# RM0380 Reference manual

STLUX and STNRG digital controllers designed for lighting and power conversion

## Introduction

This reference manual provides complete information for application developers on how to use the STLUX and STNRG family of digital controllers.

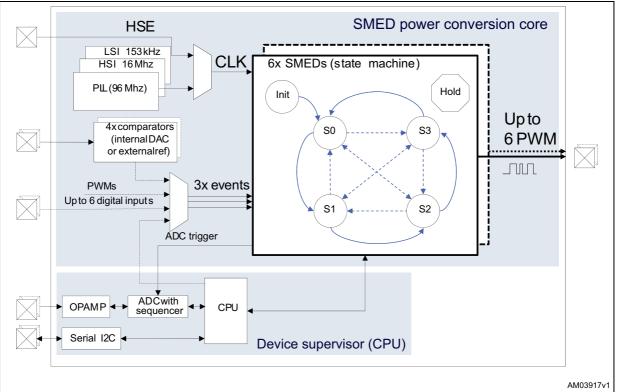

The STLUX<sup>™</sup> family of controllers is a part of the STMicroelectronics<sup>®</sup> digital devices tailored for lighting applications. The STLUX controllers have been successfully integrated in a wide range of architectures and applications, starting from simple buck converters for driving multiple LED strings, boost for power factor corrections, half-bridge resonant converters for high power dimmable LED strings and up to full bridge controllers for HID lamp ballasts. STLUX natively supports the DALI via the internal DALI communication module (DCM). DALI is a serial communication standard used in the lighting industry.

STNRG devices are a part of the STNRG family of STMicroelectronics digital devices designed for advanced power conversion applications. The STNRG improves the design of the STLUX<sup>™</sup> family to support industrial power conversion applications such as PFC+LLC, interleaved LC DC-DC, interleaved PFC for smart power supplies as well as the full bridge for pilot line drivers for electric vehicles.

The heart of the STLUX (and consequently STNRG where not differently specified) is the SMED ("State Machine, Event Driven") technology which allows the device to operate several independently configurable PWM clocks with an up to 1.3 ns resolution. An SMED is a powerful autonomous state machine which is programmed to react to both external and internal events and may evolve without any software intervention. The SMED even reaction time can be as low as 10 ns, giving the STLUX the ability of operating in time critical applications.

The SMEDs are configured and programmed via the STLUX internal low-power microcontroller (STM8). The STM8 controller extends the STLUX reliability and guarantees more than 15 years of both operating lifetime and memory data retention to the program and data memory after cycling. The STM8 device also provides powerful processing while maintaining the advantages of the CISC architecture, a 24-bit linear addressing mode, an 8-bit data bus and an optimized architecture for low power applications.

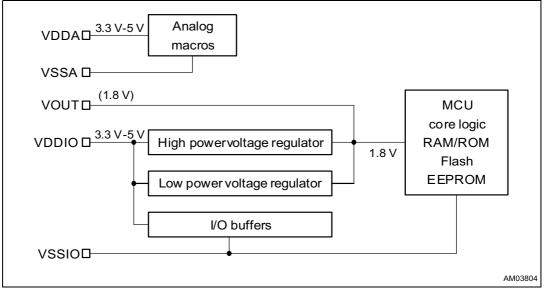

The STLUX controller 1.8 V core voltage is provided by an internal power supply DC regulator in order to simplify and reduce the application design and cost.

The STLUX device has an embedded low power, low voltage, single voltage Flash program memory designed for reliability. The same technology provides an embedded true RWW data EEPROM dedicated area and dedicated 128 byte data used for the IC configuration.

This manual describes how to program the SMED and the STM8 companion controller.

Refer to the product datasheets for ordering information, pin description, mechanical and electrical device characteristics, and for specific peripherals and implementation details.

## Contents

| 1 | Refer | ence do   | ocuments                     |

|---|-------|-----------|------------------------------|

| 2 | Acror | nyms      |                              |

| 3 | Regis | ster moo  | del                          |

| 4 | Desci | ription . |                              |

|   | 4.1   | STLUX     | STNRG feature comparison 25  |

| 5 | Centr | al proc   | essing unit (CPU)            |

|   | 5.1   |           | roduction                    |

|   | 5.2   |           | chitecture overview          |

|   | 0.2   | 5.2.1     | Architecture and registers   |

|   |       | 5.2.2     | Addressing mode              |

|   |       | 5.2.3     | Instruction set              |

|   | 5.3   | CPU re    | gisters description          |

|   |       | 5.3.1     | Accumulator (A)              |

|   |       | 5.3.2     | Index registers (X and Y)    |

|   |       | 5.3.3     | Program counter (PC)         |

|   |       | 5.3.4     | Stack pointer (SP)           |

|   |       | 5.3.5     | Condition code register (CC) |

|   | 5.4   | Core re   | gisters description          |

|   |       | 5.4.1     | A (accumulator)              |

|   |       | 5.4.2     | PCE (program counter)        |

|   |       | 5.4.3     | PCH (program counter)        |

|   |       | 5.4.4     | PCL (program counter)        |

|   |       | 5.4.5     | XH (X-index)                 |

|   |       | 5.4.6     | XL (X-index)                 |

|   |       | 5.4.7     | YH (Y-index)                 |

|   |       | 5.4.8     | YL (Y-index)                 |

|   |       | 5.4.9     | SPH (stack pointer)          |

|   |       | 5.4.10    | SPL (stack pointer)          |

|   |       | 5.4.11    | CC (code condition)          |

|   | 5.5   | CPU re    | gister map                   |

DocID026249 Rev 1

|   | 5.6   | Global o | configuration register description (CFG_GCR) | 34   |

|---|-------|----------|----------------------------------------------|------|

|   |       | 5.6.1    | SWIM disable                                 | . 34 |

|   |       | 5.6.2    | Global configuration descriptions            | . 34 |

| 6 | Debu  | g archit | ecture                                       | 36   |

|   | 6.1   | Introduc | tion                                         | 36   |

|   | 6.2   | Single v | vire interface module (SWIM)                 | 36   |

|   | 6.3   | SWIM n   | nain features                                | 37   |

|   | 6.4   | SWIM r   | egister description                          | 37   |

|   |       | SWIM_C   | SR (SWIM control register)                   | . 37 |

|   | 6.5   | SWIM r   | egister map                                  | 38   |

|   | 6.6   | Debug r  | nodule                                       | 38   |

|   | 6.7   | DM mai   | n features                                   | 38   |

|   | 6.8   | Internal | registers description                        | 39   |

|   |       | 6.8.1    | DM_BK1E (DM breakpoint 1 ext. byte)          | . 39 |

|   |       | 6.8.2    | DM_BK1H (DM breakpoint 1 high byte)          | . 39 |

|   |       | 6.8.3    | DM_BK1L (DM breakpoint 1 low byte)           | . 39 |

|   |       | 6.8.4    | DM_BK2E (DM breakpoint 2 ext. byte)          | . 39 |

|   |       | 6.8.5    | DM_BK2H (DM breakpoint 2 high byte)          | . 40 |

|   |       | 6.8.6    | DM_BK2L (DM breakpoint 2 low byte)           | . 40 |

|   |       | 6.8.7    | DM_CR (DM control register)                  | . 40 |

|   |       | 6.8.8    | DM_CR2 (DM control register 2)               |      |

|   |       | 6.8.9    | DM_CSR (DM status/control register 1)        |      |

|   |       | 6.8.10   | DM_CSR2 (DM status/control register 2)       |      |

|   |       | 6.8.11   | DM_ENFCT (DM enable function register)       |      |

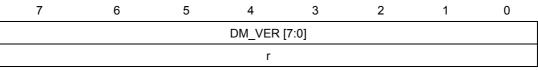

|   |       | 6.8.12   | DM_VER (DM version register)                 |      |

|   | 6.9   | Internal | registers overview                           | 45   |

| 7 | Boot  | ROM      |                                              | 46   |

| 8 | Memo  | ory and  | register map                                 | 47   |

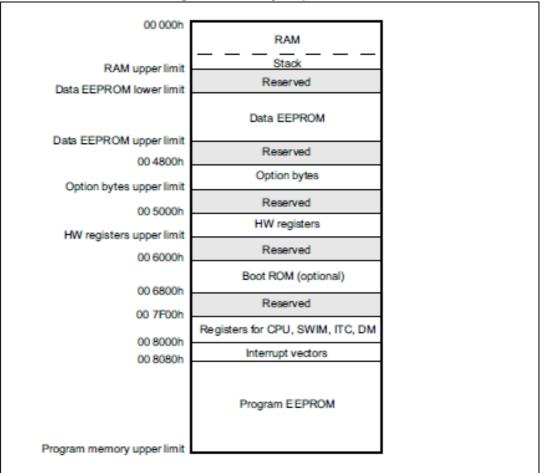

|   | 8.1   | Memory   | layout                                       | 47   |

|   |       | 8.1.1    | Memory map                                   | . 47 |

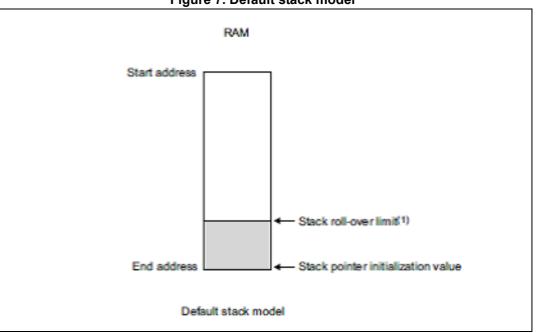

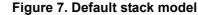

|   |       | 8.1.2    | Stack handling                               | . 48 |

| 9 | Flash | progra   | m memory and data EEPROM                     | 50   |

| 9.1  | Main F    | lash memory features                            | 50 |

|------|-----------|-------------------------------------------------|----|

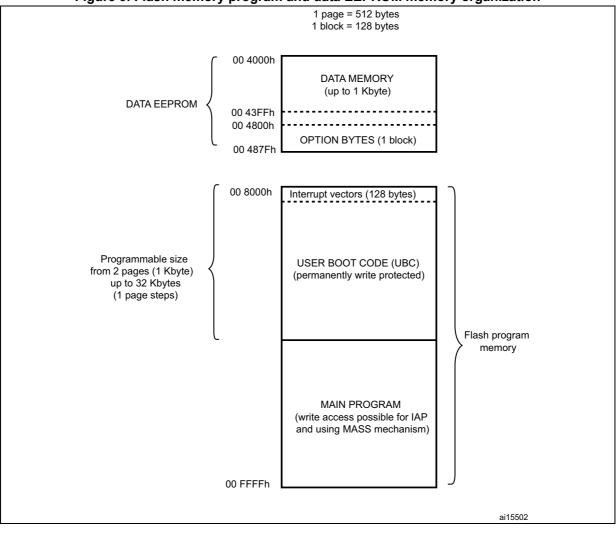

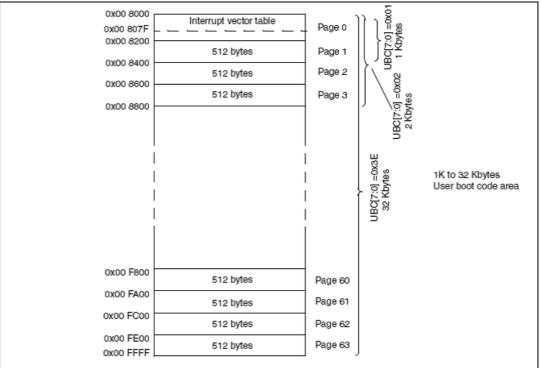

| 9.2  | Flash r   | memory organization                             | 51 |

|      | 9.2.1     | Memory access / wait state configuration        | 52 |

|      | 9.2.2     | Program memory                                  | 52 |

|      | 9.2.3     | Data memory                                     | 53 |

|      | 9.2.4     | Option byte memory                              | 53 |

| 9.3  | Memor     | y protection mechanism                          | 53 |

|      | 9.3.1     | Readout protection (ROP)                        | 53 |

|      | 9.3.2     | Memory access security system (MASS)            | 53 |

| 9.4  | Memor     | ry programming                                  | 55 |

|      | 9.4.1     | Read-while-write (RWW)                          | 55 |

|      | 9.4.2     | Programming modes                               | 55 |

| 9.5  | ICP an    | d IAP                                           | 58 |

| 9.6  | Flash r   | egisters description                            | 60 |

|      | 9.6.1     | FLASH_CR1 (Flash control register1)             | 60 |

|      | 9.6.2     | FLASH_CR2 (Flash control register2)             | 60 |

|      | 9.6.3     | FLASH_nCR2 (Flash control register2 protection) | 61 |

|      | 9.6.4     | FLASH_FPR (Flash write page protection)         | 61 |

|      | 9.6.5     | FLASH_nFPRP (FLASH_FPR protection)              | 62 |

|      | 9.6.6     | FLASH_IAPSR (Flash status register)             | 62 |

|      | 9.6.7     | FLASH_PUKR (Flash program memory unprotection)  | 63 |

|      | 9.6.8     | FLASH_DUKR (Flash data memory unprotection)     | 63 |

|      | 9.6.9     | FLASH_WAIT (Flash wait state register)          | 64 |

| 9.7  | Flash r   | egisters overview                               | 65 |

| Pow  | er supp   | ly                                              | 66 |

| Rese | et contro | ol unit (RST)                                   | 67 |

| 11.1 | Reset     | state and reset in progress definition          | 67 |

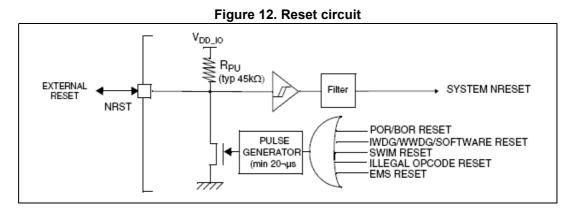

| 11.2 | Reset     | circuit description                             | 67 |

| 11.3 | Interna   | Il reset sources                                | 68 |

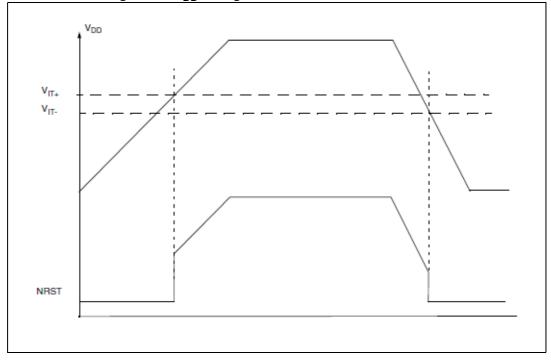

|      | 11.3.1    | Power-on reset (POR) and brownout reset (BOR)   | 68 |

|      | 11.3.2    | Watchdog reset                                  | 69 |

|      | 11.3.3    | Software reset                                  | 69 |

|      | 11.3.4    | SWIM reset                                      | 69 |

|      | 11.3.5    | Illegal opcode reset                            | 69 |

10

11

|    |       | 11.3.6 EMC reset                                           | )        |

|----|-------|------------------------------------------------------------|----------|

|    | 11.4  | RST register description 69                                | )        |

|    |       | RST_SR (status register)69                                 | )        |

|    | 11.5  | RST register overview                                      | )        |

| 12 | Clock | control unit (CKC)                                         |          |

|    | 12.1  | EMS - hardened clock configuration registers (optional) 71 |          |

|    | 12.2  | Features overview                                          |          |

|    | 12.3  | Master clock sources                                       | ]        |

|    |       | 12.3.1 HSI                                                 | >        |

|    |       | 12.3.2 LSI                                                 | 2        |

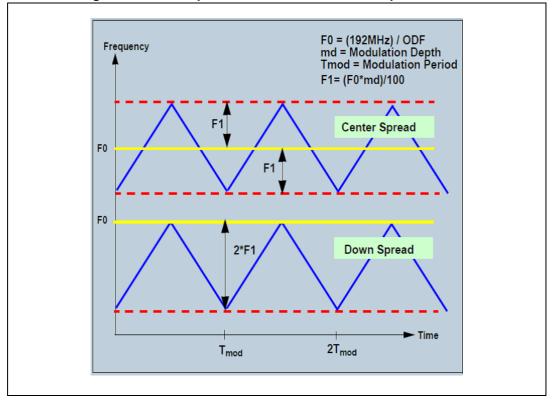

|    |       | 12.3.3 PLL                                                 | }        |

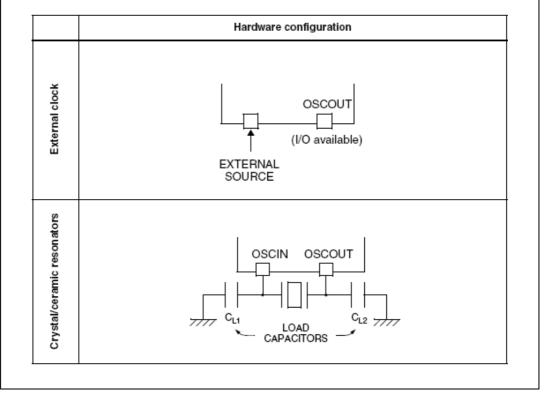

|    |       | 12.3.4 HSE                                                 | ŀ        |

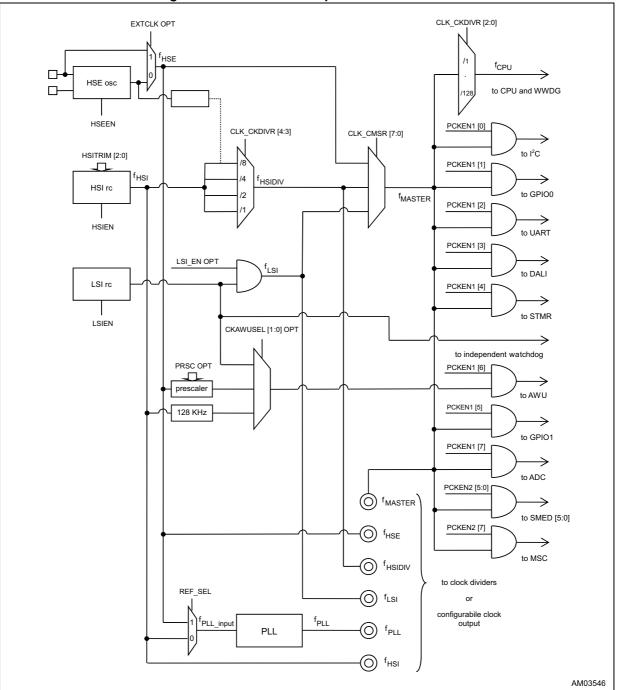

|    |       | 12.3.5 Internal clock scheme                               | 5        |

|    | 12.4  | Oscillators control                                        | '        |

|    |       | 12.4.1 Oscillator enable control logic                     | ,        |

|    |       | 12.4.2 Oscillator startup                                  | '        |

|    | 12.5  | Master clock switch                                        | ,        |

|    |       | 12.5.1 Switch trigger                                      | ,        |

|    |       | 12.5.2 CPU clock during switch                             | 3        |

|    |       | 12.5.3 Glitch filter                                       |          |

|    |       | 12.5.4 SWBSY utility                                       | 3        |

|    |       | 12.5.5 Switch enable                                       |          |

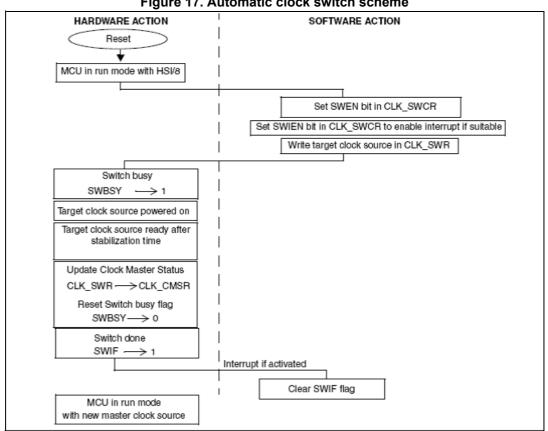

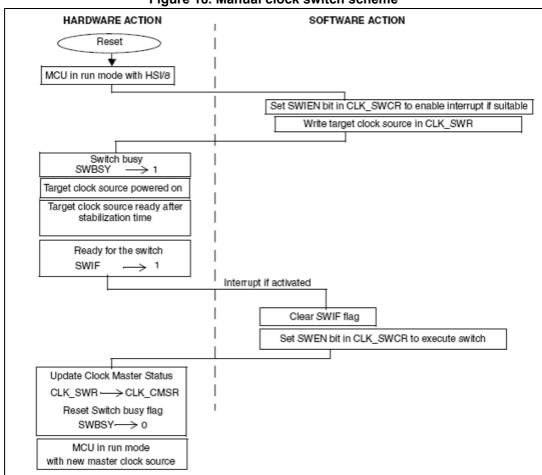

|    |       | 12.5.6 Automatic vs. manual switch                         |          |

|    |       | 12.5.7 Interrupts/flags for application                    |          |

|    |       | 12.5.8 Old CKM after switch                                |          |

|    |       | 12.5.9 Wait mode synchronization                           |          |

|    | 12.6  | Peripheral clock gating 81                                 | I        |

|    | 12.7  | Clock dividers                                             | <u>}</u> |

|    |       | 12.7.1 PLL clock divider                                   |          |

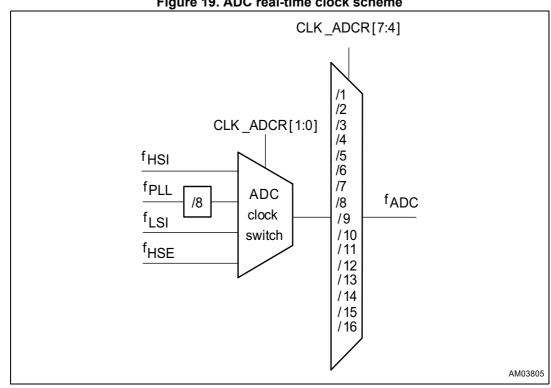

|    |       | 12.7.2 ADC real-time clock divider 82                      |          |

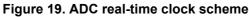

|    |       | 12.7.3 SMED real-time clock dividers                       |          |

|    | 12.8  | Clock security system (CSS) 84                             | ŀ        |

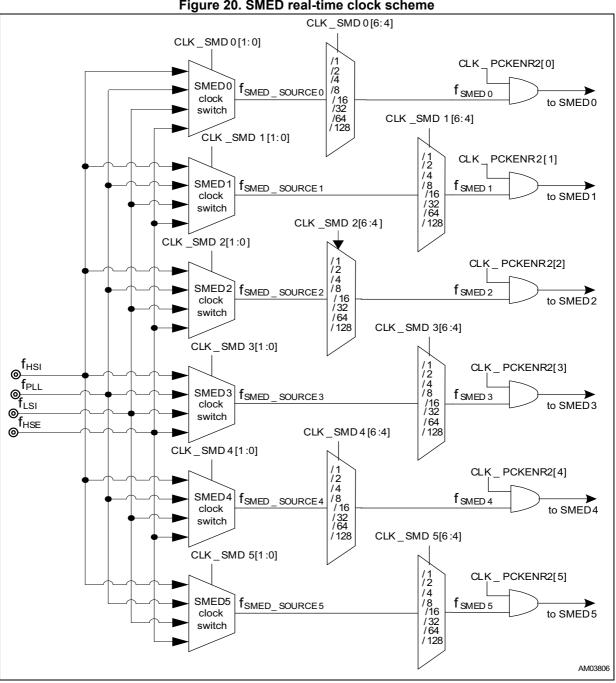

|    | 12.9  | Configurable clock output 85                               | ;        |

|    | 12.10 | CLK interrupts                                             | ,        |

|    | 12.11 | Clock registers description                                | ,        |

|    |       |                                                            |          |

|       | 12.11.1  | CLK_SMD0 (SMED0 clock configuration)            | 87    |

|-------|----------|-------------------------------------------------|-------|

|       | 12.11.2  | CLK_SMD1 (SMED1 clock configuration)            | 88    |

|       | 12.11.3  | CLK_SMD2 (SMED2 clock configuration)            | 88    |

|       | 12.11.4  | CLK_SMD3 (SMED3 clock configuration)            | 89    |

|       | 12.11.5  | CLK_SMD4 (SMED4 clock configuration)            | 90    |

|       | 12.11.6  | CLK_SMD5 (SMED5 clock configuration)            | 90    |

|       | 12.11.7  | CLK_PLLDIVR (PLL prescaler configuration)       | 91    |

|       | 12.11.8  | CLK_AWUDIVR (AWU clock prescaler configuration) | 92    |

|       | 12.11.9  | CLK_ICKR (internal clocks control)              | 92    |

|       | 12.11.10 | CLK_ECKR (external clocks control)              | 94    |

|       | 12.11.11 | CLK_PLLR (PLL configuration)                    | 94    |

|       | 12.11.12 | CLK_CMSR (clock master)                         | 95    |

|       | 12.11.13 | CLK_SWR (clock switch)                          | 96    |

|       | 12.11.14 | CLK_SWCR (switch control)                       | 97    |

|       | 12.11.15 | CLK_CKDIVR (clock dividers)                     | 98    |

|       | 12.11.16 | CLK_PCKENR1 (peripherals clock enable)          | 99    |

|       | 12.11.17 | CLK_CSSR (clock security system)                | . 100 |

|       | 12.11.18 | CLK_CCOR (configurable clock output)            | . 101 |

|       | 12.11.19 | CLK_PCKENR2 (peripherals clock enable)          | . 103 |

|       | 12.11.20 | CLK_HSITRIMR (HSI calibration trimmer)          | . 104 |

|       | 12.11.21 | CLK_SWIMCCR (SWIM clock division)               | . 104 |

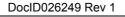

|       | 12.11.22 | CLK_CCODIVR (CCO divider)                       | . 104 |

|       | 12.11.23 | CLK_ADCR (ADC clock configuration)              | . 105 |

| 12.12 | Clock re | egisters overview                               | 106   |

| owe   | r mana   | gement (PM)                                     | 107   |

| 13.1  | Overvie  | w                                               | 107   |

| 13.2  | Clock s  | witching reduction                              | 107   |

|       | 13.2.1   | Peripheral clock gating                         |       |

|       | 13.2.2   | Slow down clock                                 |       |

|       | 13.2.3   | Analog peripherals power-down                   |       |

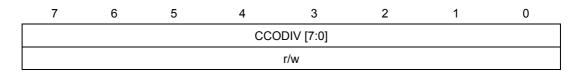

| 3.3   |          | ng modes                                        |       |

|       | 13.3.1   | RUN mode                                        |       |

|       | 13.3.2   | WAIT mode                                       |       |

|       | 13.3.3   | Active-halt mode                                |       |

|       | 13.3.4   | Halt mode                                       |       |

|       |          |                                                 |       |

13

| 14 | Interr | upt con   | troller (ITC) 113                                                   |

|----|--------|-----------|---------------------------------------------------------------------|

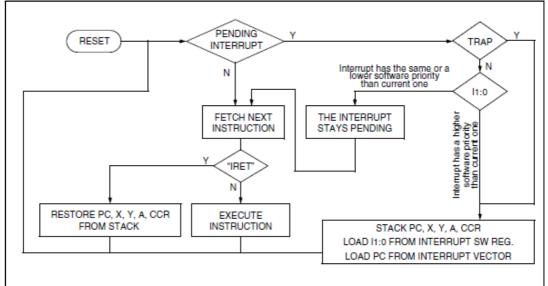

|    | 14.1   | Functio   | nal overview                                                        |

|    | 14.2   | Interrup  | t masking and processing flow113                                    |

|    | 14.3   | Interrup  | t priority                                                          |

|    | 14.4   | Servicir  | ng pending interrupts                                               |

|    | 14.5   | Interrup  | t sources                                                           |

|    |        | 14.5.1    | Not-maskable interrupt sources                                      |

|    |        | 14.5.2    | Maskable interrupt sources 117                                      |

|    | 14.6   | Interrup  | ts and low power modes117                                           |

|    | 14.7   | Activatio | on level/low power mode control                                     |

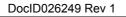

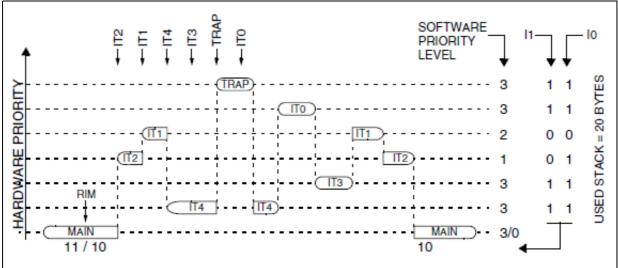

|    | 14.8   | Concur    | rent and nested interrupt management                                |

|    |        | 14.8.1    | Concurrent interrupt management mode                                |

|    |        | 14.8.2    | Nested interrupt management mode                                    |

|    | 14.9   | Externa   | l interrupts                                                        |

|    |        | 14.9.1    | Interrupt on port 3 (comparators) 121                               |

|    |        | 14.9.2    | Interrupt polling mode121                                           |

|    |        | 14.9.3    | Auxiliary/basic timers interrupt functionality                      |

|    |        | 14.9.4    | Edge detector configuration                                         |

|    | 14.10  | Interrup  | t instructions                                                      |

|    | 14.11  | Interrup  | t controller registers description 124                              |

|    |        | 14.11.1   | ITC_SPR0 (interrupt SW priority 0) 124                              |

|    |        | 14.11.2   | ITC_SPR1 (interrupt SW priority 1) 125                              |

|    |        | 14.11.3   | ITC_SPR2 (interrupt SW priority 2) 125                              |

|    |        | 14.11.4   | ITC_SPR3 (interrupt SW priority 3) 125                              |

|    |        | 14.11.5   | ITC_SPR4 (interrupt SW priority 4) 126                              |

|    |        | 14.11.6   | ITC_SPR5 (interrupt SW priority 5) 126                              |

|    |        | 14.11.7   | ITC_SPR6 (interrupt SW priority 6) 126                              |

|    |        | 14.11.8   | ITC_SPR7 (interrupt SW priority 7) 127                              |

|    | 14.12  | Miscella  | aneous interrupt registers 127                                      |

|    |        | 14.12.1   | MSC_CFGP <xy> (port P<x>[<y>] input control register)</y></x></xy>  |

|    |        | 14.12.2   | $MSC\_STSP (port P interrupt status reg.;  = 0, 1, 2, 3) \dots 128$ |

|    |        | 14.12.3   | MSC_INPP2AUX1 (INPP2 aux. register1)                                |

|    |        | 14.12.4   | MSC_INPP2AUX2 (INPP2 aux. register2)130                             |

|    |        | 14.12.5   | MSC_INPP2 (Port2 input data register) 130                           |

|    | 14.13  | Interrup  | t controller registers overview 131                                 |

|    | 14.14 | Miscellaneous interrupt registers overview                       |

|----|-------|------------------------------------------------------------------|

|    | 14.15 | Interrupt exception vector table 132                             |

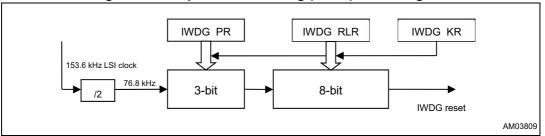

| 15 | Indep | endent watchdog (IWDG) 133                                       |

|    | 15.1  | IWDG introduction                                                |

|    | 15.2  | IWDG functional description                                      |

|    |       | 15.2.1 IWDG HW feature                                           |

|    |       | 15.2.2 IWDG timeout period                                       |

|    | 15.3  | IWDG program sequence                                            |

|    | 15.4  | IWDG and AWU concurrent activation                               |

|    | 15.5  | Independent watchdog registers description                       |

|    |       | 15.5.1 IWDG_KR (key register)                                    |

|    |       | 15.5.2 IWDG_PR (prescaler register)                              |

|    |       | 15.5.3 IWDG_RLR (reload counter)                                 |

|    | 15.6  | Watchdog registers overview 137                                  |

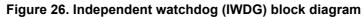

| 16 | Wind  | ow watchdog (WWDG) 138                                           |

|    | 16.1  | WWDG introduction                                                |

|    | 16.2  | WWDG main features 138                                           |

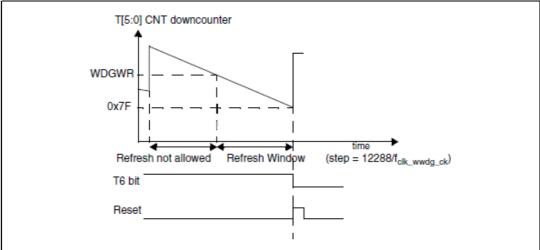

|    | 16.3  | WWDG functional description                                      |

|    | 16.4  | Watchdog reset on Halt option                                    |

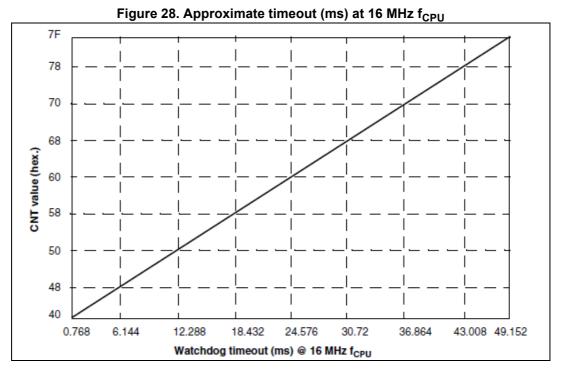

|    | 16.5  | How to program the watchdog timeout 140                          |

|    | 16.6  | WWDG low power modes                                             |

|    |       | 16.6.1 Hardware watchdog option                                  |

|    |       | 16.6.2 Using Halt mode with the WWDG (WWDG_HALT option byte) 141 |

|    | 16.7  | Window watchdog registers description                            |

|    |       | 16.7.1 WWDG_ CR (control register) 141                           |

|    |       | 16.7.2 WWDG_WR (window register)                                 |

|    | 16.8  | Window watchdog registers overview                               |

| 17 | Auto- | wakeup unit (AWU)143                                             |

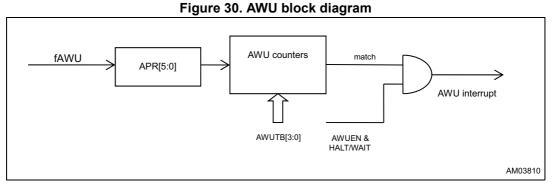

|    | 17.1  | AWU functional description 143                                   |

|    | 17.2  | Time base selection                                              |

|    | 17.3  | Interval time formulas                                           |

|    | 17.4  | AWU program sequence                                             |

|    | 17.5   | Auto wake unit registers description 14       | 45        |

|----|--------|-----------------------------------------------|-----------|

|    |        | 17.5.1 AWU_CSR (control status register)14    | 45        |

|    |        | 17.5.2 AWU_APR (prescaler divider register)14 | 46        |

|    |        | 17.5.3 AWU_TBR (time base register)14         | 47        |

|    | 17.6   | Auto wake unit registers overview 14          | 47        |

| 18 | Syste  | em timer (STMR)                               | 18        |

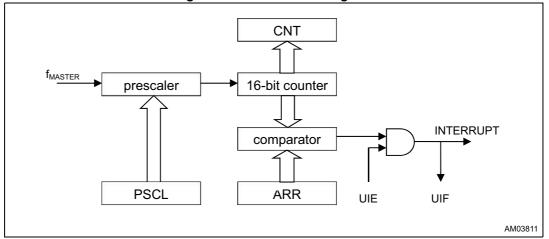

|    | 18.1   | STMR introduction 14                          | 48        |

|    | 18.2   | STMR main features 14                         | 48        |

|    | 18.3   | STMR timer overview 14                        | 48        |

|    | 18.4   | Configuration of the 16-bit counter 14        | 49        |

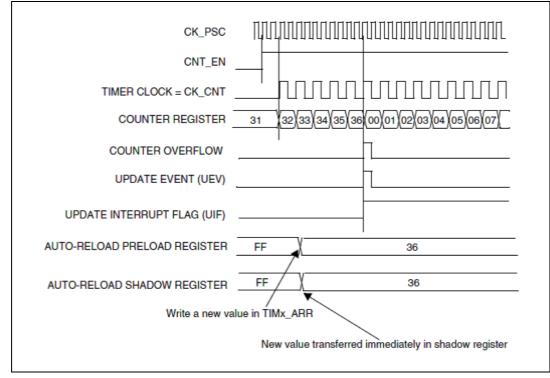

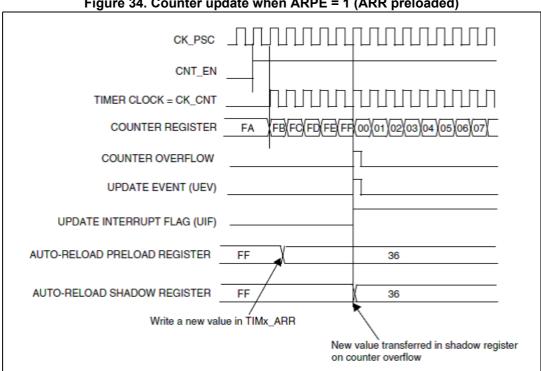

|    | 18.5   | Write sequence for 16-bit STMR_ARR register   | 50        |

|    | 18.6   | Prescaler                                     | 50        |

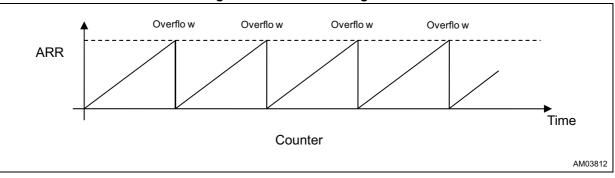

|    | 18.7   | STMR counting mode 15                         | 50        |

|    | 18.8   | STMR program sequence 15                      | 52        |

|    | 18.9   | STMR interrupts                               | 52        |

|    | 18.10  | System timer as ADC trigger source            | 53        |

|    | 18.11  | System timer unit registers description       | 53        |

|    |        | 18.11.1 STMR_CR1 (control register)1          | 53        |

|    |        | 18.11.2 STMR_IER (interrupt enable register)1 | 54        |

|    |        | 18.11.3 STMR_SR1 (status register 1) 1        | 54        |

|    |        | 18.11.4 STMR_EGR (event generation register)  | 55        |

|    |        | 18.11.5 STMR_CNTH (counter high register)     |           |

|    |        | 18.11.6 STMR_CNTL (counter low register)      |           |

|    |        | 18.11.7 STMR_PSCL (prescaler register)        |           |

|    |        | 18.11.8 STMR_ARRH (auto-reload high register) |           |

|    | 40.40  | 18.11.9 STMR_ARRL (auto-reload low register)  |           |

|    | 18.12  | System timer unit registers overview          | <i>э1</i> |

| 19 | Auxili | iary timer                                    | 58        |

|    | 19.1   | Auxiliary timer introduction 15               | 58        |

|    | 19.2   | Auxiliary timer main features                 | 58        |

|    | 19.3   | Auxiliary timer functional description        | 58        |

|    | 19.4   | Program sequence                              | 59        |

|    | 19.5   | Auxiliary timer unit register overview        | 59        |

| 20 | Basic | timer .   |                                                    | 160   |

|----|-------|-----------|----------------------------------------------------|-------|

|    | 20.1  | Basic tin | ner introduction                                   | 160   |

|    | 20.2  | Basic tin | ner main features                                  | 160   |

|    | 20.3  | Basic tin | ner functional description                         | 160   |

|    | 20.4  | Program   | iming sequence                                     | 161   |

|    | 20.5  | •         | ner control registers                              |       |

|    |       | 20.5.1    | MSC FTM0CKSEL (BscTim10 clock selection)           |       |

|    |       | 20.5.2    | MSC_FTM0CKDIV (BscTim0 clock division factor)      | . 162 |

|    |       | 20.5.3    | MSC_FTM0CONF (BscTim0 counter)                     | . 163 |

|    |       | 20.5.4    | MSC_FTM1CKDIV (BscTim1 clock division factor)      | . 163 |

|    |       | 20.5.5    | MSC_FTM1CONF (BscTim0 counter)                     | . 163 |

|    | 20.6  | Addition  | al basic timer register overview                   | 164   |

|    | -     |           |                                                    |       |

| 21 |       |           | e, event driven (SMED)                             |       |

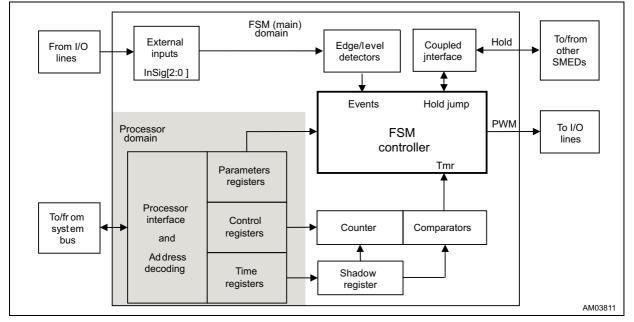

|    | 21.1  | SMED a    | rchitecture overview                               | 165   |

|    | 21.2  | SMED n    | nain features                                      | 166   |

|    | 21.3  | Block dia | agram                                              | 167   |

|    |       | 21.3.1    | Subblocks descriptions                             | . 167 |

|    |       | 21.3.2    | Clock domains                                      | . 167 |

|    | 21.4  | Process   | or interface                                       | 168   |

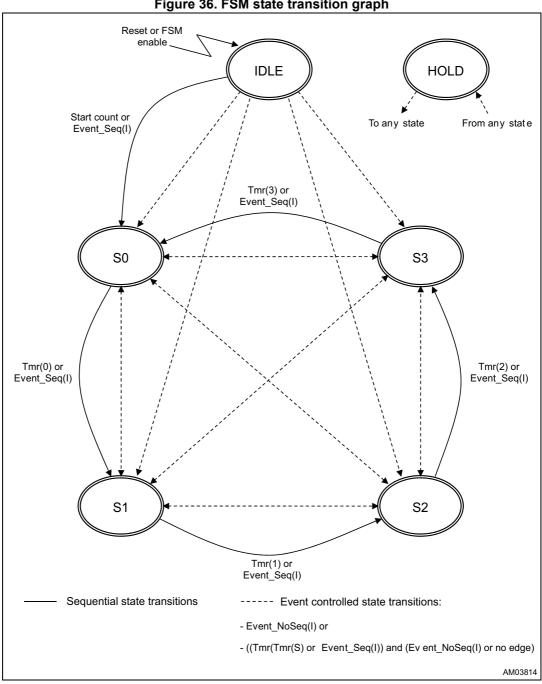

|    | 21.5  | FSM co    | ntroller                                           | 168   |

|    | 21.6  | External  | events                                             | 169   |

|    |       | 21.6.1    | Level/edge detection logic                         | . 169 |

|    |       | 21.6.2    | External event handling                            | . 169 |

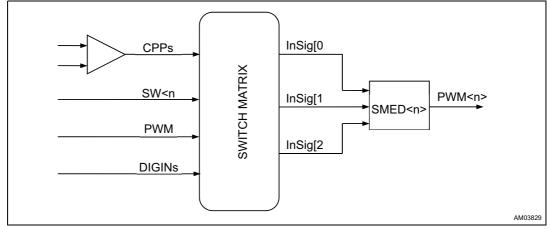

|    |       | 21.6.3    | External input multiplexing                        | . 170 |

|    | 21.7  | Internal  | events                                             | 170   |

|    | 21.8  | Events p  | priority                                           | 171   |

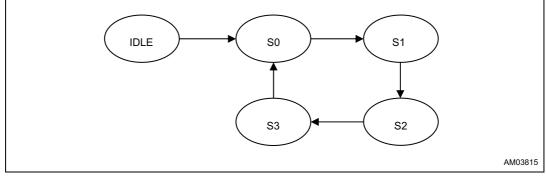

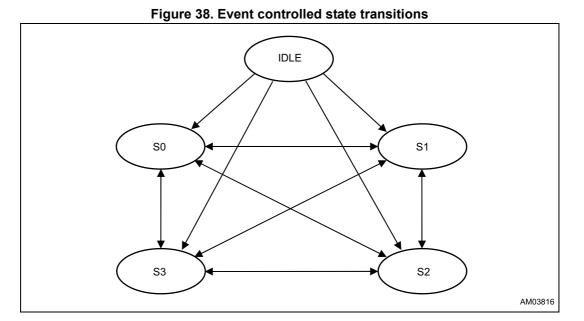

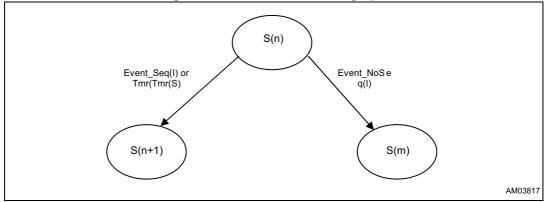

|    | 21.9  | State tra | nsition                                            | 171   |

|    |       | 21.9.1    | IDLE state                                         | . 174 |

|    |       | 21.9.2    | HOLD state                                         | . 174 |

|    |       | 21.9.3    | Sequential state transitions (S0 $\rightarrow$ S3) | . 174 |

|    |       | 21.9.4    | Non-sequential state transitions                   | . 175 |

|    |       | 21.9.5    | State evolution equations                          | . 176 |

|    | 21.10 | State tra | nsition occurrence                                 | 178   |

|    |       | 21.10.1   | Output PWM level                                   | . 179 |

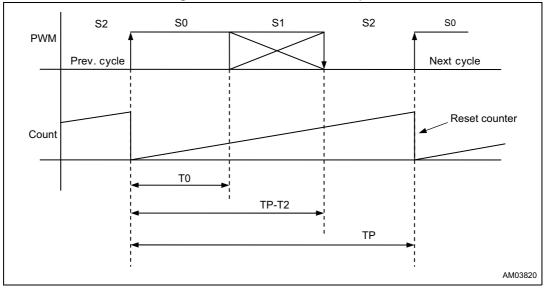

|       | 21.10.2          | Counter reset                                  | 179 |

|-------|------------------|------------------------------------------------|-----|

|       | 21.10.3          | Hold jump                                      | 180 |

|       | 21.10.4          | Hold exit                                      | 181 |

| 21.11 | Time co          | ntrol                                          | 182 |

|       | 21.11.1          | State timer registers                          | 182 |

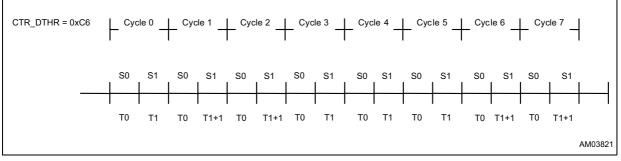

|       | 21.11.2          | Dithering                                      | 183 |

|       | 21.11.3          | Time stamp functionality                       | 185 |

| 21.12 | Interrup         | t functionality                                | 186 |

| 21.13 | Status ir        | nformation                                     | 187 |

|       | 21.13.1          | GSTS (global status register)                  | 187 |

|       | 21.13.2          | FSM_STS (finite state machine status register) | 187 |

| 21.14 | PWM re           | eset output value                              | 188 |

| 21.15 | PWM pa           | ad (pseudo) open drain configuration           | 188 |

| 21.16 | SMED a           | as ADC trigger source                          | 188 |

| 21.17 | SMED o           | coupled expansion interface                    | 189 |

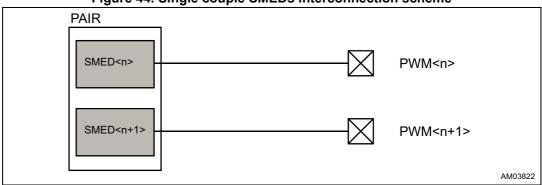

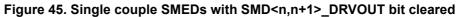

|       | 21.17.1          | SMED coupled interface configuration scheme    | 189 |

|       | 21.17.2          | Chapter assumptions:                           | 190 |

|       | 21.17.3          | SMED subsystem configuration                   | 190 |

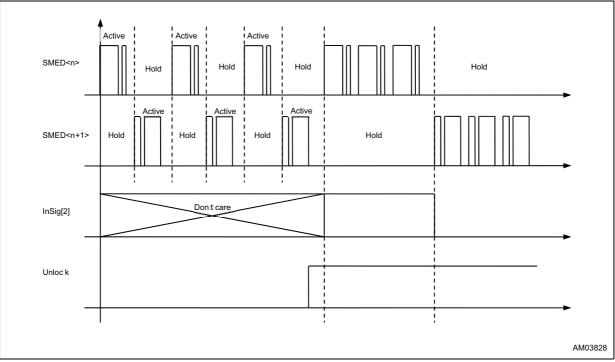

|       | 21.17.4          | Unlock feature                                 | 196 |

|       | 21.17.5          | Connection box                                 | 197 |

|       | 21.17.6          | FSM diagnostic trace                           | 199 |

| 21.18 | SMED r           | egisters description                           | 199 |

|       | 21.18.1          | SMED core registers                            | 199 |

|       | 21.18.2          | SMED environment configuration registers       | 215 |

| Cono  |                  | esse I/O mort (CBIO)                           | 224 |

|       |                  | ose I/O port (GPIO)                            |     |

| 22.1  |                  | nain features                                  |     |

| 22.2  |                  | nfiguration and usage                          |     |

|       | 22.2.1           | Input modes                                    |     |

|       | 22.2.2           | Output modes                                   |     |

|       | 22.2.3           | Slope control                                  |     |

|       | 22.2.4<br>22.2.5 | Reset configuration                            |     |

|       | 22.2.5           | Unused I/O pins                                |     |

| 22.3  |                  | e output function                              |     |

| -     |                  | •                                              |     |

| 22.4  | merrup           | t functionality                                | 223 |

22

|    | 22.5   | Interrup               | t masking                                                                                                   | 223   |

|----|--------|------------------------|-------------------------------------------------------------------------------------------------------------|-------|

|    | 22.6   | GPIO re                | egisters description                                                                                        | 224   |

|    |        | 22.6.1                 | P <n>_ODR (port output data register)</n>                                                                   | . 224 |

|    |        | 22.6.2                 | P <n>_IDR (port input data register)</n>                                                                    | . 224 |

|    |        | 22.6.3                 | P <n>_DDR (port data direction register)</n>                                                                | . 225 |

|    |        | 22.6.4                 | P <n>_CR1 (port control register1)</n>                                                                      | . 225 |

|    |        | 22.6.5                 | P <n>_CR2 (port control register2)</n>                                                                      | . 226 |

|    | 22.7   | GPIO re                | egisters overview                                                                                           | 227   |

| 23 | Inter- | integrat               | ted circuit interface (I <sup>2</sup> C)                                                                    | 228   |

|    | 23.1   | I <sup>2</sup> C intro | oduction                                                                                                    | 228   |

|    | 23.2   | I <sup>2</sup> C mai   | n features                                                                                                  | 228   |

|    | 23.3   | I <sup>2</sup> C sigr  | nal interface                                                                                               | 229   |

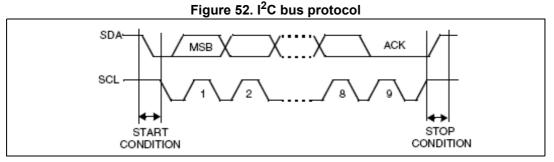

|    | 23.4   | I <sup>2</sup> C gen   | eral description                                                                                            | 229   |

|    | 23.5   | Commu                  | inication flow                                                                                              | 229   |

|    | 23.6   | I <sup>2</sup> C fund  | ctional description                                                                                         | 230   |

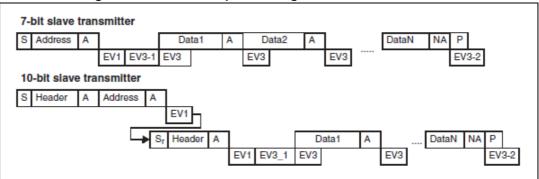

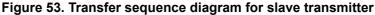

|    |        | 23.6.1                 | I <sup>2</sup> C slave mode                                                                                 |       |

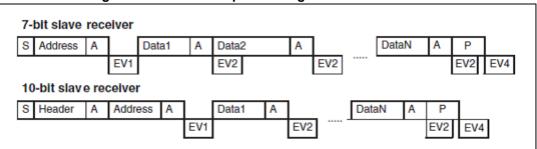

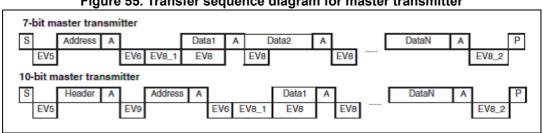

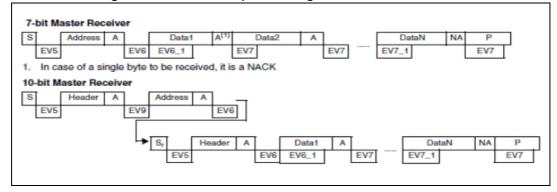

|    |        | 23.6.2                 | I <sup>2</sup> C master mode                                                                                | . 233 |

|    |        | 23.6.3                 | Error conditions                                                                                            | . 241 |

|    |        | 23.6.4                 | SDA/SCL line control                                                                                        | . 242 |

|    | 23.7   | Limitatio              | ons on I <sup>2</sup> C peripheral usage                                                                    | 242   |

|    |        | 23.7.1                 | I <sup>2</sup> C event management                                                                           | . 242 |

|    |        | 23.7.2                 | Corrupted last received data in master receiver mode                                                        | . 243 |

|    |        | 23.7.3                 | Wrong behavior of I <sup>2</sup> C peripheral in master mode after misplaced STOP                           | . 243 |

|    |        | 23.7.4                 | Violation of I <sup>2</sup> C "setup time for repeated START condition" parameter                           | . 244 |

|    |        | 23.7.5                 | In I <sup>2</sup> C slave "NOSTRETCH" mode, underrun errors may not be detected and may generate bus errors | . 244 |

|    |        | 23.7.6                 | I <sup>2</sup> C pulse missed                                                                               | . 245 |

|    | 23.8   | I <sup>2</sup> C low   | power modes                                                                                                 | 246   |

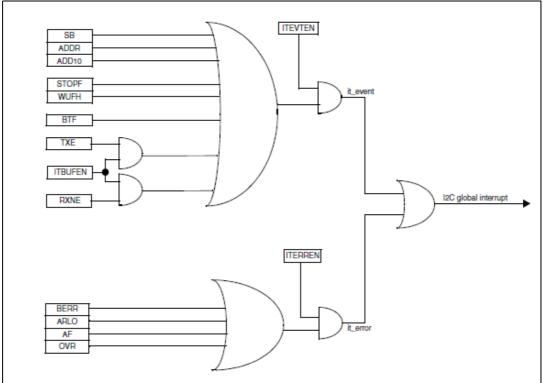

|    | 23.9   | I <sup>2</sup> C inte  | rrupts                                                                                                      | 246   |

|    | 23.10  | l <sup>2</sup> C regi  | isters description                                                                                          | 247   |

|    |        | •                      | I2C_CR1 (control register1)                                                                                 |       |

|    |        |                        | I2C_CR2 (control register2)                                                                                 |       |

|    |        | 23.10.3                | I2C_FREQR (frequency register)                                                                              | . 249 |

|    |        | 23.10.4                | I2C_OARL (own add. LSB register)                                                                            | . 250 |

|    |        |                        |                                                                                                             |       |

|    |        | 23.10.5 I2C_OARH (own add. MSB register)      |

|----|--------|-----------------------------------------------|

|    |        | 23.10.6 I2C_DR (data register) 251            |

|    |        | 23.10.7 I2C_SR1 (status register1)            |

|    |        | 23.10.8 I2C_SR2 (status register2)            |

|    |        | 23.10.9 I2C_SR3 (status register3) 255        |

|    |        | 23.10.10 I2C_ITR (interrupt register)         |

|    |        | 23.10.11 I2C_CCRL (clock control low)         |

|    |        | 23.10.12 I2C_CCRH (clock control high)        |

|    |        | 23.10.13 I2C_TRISER (time rise register)      |

|    | 23.11  | I <sup>2</sup> C registers overview           |

| 24 | Unive  | rsal asynchronous receiver transmitter (UART) |

|    | 24.1   | UART main features                            |

|    | 24.2   | UART functional description 262               |

|    |        | 24.2.1 UART character description             |

|    |        | 24.2.2 UART transmitter                       |

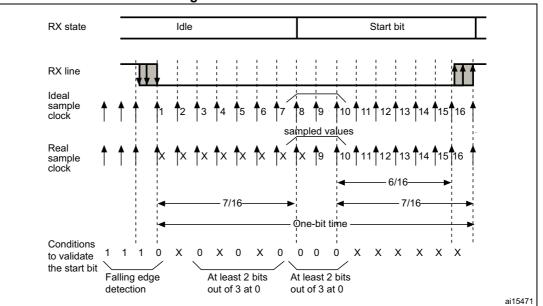

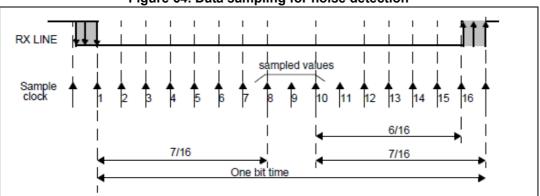

|    |        | 24.2.3 UART receiver                          |

|    |        | 24.2.4 Parity control                         |

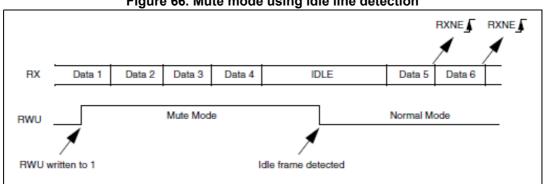

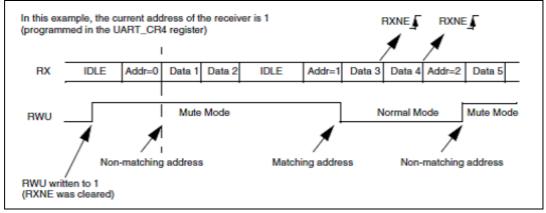

|    |        | 24.2.5 Multi-processor communication          |

|    | 24.3   | UART low power mode                           |

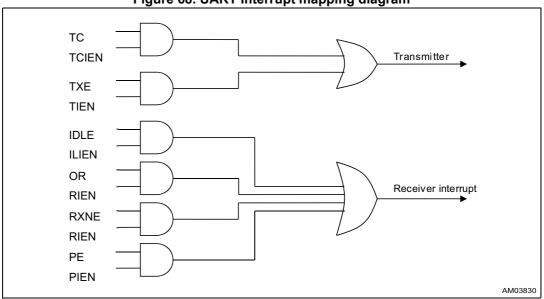

|    | 24.4   | UART interrupts                               |

|    | 24.5   | UART registers description                    |

|    |        | 24.5.1 UART_SR (status register)              |

|    |        | 24.5.2 UART_DR (data register)                |

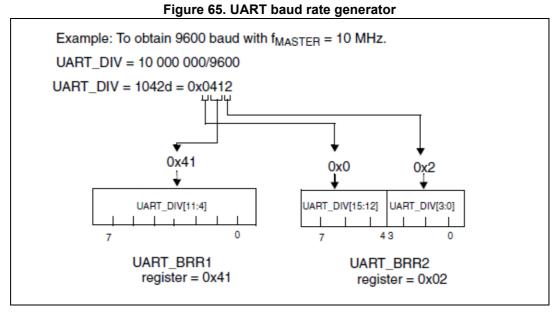

|    |        | 24.5.3 UART_BRR1 (baud rate 1 register)       |

|    |        | 24.5.4 UART_BRR2 (baud rate 2 register)       |

|    |        | 24.5.5 UART_CR1 (control register 1)          |

|    |        | 24.5.6 UART_CR2 (control register 2)          |

|    |        | 24.5.7 UART_CR3 (control register 3)          |

|    |        | 24.5.8 UART_CR4 (control register 4)          |

|    | 24.6   | UART registers overview                       |

| 25 | Digita | Il addressable lighting interface (DALI)      |

|    | 25.1   | DALI main features                            |

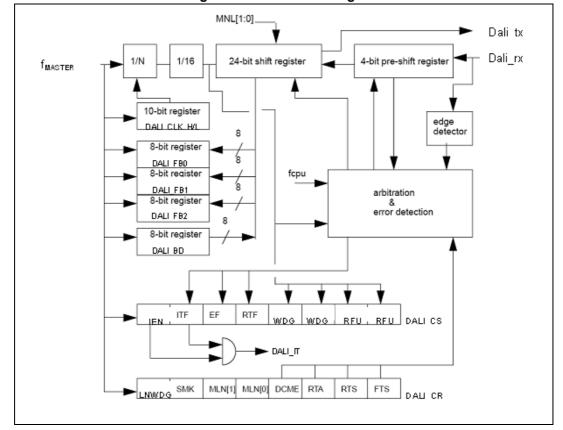

|    | 25.2   | DALI block diagram                            |

|    | 25.3   | DALI functional overview                      |

|    |        |                                               |

| 25.4  | Monitor   | receiver line                                     | 285 |

|-------|-----------|---------------------------------------------------|-----|

| 25.5  | DALI sig  | gnal interface                                    | 285 |

|       | 25.5.1    | Polarity configurable signal interface            | 285 |

|       | 25.5.2    | Start bit handling                                | 285 |

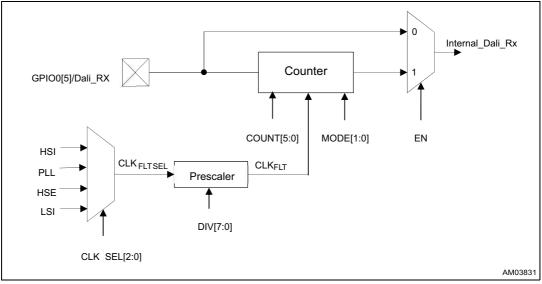

|       | 25.5.3    | Digital noise rejection filter                    | 285 |

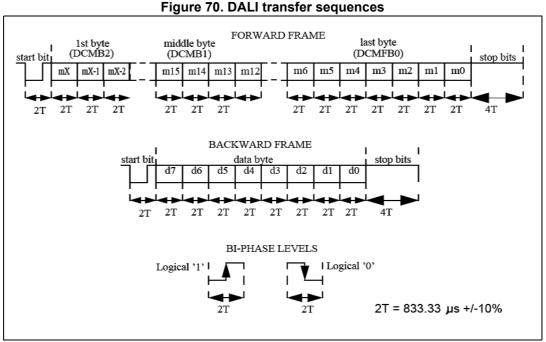

| 25.6  | DALI da   | ata rate                                          | 288 |

| 25.7  | DALI Io   | w power mode                                      | 288 |

| 25.8  | DALI int  | terrupts                                          | 289 |

| 25.9  | DALI pr   | ogramming sequences                               | 289 |

|       | 25.9.1    | DALI initialization procedure                     | 289 |

|       | 25.9.2    | Data interrupt handling                           | 289 |

| 25.10 | DALI re   | gisters description                               | 291 |

|       | 25.10.1   | DALI_CLK_L (clock prescaler LSB)                  | 291 |

|       | 25.10.2   | DALI_CLK_H (clock prescaler MSB)                  | 291 |

|       | 25.10.3   | DALI_FB0 [forward message register (7:0)]         | 291 |

|       | 25.10.4   | DALI_FB1 [forward message register(15:8)]         | 292 |

|       | 25.10.5   | DALI_FB2 [forward message register(23:16)]        | 292 |

|       | 25.10.6   | DALI_BD [backward message register(7:0)]          | 292 |

|       | 25.10.7   | DALI_CR (control register)                        | 293 |

|       | 25.10.8   | DALI_CSR (control and status register)            | 295 |

|       | 25.10.9   | DALI_CSR1 (control and status register1)          | 296 |

|       | 25.10.10  | ) DALI_REVLN (control reverse signal line)        | 296 |

| 25.11 | DALI filt | ter control registers                             | 297 |

|       | 25.11.1   | MSC_DALICKSEL (DALI filter clock selection)       | 297 |

|       | 25.11.2   | MSC_DALICKDIV (DALI filter clock division factor) | 297 |

|       | 25.11.3   | MSC_DALICONF (DALI filter mode configuration)     | 298 |

| 25.12 | DALI re   | gisters overview                                  | 299 |

| Analo | og comp   | parator unit (ACU)                                | 300 |

| 26.1  | Overvie   | w description                                     | 300 |

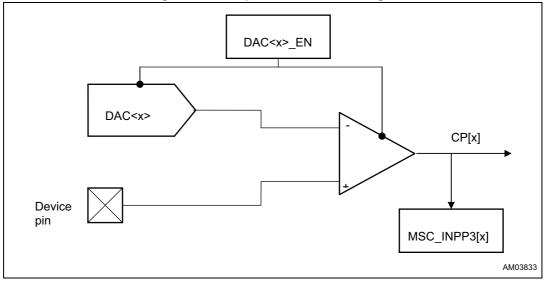

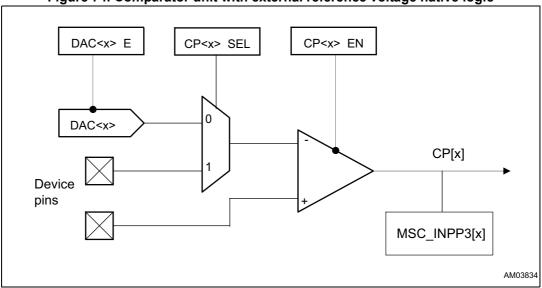

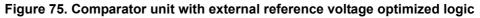

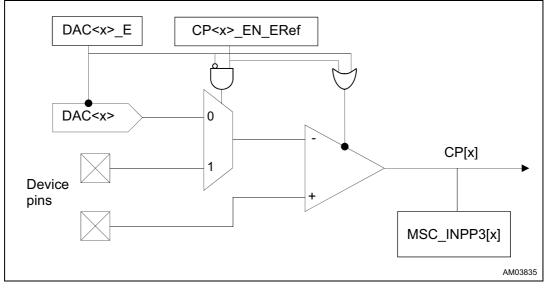

| 26.2  | Compar    | rator logic                                       | 302 |

|       | 26.2.1    | Main features                                     | 302 |

|       | 26.2.2    | DAC and comparator programming                    | 302 |

|       | 26.2.3    | Interrupt and wake up capability                  | 303 |

|       | 26.2.4    | Hysteresis programming                            | 303 |

|       | 26.2.5    | Processor interface to the comparator outputs     | 304 |

26

|    | 26.3  | DAC converter logic 30                                       | )4 |

|----|-------|--------------------------------------------------------------|----|

|    | 26.4  | DAC main features 30                                         | )4 |

|    | 26.5  | ACU programming sequence 30                                  | )5 |

|    | 26.6  | ACU low power modes                                          | )6 |

|    | 26.7  | ACU registers description                                    | )6 |

|    |       | 26.7.1 MSC_DACCTR (DAC comparator control register)          | )7 |

|    |       | 26.7.2 MSC_DACIN <n> (Dac<n> input data register)</n></n>    | )9 |

|    |       | 26.7.3 MSC_INPP3 (port P3 input data register)               | )9 |

|    |       | 26.7.4 MSC_DAC <n>HYST (DAC <n>hysteresis selection)</n></n> | 10 |

|    | 26.8  | ACU registers overview                                       | 11 |

| 27 | Analo | og-to-digital converter (ADC)                                | 2  |

|    | 27.1  | ADC main features                                            | 12 |

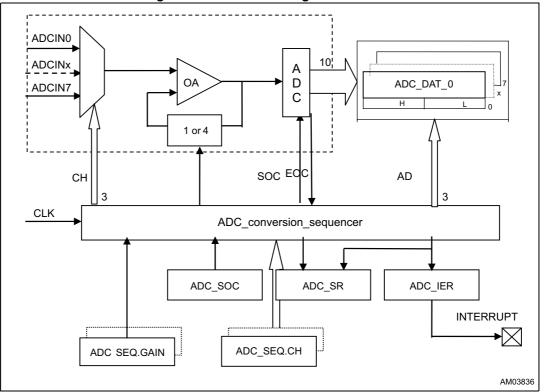

|    | 27.2  | ADC unit block diagram                                       | 12 |

|    | 27.3  | ADC analog unit                                              | 13 |

|    |       | 27.3.1 ADC analog main features                              | 14 |

|    | 27.4  | ADC digital unit                                             | 14 |

|    |       | 27.4.1 ADC digital main features                             | 15 |

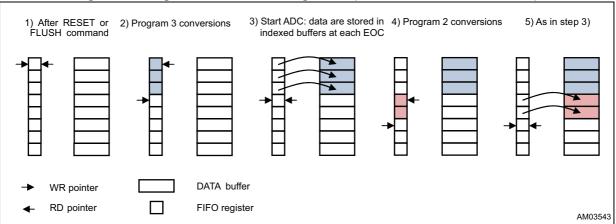

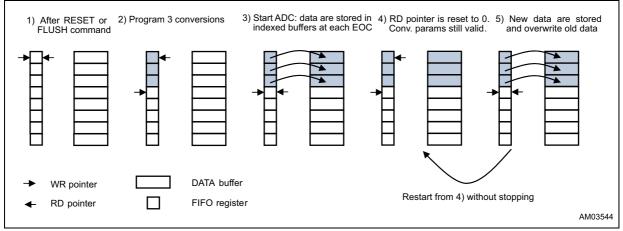

|    |       | 27.4.2 The ADC sequencer                                     | 15 |

|    |       | 27.4.3 ADC conversion modes                                  | 15 |

|    |       | 27.4.4 Start the ADC conversion                              | 18 |

|    |       | 27.4.5 Reading the conversion result                         | 19 |

|    |       | 27.4.6 DELAY register                                        | 20 |

|    |       | 27.4.7 ADC clock selection                                   | 20 |

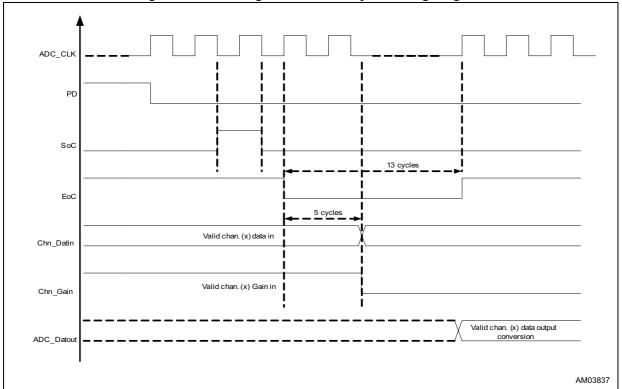

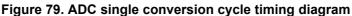

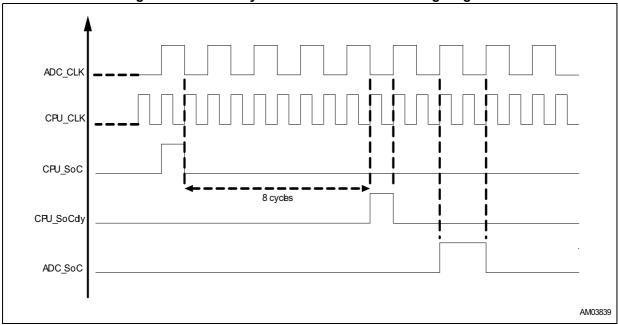

|    |       | 27.4.8 ADC timing                                            | 20 |

|    |       | 27.4.9 ADC HW trigger latency                                | 22 |

|    | 27.5  | Interrupts                                                   | 22 |

|    | 27.6  | ADC programming sequences 32                                 | 22 |

|    |       | 27.6.1 Single mode programming sequence                      | 23 |

|    |       | 27.6.2 Continuous (circular buffer) programming sequence     | 24 |

|    |       | 27.6.3 Abort sequence                                        | 24 |

|    |       | 27.6.4 ADC power-down sequence                               | 25 |

|    | 27.7  | ADC low power modes                                          | 25 |

|    | 27.8  | ADC register description                                     | 26 |

|    |       | 27.8.1 ADC_CFG (configuration register)                      | 26 |

|    |       | 27.8.2 ADC_SOC (start of conversion)                         | 27 |

|    |       |                                                              |    |

28

|      | 27.8.3  | ADC_IER (interrupt enable register)                    | . 327 |

|------|---------|--------------------------------------------------------|-------|

|      | 27.8.4  | ADC_SEQ (sequencer register)                           | . 328 |

|      | 27.8.5  | ADC_DATL_ <n> (data low register right alignment)</n>  | . 328 |

|      | 27.8.6  | ADC_DATH_ <n> (data high register right alignment)</n> | . 329 |

|      | 27.8.7  | ADC_DATL_ <n> (data low register left alignment)</n>   | . 329 |

|      | 27.8.8  | ADC_DATH_ <n> (data high register left alignment)</n>  | . 329 |

|      | 27.8.9  | ADC_SR (status register)                               | . 330 |

|      | 27.8.10 | ADC_DLYCNT (SOC delay counter register)                | . 330 |

| 27.9 | ADC H   | N trigger configuration registers description          | 331   |

|      | 27.9.1  | MSC_FTM0CONF (AddTimer0 mode configuration)            | . 331 |

|      | 27.9.2  | MSC_DALICKSEL (DALI filter clock selection)            | . 331 |

|      | 27.9.3  | MSC_INPP2AUX1 (INPP2 aux register 1)                   | . 332 |

|      |         | gisters overview                                       | ~~~   |

16/335

# List of tables

| Table 1.               | Acronym descriptions                               | 21   |

|------------------------|----------------------------------------------------|------|

| Table 2.               | Register abbreviations                             | . 23 |

| Table 3.               | STLUX/STNRG feature comparison                     | 25   |

| Table 4.               | Interrupt priority level                           | 29   |

| Table 5.               | CPU register map                                   | 34   |

| Table 6.               | SWIM internal register overview                    | 38   |

| Table 7.               | DM internal registers overview                     | 45   |

| Table 8.               | Memory access versus programming method            | 59   |

| Table 9.               | Flash registers overview                           | 65   |

| Table 10.              | Reset controller register overview                 |      |

| Table 11.              | RC16 MHz oscillator user trimming                  |      |

| Table 12.              | Oscillators stabilization cycles                   | 77   |

| Table 13.              | PLL output frequency divisor                       |      |

| Table 14.              | Clock interrupt event.                             |      |

| Table 15.              | Clock controller registers overview                |      |

| Table 16.              | Power management scheme                            |      |

| Table 17.              | Interrupt disable / enable inside the ISR          |      |

| Table 18.              | Interrupt priority encoding value                  |      |

| Table 19.              | Dedicated interrupt instruction set                |      |

| Table 20.              | ITC interrupt control registers                    |      |

| Table 21.              | MISC interrupt control registers                   |      |

| Table 22.              | Watchdog timeout period (with LSI/2 counter clock) |      |

| Table 23.              | IWDG internal registers overview                   |      |

| Table 24.              | Low power-on WWDG                                  |      |

| Table 25.              | WWDG internal registers overview.                  |      |

| Table 26.              | AWU timer interval range                           |      |

| Table 27.              | AWU internal registers overview.                   |      |

| Table 28.              | System timer internal registers overview           |      |

| Table 29.              | Auxiliary timer register overview                  |      |

| Table 30.              | BASIC timer register overview                      |      |

| Table 31.              | FSM states transition overview.                    |      |

| Table 32.              | FSM states coding                                  |      |

| Table 33.              | SMED low power mode                                |      |

| Table 34.              | SMED coupled interface configuration scheme        |      |

| Table 35.              | Tmr(S) NextHold event assignment                   |      |

| Table 36.              | Connection box interconnection matrix.             |      |

| Table 37.              | SMED core register overview                        |      |

| Table 38.              | SMED environment configuration register overview   |      |

| Table 39.              | GPIO port signal configuration                     |      |

| Table 33.<br>Table 40. | Effect of low power modes on GPIO ports            |      |

| Table 41.              | GPIO internal registers overview                   |      |

| Table 42.              | I <sup>2</sup> C low power mode                    |      |

| Table 43.              | I <sup>2</sup> C interrupt requests                |      |

| Table 43.              | I <sup>2</sup> C internal registers overview       |      |

| Table 44.<br>Table 45. | Noise detection from sampled data                  |      |

| Table 45.<br>Table 46. | Baud rate programming and error calculation        |      |

| Table 40.<br>Table 47. | Frame format                                       |      |

| Table 47.<br>Table 48. |                                                    |      |

| 1 aule 40.             | UART low power mode                                | 213  |

| UART interrupt request.                           | 273                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|---------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| UART internal registers overview                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| DALI low power mode.                              | 288                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| DALI internal registers overview                  | 299                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| DALI filter internal registers overview           | 299                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| DAC and comparator selection                      | 303                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| DAC conversion voltage scale                      | 305                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| ACU low power mode                                | 306                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| ACU register control unit overview                | 311                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| ACU MISC indirect register overview               | 311                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| ADC operating mode                                | 316                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Conversion data alignment format                  | 319                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| ADC low power mode                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| ADC digital interface internal registers overview | 333                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| ADC MISC register overview                        | 334                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Document revision history                         | 334                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                   | UART internal registers overview .<br>DALI low power mode.<br>DALI internal registers overview .<br>DALI filter internal registers overview .<br>DAC and comparator selection .<br>DAC conversion voltage scale .<br>ACU low power mode .<br>ACU low power mode .<br>ACU register control unit overview .<br>ACU MISC indirect register overview .<br>ADC operating mode .<br>Conversion data alignment format .<br>ADC low power mode .<br>ADC digital interface internal registers overview .<br>ADC MISC register overview . |

# List of figures

| Figure 1.  | STNRG high level view                                               | . 24 |

|------------|---------------------------------------------------------------------|------|

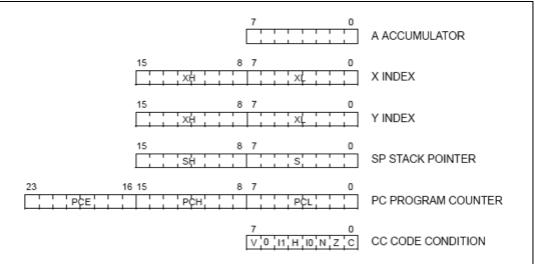

| Figure 2.  | CPU register model                                                  | . 27 |

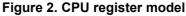

| Figure 3.  | Stacking order                                                      | . 28 |

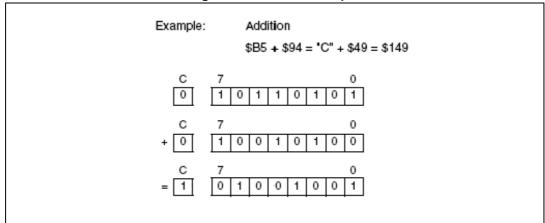

| Figure 4.  | Addition example                                                    | . 30 |

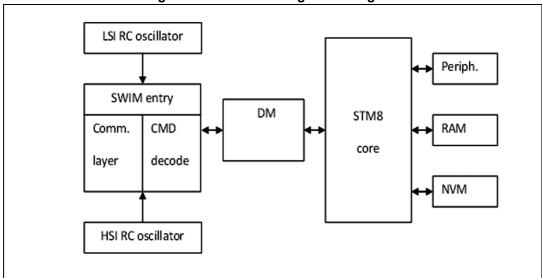

| Figure 5.  | In-circuit debug block diagram                                      |      |

| Figure 6.  | Memory map overview                                                 |      |

| Figure 7.  | Default stack model                                                 |      |

| Figure 8.  | Customized stack model                                              |      |

| Figure 9.  | Flash memory program and data EEPROM memory organization.           |      |

| Figure 10. | UBC memory area definition.                                         |      |

| Figure 11. | Power supply internal scheme                                        |      |

| Figure 12. | Reset circuit                                                       |      |

| Figure 13. | V <sub>DD</sub> voltage detection: POR/BOR threshold.               |      |

| Figure 14. | PLL output clock in the two different spread modes                  |      |

| Figure 15. | HSE clock source                                                    |      |

| Figure 16. | Main clock tree processor interfaces                                |      |

| Figure 17. | Automatic clock switch scheme                                       |      |

| Figure 18. | Manual clock switch scheme                                          |      |

| Figure 19. | ADC real-time clock scheme                                          |      |

| Figure 19. | SMED real-time clock scheme                                         |      |

| -          | CCO clock scheme                                                    |      |

| Figure 21. |                                                                     |      |

| Figure 22. | Power management transition state                                   |      |

| Figure 23. | Interrupt processing flowchart.                                     |      |

| Figure 24. | Concurrent interrupt management                                     |      |

| Figure 25. | Nested interrupt management                                         |      |

| Figure 26. | Independent watchdog (IWDG) block diagram.                          |      |

| Figure 27. | Window watchdog block diagram                                       |      |

| Figure 28. | Approximate timeout (ms) at 16 MHz f <sub>CPU</sub>                 |      |

| Figure 29. | Windows watchdog timing diagram                                     |      |

| Figure 30. | AWU block diagram                                                   |      |

| Figure 31. | STMR block diagram                                                  |      |

| Figure 32. | STMR counting mode                                                  |      |

| Figure 33. | Counter update when ARPE = 0 (ARR not preloaded) with prescaler = 2 |      |

| Figure 34. | Counter update when ARPE = 1 (ARR preloaded).                       |      |

| Figure 35. | SMED architecture                                                   |      |

| Figure 36. | FSM state transition graph                                          |      |

| Figure 37. | Sequential state transition                                         |      |

| Figure 38. | Event controlled state transitions                                  | 175  |

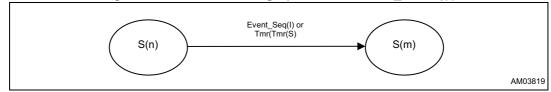

| Figure 39. | OR state transition graph                                           |      |

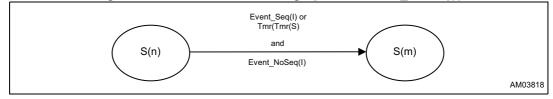

| Figure 40. | AND state transition graph with Event_NoSeq(I)                      | 177  |

| Figure 41. | AND transition graph without Event_NoSeq(I)                         | 177  |

| Figure 42. | Counter reset example                                               |      |

| Figure 43. | Dithering example                                                   | 185  |

| Figure 44. | Single couple SMEDs interconnection scheme                          |      |

| Figure 45. | Single couple SMEDs with SMD <n,n+1>_DRVOUT bit cleared</n,n+1>     | 191  |

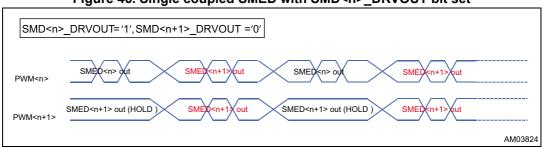

| Figure 46. | Single coupled SMED with SMD <n>_DRVOUT bit set</n>                 | 192  |

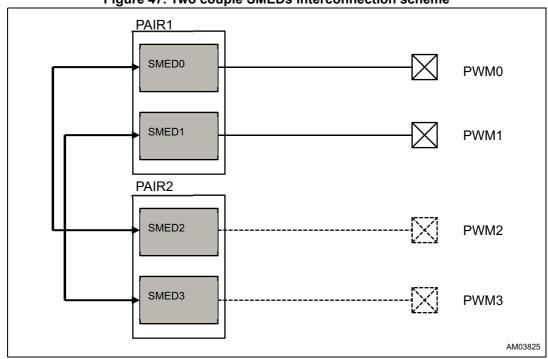

| Figure 47. | Two couple SMEDs interconnection scheme                             | 193  |

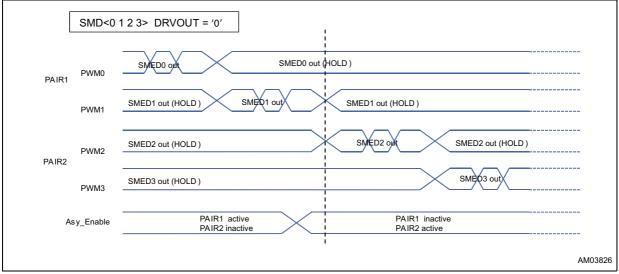

| Figure 48. | Two couple SMEDs with SMD<0,1,2,3>_DRVOUT bits cleared              | 194  |

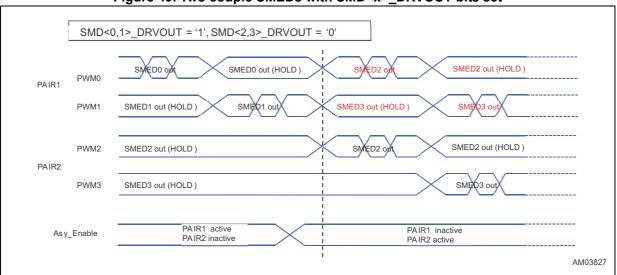

| Figure 49.    | Two couple SMEDs with SMD <x>_DRVOUT bits set</x>                     | 105 |

|---------------|-----------------------------------------------------------------------|-----|

| Figure 50.    | SMED unlock sequence                                                  |     |

| Figure 51.    | Interconnection matrix for one SMED.                                  |     |

| Figure 51.    | $I^2C$ bus protocol                                                   |     |

| Figure 52.    | Transfer sequence diagram for slave transmitter                       |     |

| Figure 54.    | Transfer sequence diagram for slave receiver                          |     |

| •             | Transfer sequence diagram for master transmitter                      |     |

| Figure 55.    |                                                                       |     |

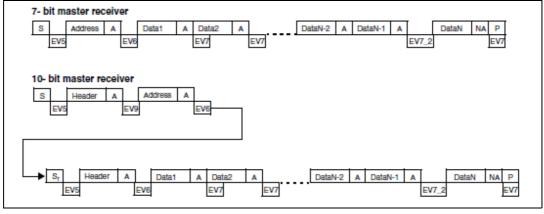

| Figure 56.    | Transfer sequence diagram for master receiver.                        |     |

| Figure 57.    | Method 2 - transfer sequence diagram for master receiver when $N > 2$ |     |

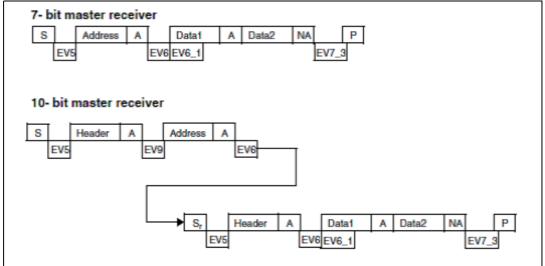

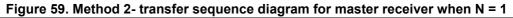

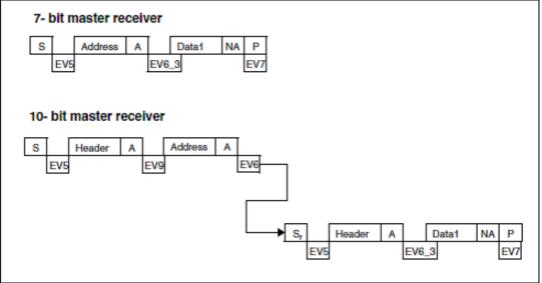

| Figure 58.    | Method 2 - transfer sequence diagram for master receiver when N = 2   |     |

| Figure 59.    | Method 2- transfer sequence diagram for master receiver when $N = 1$  |     |

| Figure 60.    | I <sup>2</sup> C interrupt mapping diagram                            |     |

| Figure 61.    | Word length programming                                               |     |

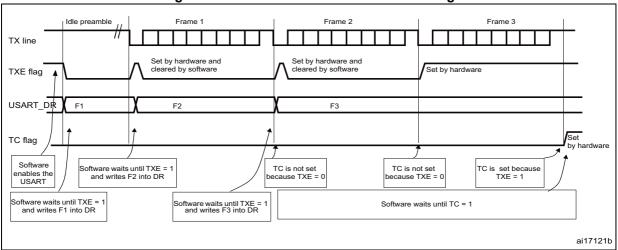

| Figure 62.    | TC/TXE behavior when transmitting                                     |     |

| Figure 63.    | Start bit detection                                                   |     |

| Figure 64.    | Data sampling for noise detection                                     |     |

| Figure 65.    | UART baud rate generator                                              |     |

| Figure 66.    | Mute mode using idle line detection                                   | 272 |

| Figure 67.    | Mute mode using address mark detection                                | 272 |

| Figure 68.    | UART Interrupt mapping diagram.                                       | 274 |

| Figure 69.    | DALI block diagram                                                    | 283 |

| Figure 70.    | DALI transfer sequences                                               | 284 |

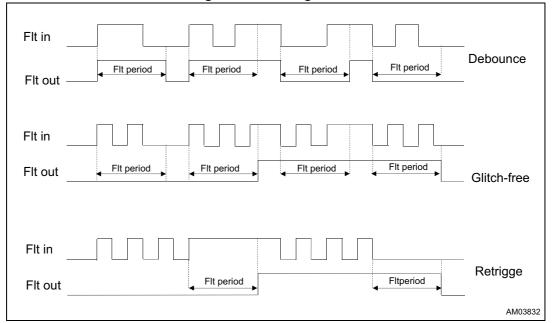

| Figure 71.    | Digital input filter interconnection scheme                           |     |

| Figure 72.    | Filtering modes                                                       |     |

| Figure 73.    | Comparator unit native logic                                          |     |

| Figure 74.    | Comparator unit with external reference voltage native logic          |     |

| Figure 75.    | Comparator unit with external reference voltage optimized logic       |     |

| Figure 76.    | ADC block diagram overview                                            |     |

| Figure 77.    | Single mode buffer management (w/o FIFO flush or auto-flush)          |     |

| Figure 78.    | Continuous mode buffer management                                     |     |

| Figure 79.    | ADC single conversion cycle timing diagram                            |     |

| Figure 80.    | ADC continue conversion cycle timing diagram                          |     |

| Figure 81.    | ADC delayed start of conversion timing diagram                        |     |

| i igui e o i. |                                                                       | 521 |

## 1 Reference documents

- For hardware information on the STLUX controller and product specific SMED configuration, please refer to the STLUX product datasheets for STLUX385A, STLUX383A, STLUX325A and STLUX285A.

- For hardware information of the STNRG controller and product specific SMED configuration, please refer to the STNRG product datasheets for STNRG388A, STNRG328A and STNRG288A.

- For information on programming, erasing and protection of the internal Flash memory please refer to the programming manual PM0051 "How to program STM8S and STM8A Flash program memory and data EEPROM".

- For information about the debug module and SWIM (single wire interface module) refer to the STM8 SWIM communication protocol and debug module user manual (UM0470).

- For information on the STM8 core and assembler instruction please refer to the STM8 CPU programming manual (PM0044).

- For information on the development tools please refer to the UM1792.

## 2 Acronyms

The following is a list of acronyms used in this document:

| Table 1. Acronym descriptions |                                                                 |  |  |  |

|-------------------------------|-----------------------------------------------------------------|--|--|--|

| Acronym                       | ym Description                                                  |  |  |  |

| ACU                           | Analog comparator unit                                          |  |  |  |

| ADC                           | Analog-to-digital converter                                     |  |  |  |

| AWU                           | Auto-wakeup unit                                                |  |  |  |

| BL                            | Bootloader - used to load the user program without the emulator |  |  |  |

| СКС                           | Clock control unit                                              |  |  |  |

| CPU                           | Central processing unit                                         |  |  |  |

| CSS                           | Clock security system                                           |  |  |  |

| DAC                           | Digital-to-analog converter                                     |  |  |  |

| DALI                          | Digital addressable lighting interface                          |  |  |  |

| ECC                           | Error Correction Code                                           |  |  |  |

| FSM                           | Finite state machine                                            |  |  |  |

| FW                            | Firmware loaded and running on the CPU                          |  |  |  |

| GPIO                          | General purpose input/output                                    |  |  |  |

| HSE                           | High-speed external crystal - ceramic resonator                 |  |  |  |

| HSI                           | High-speed internal RC oscillator                               |  |  |  |

#### Table 1. Acronym descriptions

| Table 1. Acronym descriptions (continued) |                                                                           |  |  |  |

|-------------------------------------------|---------------------------------------------------------------------------|--|--|--|

| Acronym                                   | Acronym Description                                                       |  |  |  |

| l <sup>2</sup> C                          | Inter-integrated circuit interface                                        |  |  |  |

| IAP                                       | In-application programming                                                |  |  |  |

| ICP                                       | In-circuit programming                                                    |  |  |  |

| ITC                                       | Interrupt controller                                                      |  |  |  |

| IWDG                                      | Independent watchdog                                                      |  |  |  |

| LSI                                       | Low-speed internal RC oscillator                                          |  |  |  |

| MCU                                       | Microprocessor central unit                                               |  |  |  |

| MSC                                       | Miscellaneous                                                             |  |  |  |

| PM                                        | Power management                                                          |  |  |  |

| RFU                                       | Reserved for future use                                                   |  |  |  |

| ROP                                       | Read-out protection                                                       |  |  |  |

| RST                                       | Reset control unit                                                        |  |  |  |

| RTC                                       | Real-time clock                                                           |  |  |  |

| SMED                                      | State machine, event driven                                               |  |  |  |

| STMR                                      | System timer                                                              |  |  |  |

| SW                                        | Software is the firmware loaded and running on the CPU (synonymous of FW) |  |  |  |

| SWIM                                      | Single wire interface module                                              |  |  |  |

| UART                                      | Universal asynchronous receiver transmitter                               |  |  |  |

| WWDG                                      | Window watchdog                                                           |  |  |  |

|                                           |                                                                           |  |  |  |

Table 1. Acronym descriptions (continued)

\_\_\_\_\_

# 3 Register model

Table 2 shows an outline picture of the register abbreviations used in this document.

| Abbreviation             | Description                                                                                                                    |

|--------------------------|--------------------------------------------------------------------------------------------------------------------------------|