## UM0339 User manual

#### SuperH<sup>™</sup> (SH) 32-bit RISC series SH-4, ST40 system architecture, volume 1: system

This manual describes the ST40 family system architecture. It is split into four volumes:

ST40 System Architecture - Volume 1 System - ADCS 7153464.

ST40 System Architecture - Volume 2 Bus Interfaces - ADCS 7181720.

ST40 System Architecture - Volume 3 Video Devices - ADCS 7225754.

ST40 System Architecture - Volume 4 I/O Devices - ADCS 7225754.

# Contents

| Pre | face   |                                                  | xxi     |

|-----|--------|--------------------------------------------------|---------|

|     | Docur  | nent identification and control                  | xxi     |

|     | ST40   | documentation suite                              | xxi     |

|     |        | ST40 Micro Toolset User's Guide                  | xxi     |

|     |        | OS21 User's Manual                               | xxii    |

|     |        | OS21 for ST40 User Manual                        | xxii    |

|     |        | 32-Bit RISC Series, SH-4 CPU Core Architecture   | xxii    |

|     |        | 32-Bit RISC Series, SH-4, ST40 System Architectu | re xxii |

|     | Conve  | entions used in this guide                       | xxiii   |

|     |        | General notation                                 | xxiii   |

|     |        | Hardware notation                                | xxiii   |

|     |        | Software notation                                | xxiii   |

| Ove | erview | I                                                | 1       |

| 1.1 | ST40   | features                                         | 1       |

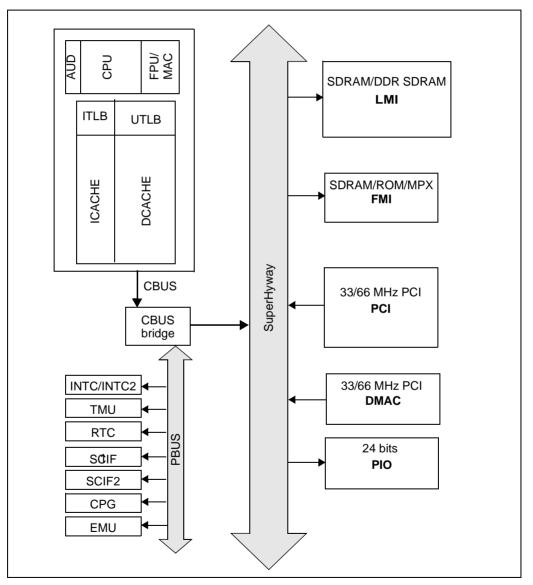

| 1.2 | Block  | diagram                                          | 2       |

|     | 1.2.1  | CPU                                              | 3       |

|     | 1.2.2  | FPU/MAC                                          | 3       |

|     | 1.2.3  | MMU                                              | 4       |

|     | 1.2.4  | Cache                                            | 4       |

|     | 1.2.5  | Interrupt                                        | 5       |

|     | 1.2.6  | DMA controller                                   | 5       |

|     |        |                                                  |         |

**STMicroelectronics**

1

SH-4, ST40 System Architecture, Volume 1: System

- 17 -

|   |                    | 1.2.7                                                                                   | Debugging and emulation                                                                                                                                                                                                      | 5                                                  |

|---|--------------------|-----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

|   |                    | 1.2.8                                                                                   | Power management                                                                                                                                                                                                             | 6                                                  |

|   |                    | 1.2.9                                                                                   | Timers                                                                                                                                                                                                                       | 6                                                  |

|   |                    | 1.2.10                                                                                  | Real-time clock                                                                                                                                                                                                              | 6                                                  |

|   |                    | 1.2.11                                                                                  | Serial communication                                                                                                                                                                                                         | 6                                                  |

|   |                    | 1.2.12                                                                                  | External memory support                                                                                                                                                                                                      | 6                                                  |

| 2 | Sys                | tem or                                                                                  | ganization                                                                                                                                                                                                                   | 7                                                  |

|   | 2.1                | The S                                                                                   | uperHyway                                                                                                                                                                                                                    | 7                                                  |

|   |                    | 2.1.1                                                                                   | SuperHyway architecture                                                                                                                                                                                                      | 7                                                  |

|   |                    | 2.1.2                                                                                   | Packets                                                                                                                                                                                                                      | 9                                                  |

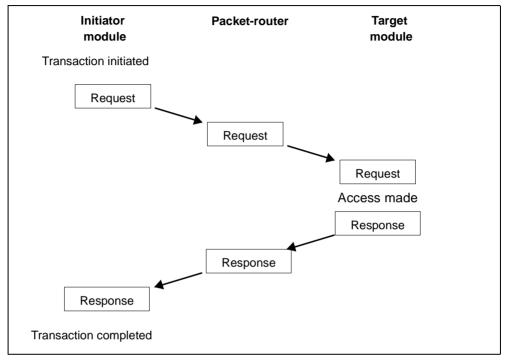

|   |                    | 2.1.3                                                                                   | Transactions                                                                                                                                                                                                                 | 10                                                 |

|   |                    |                                                                                         | Request                                                                                                                                                                                                                      |                                                    |

|   |                    |                                                                                         | Response                                                                                                                                                                                                                     |                                                    |

|   |                    | 2.1.4                                                                                   | A complete transaction<br>SuperHyway packet-router                                                                                                                                                                           | 13                                                 |

|   | 0 0                |                                                                                         |                                                                                                                                                                                                                              | 13                                                 |

|   | 2.2                | Physic                                                                                  | cal address map                                                                                                                                                                                                              | 15                                                 |

|   |                    |                                                                                         |                                                                                                                                                                                                                              |                                                    |

| 3 | Inte               | errupt                                                                                  | controller (INTC)                                                                                                                                                                                                            | 15                                                 |

| 3 | <b>Inte</b><br>3.1 | e <b>rrupt</b><br>Overv                                                                 |                                                                                                                                                                                                                              | <b>15</b><br>15                                    |

| 3 |                    | -                                                                                       |                                                                                                                                                                                                                              | _                                                  |

| 3 |                    | Overv                                                                                   | iew                                                                                                                                                                                                                          | 15                                                 |

| 3 |                    | Overv<br>3.1.1                                                                          | iew<br>INTC features                                                                                                                                                                                                         | 15<br>15                                           |

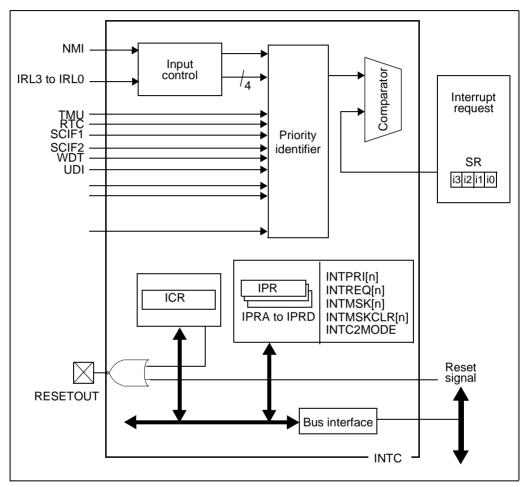

| 3 |                    | Overv<br>3.1.1<br>3.1.2                                                                 | iew<br>INTC features<br>Block diagram                                                                                                                                                                                        | 15<br>15<br>16                                     |

| 3 |                    | Overv<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4                                               | iew<br>INTC features<br>Block diagram<br>Pin configuration                                                                                                                                                                   | 15<br>15<br>16<br>17                               |

| 3 | 3.1                | Overv<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4                                               | iew<br>INTC features<br>Block diagram<br>Pin configuration<br>Register configuration                                                                                                                                         | 15<br>15<br>16<br>17<br>17                         |

| 3 | 3.1                | Overv<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>Interr                                     | iew<br>INTC features<br>Block diagram<br>Pin configuration<br>Register configuration<br>upt sources                                                                                                                          | 15<br>15<br>16<br>17<br>17<br>19                   |

| 3 | 3.1                | Overv<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>Interr<br>3.2.1                            | iew<br>INTC features<br>Block diagram<br>Pin configuration<br>Register configuration<br>upt sources<br>NMI interrupts                                                                                                        | 15<br>15<br>16<br>17<br>17<br>19<br>19             |

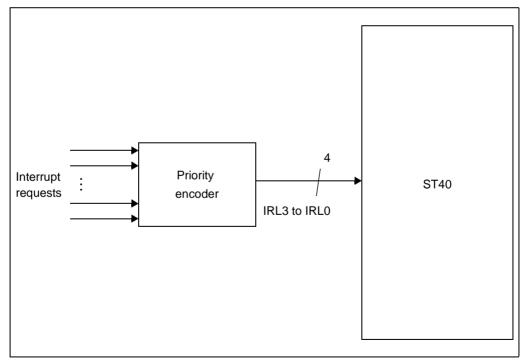

| 3 | 3.1                | Overv<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>Interr<br>3.2.1<br>3.2.2                   | iew<br>INTC features<br>Block diagram<br>Pin configuration<br>Register configuration<br>upt sources<br>NMI interrupts<br>IRL interrupts                                                                                      | 15<br>15<br>16<br>17<br>17<br>19<br>19<br>20       |

| 3 | 3.1                | Overv<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>Interr<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4 | iew<br>INTC features<br>Block diagram<br>Pin configuration<br>Register configuration<br>upt sources<br>NMI interrupts<br>IRL interrupts<br>On-chip peripheral module interrupts                                              | 15<br>15<br>16<br>17<br>17<br>19<br>19<br>20<br>22 |

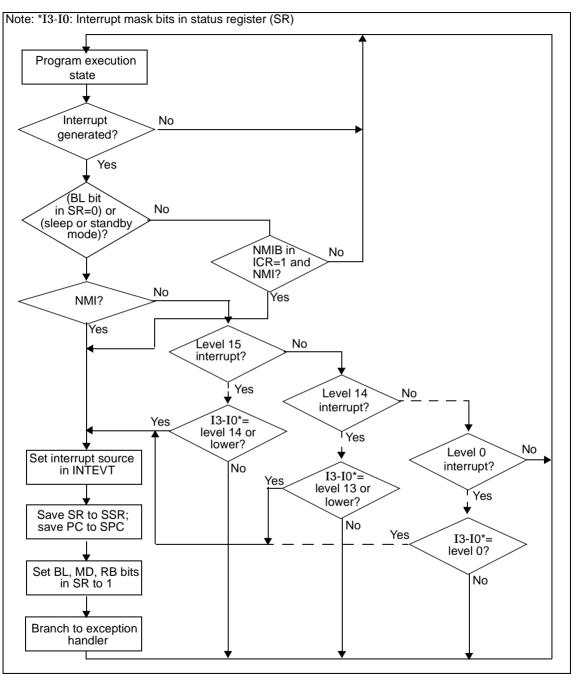

| 3 | 3.1<br>3.2         | Overv<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>Interr<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4 | iew<br>INTC features<br>Block diagram<br>Pin configuration<br>Register configuration<br>upt sources<br>NMI interrupts<br>IRL interrupts<br>On-chip peripheral module interrupts<br>Interrupt exception handling and priority | 15<br>15<br>16<br>17<br>17<br>19<br>20<br>22<br>23 |

- 477 -

|   |     |       | Bit 15: NMI input level (NMIL)<br>Bit 14: NMI interrupt mask (MAI)<br>Bit 9: NMI block mode (NMIB)<br>Bit 8: NMI edge select (NMIE)<br>Bit 7: IRL pin mode<br>Bits 13 to 10 and 6 to 0: reserved |    |

|---|-----|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|   |     | 3.3.3 | Interrupt priority registers<br>(INTPRI00, INTPRI04, INTPRI08)                                                                                                                                   | 30 |

|   |     | 3.3.4 | Interrupt request registers<br>(INTREQ00, INTREQ04, INTREQ08)                                                                                                                                    | 32 |

|   |     | 3.3.5 | Interrupt mask registers<br>(INTMSK00, INTMSK04, INTMSK08)                                                                                                                                       | 34 |

|   |     | 3.3.6 | Interrupt mask clear registers<br>(INTMSKCLR00, INTMSKCLR04, INTMSKCLR08)                                                                                                                        | 36 |

|   |     | 3.3.7 | INTC2 mode register (INTC2MODE)                                                                                                                                                                  | 38 |

|   | 3.4 | INTC  | operation                                                                                                                                                                                        | 40 |

|   |     | 3.4.1 | Interrupt sequence                                                                                                                                                                               | 40 |

|   |     | 3.4.2 | Multiple interrupts                                                                                                                                                                              | 42 |

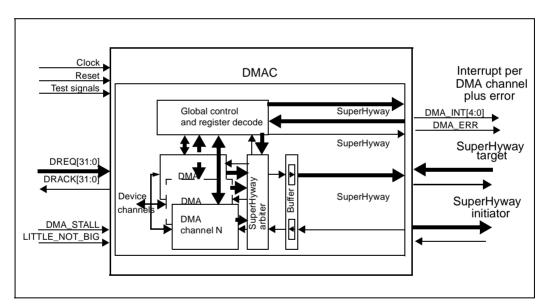

| 4 | GPI | DMA o | controller (DMAC)                                                                                                                                                                                | 43 |

|   | 4.1 | Featu | res                                                                                                                                                                                              | 43 |

|   | 4.2 | Addre | ess map                                                                                                                                                                                          | 45 |

|   |     | 4.2.1 | Channel 0: multiplexed DMA channel                                                                                                                                                               | 47 |

|   |     | 4.2.2 | Channels 1 to 4: linked list DMA channel                                                                                                                                                         | 49 |

|   | 4.3 | Perip | heral allocation                                                                                                                                                                                 | 50 |

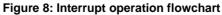

|   | 4.4 | DMA   | operation                                                                                                                                                                                        | 51 |

|   |     | 4.4.1 | DMA transfer procedure<br>Stall<br>Error<br>Disable<br>Completion                                                                                                                                | 51 |

|   |     | 4.4.2 | DMA transfer units                                                                                                                                                                               | 53 |

|   |     | 4.4.3 | DMA timing model                                                                                                                                                                                 | 53 |

|   |     |       | Free-running                                                                                                                                                                                     |    |

STMicroelectronics SH-4, ST40 System Architecture, Volume 1: System

- // -

|     |        | Paced                             |    |

|-----|--------|-----------------------------------|----|

|     | 4.4.4  | DMA requests                      | 54 |

|     | 4.4.5  | DMA data organization             | 55 |

|     |        | Single location/0D                |    |

|     |        | Incrementing/1D                   |    |

|     |        | Rectangular array/2D              |    |

|     | 4.4.6  | Endianness                        | 57 |

|     | 4.4.7  | DMA channel arbitration           | 57 |

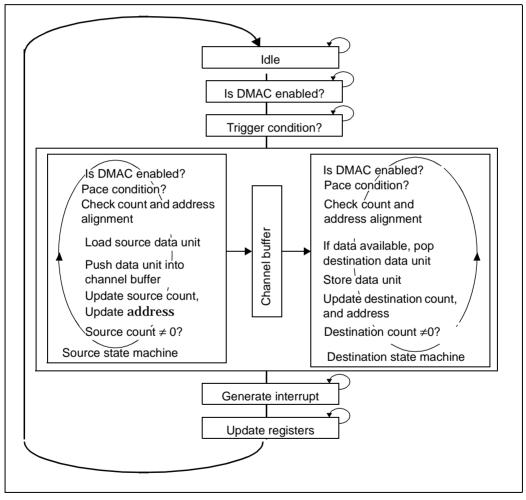

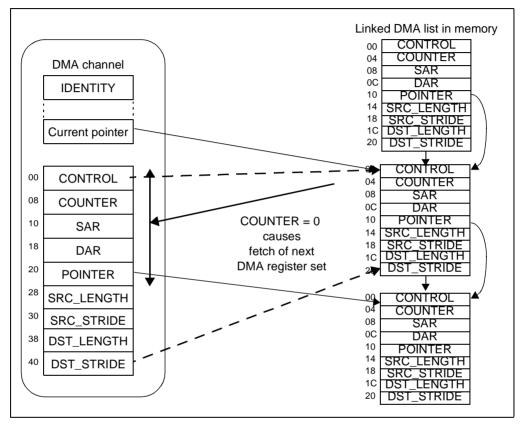

|     | 4.4.8  | Extension to basic DMA operations | 57 |

|     |        | Single linked list                |    |

|     |        | Multiplexed channels              |    |

| 4.5 | Interf | aces                              | 60 |

| 4.6 | Pogist | ter descriptions                  | 61 |

| 4.0 | -      | _                                 |    |

|     | 4.6.1  | Global registers                  | 62 |

|     |        | DMA.VCR.STATUS                    |    |

|     |        | DMA.VCR.VERSION                   |    |

|     |        | DMA.ENABLE                        |    |

|     |        | DMA.DISABLE                       |    |

|     |        | DMA.STATUS                        |    |

|     |        | DMA.INTERRUPT<br>DMA.ERROR        |    |

|     |        | DMA.DEFINED                       |    |

|     |        | DMA.HANDSHAKE                     |    |

|     | 4.6.2  | Channel specific registers        | 71 |

|     | 1.0.2  | DMA.CHAN[n].IDENTITY              |    |

|     |        | DMA.CHAN[n].ENABLE                |    |

|     |        | DMA.CHAN[n].DISABLE               |    |

|     |        | DMA.CHAN[n].STATUS                |    |

|     |        | DMA.CHAN[n].ACTION                |    |

|     |        | DMA.CHAN[n].POINTER               |    |

|     |        | DMA.CHAN[n].REQUEST               |    |

|     |        | DMA.CHAN[n].SUBBASE               |    |

|     |        | DMA.CHAN[n].SUBENABLE             |    |

|     |        | DMA.CHAN[n].SUBDISABLE            |    |

|     |        | DMA.CHAN[n].SUB_INTENB            |    |

|     |        | DMA.CHAN[n].SUBINT_DIS            |    |

|     |        | DMA.CHAN[n].SUBINT_STAT           |    |

|     |        | DMA.CHAN[n].SUBINT_ACT            |    |

|     | 4.6.3  | Memory mapped channel registers   | 93 |

- 477 -

|   |     |                | DMA.CHAN[n].CONTROL<br>DMA.CHAN[n].COUNT                                    |     |

|---|-----|----------------|-----------------------------------------------------------------------------|-----|

|   |     |                | DMA.CHAN[n].SAR<br>DMA.CHAN[n].DAR                                          |     |

|   |     |                | DMA.CHAN[n].NEXT_PTR                                                        |     |

|   |     |                | DMA.CHAN[n].SRC_LENGTH                                                      |     |

|   |     |                | DMA.CHAN[n].SRC_STRIDE                                                      |     |

|   |     |                | DMA.CHAN[n].DST_LENGTH<br>DMA.CHAN[n].DST_STRIDE                            |     |

| 5 | Par | allel ir       | nput/output (PIO)                                                           | 107 |

|   | 5.1 | PIO po         | orts 0 to 2                                                                 | 107 |

|   | 5.2 | Regist         | er descriptions                                                             | 109 |

|   |     | 5.2.1          | Output registers                                                            | 109 |

|   |     | 5.2.2          | Input registers                                                             | 112 |

|   |     | 5.2.3          | Configuration registers                                                     | 113 |

|   |     | 5.2.4          | PIO input compare and compare mask registers                                | 116 |

|   |     | 5.2.5          | Pseudoregisters                                                             | 118 |

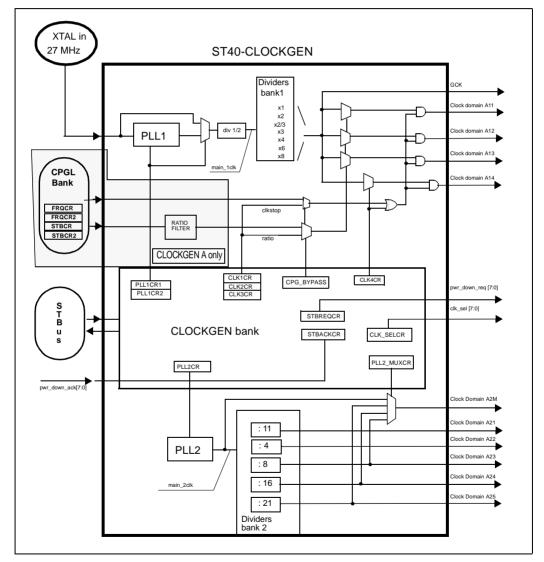

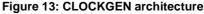

| 6 | Clo | ck and         | l power management                                                          | 121 |

|   | 6.1 | Overvi         | iew                                                                         | 121 |

|   | 6.2 | Addres         | ss map                                                                      | 122 |

|   |     | 6.2.1          | CPG bank                                                                    | 122 |

|   |     | 6.2.2          | CLKGEN bank                                                                 | 123 |

|   | 6.3 | <b>Clock</b> t | functionality                                                               | 125 |

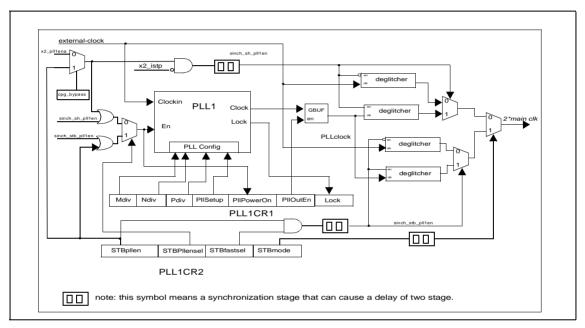

|   |     | 6.3.1          | Internal organization                                                       | 125 |

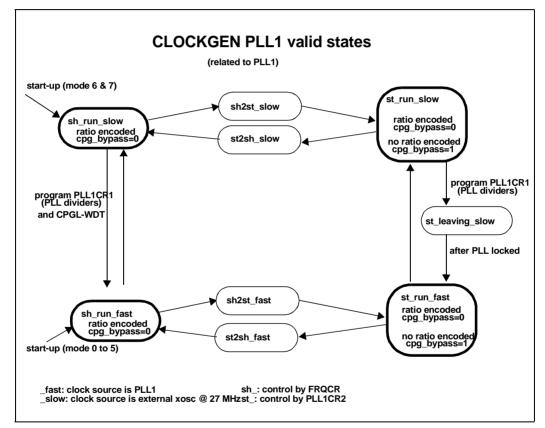

|   |     | 6.3.2          | PLL1 control                                                                | 127 |

|   |     |                | Diagram                                                                     |     |

|   |     |                | Introduction<br>Allowable transitions                                       |     |

|   |     |                | State definitions                                                           |     |

|   |     |                | Enabling and disabling PLL1                                                 |     |

|   |     |                | Changing PLL1 divide ratios (clk1 to 3)                                     |     |

|   |     |                | Changing the PLL1 divide ratio for clock 14<br>Changing PLL1 lock frequency |     |

|   |     |                | Changing FLL1 lock frequency                                                |     |

STMicroelectronics SH-4, ST40 System Architecture, Volume 1: System

- // -

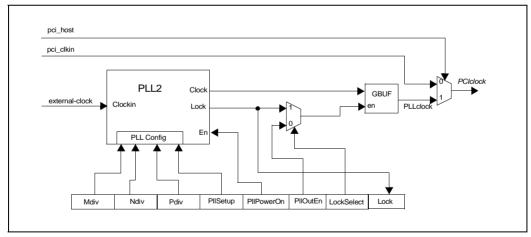

|     | 6.3.3          | Configuring PLL2                                                                      | 132 |  |

|-----|----------------|---------------------------------------------------------------------------------------|-----|--|

|     |                | Introduction                                                                          |     |  |

|     |                | Procedure to enable and disable PLL2                                                  |     |  |

|     | 694            | Changing the frequency of PLL2                                                        | 134 |  |

|     | 6.3.4          | Register description                                                                  | 134 |  |

|     |                | Frequency control register 1 (CPG.FRQCR)<br>CLKGEN.PLL1CR1                            |     |  |

|     |                | CLKGEN.PLL1CR2                                                                        |     |  |

|     |                | CLKGEN.PLL2CR                                                                         |     |  |

|     |                | CLOCKGEN.CLK4CR                                                                       |     |  |

|     |                | CLOCKGEN.CPGBYPASS                                                                    |     |  |

|     |                | CLKGEN.PLL2_MUXCR                                                                     |     |  |

|     |                | CLKGEN.CLK1CR                                                                         |     |  |

|     |                | CLKGEN.CLK2CR<br>CLKGEN.CLK3CR                                                        |     |  |

|     |                | CLKGEN.CLK_SELCR                                                                      |     |  |

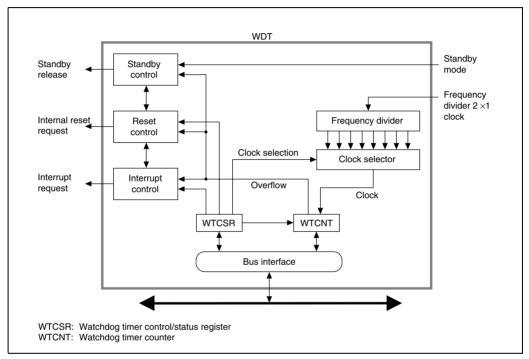

| 6.4 | Watchdog timer |                                                                                       |     |  |

| 0.4 |                |                                                                                       | 153 |  |

|     | 6.4.1          | Block diagram                                                                         | 153 |  |

|     | 6.4.2          | Register configuration                                                                | 154 |  |

|     | 6.4.3          | Register descriptions                                                                 | 154 |  |

|     |                | Watchdog timer counter (CPG.WTCNT)                                                    |     |  |

|     |                | Watchdog timer control and status register<br>(CPG.WTCSR)                             |     |  |

|     |                | Bit 7: timer enable (TME)                                                             |     |  |

|     |                | Bit 6: timer mode select (WT/NOT_IT)                                                  |     |  |

|     |                | Bit 5: reset select (RSTS)                                                            |     |  |

|     |                | Bit 4: watchdog timer overflow flag (WOVF)                                            |     |  |

|     |                | Bit 3: interval timer overflow flag (IOVF)                                            |     |  |

|     |                | Bits 2 to 0: clock select 2 to 0 (CKS2 to CKS0)<br>Writing to CPG.WTCNT and CPG.WTCSR |     |  |

|     | 6.4.4          | _                                                                                     | 159 |  |

|     | 0.4.4          | Using the WDT                                                                         | 159 |  |

|     |                | Standby clearing procedure<br>Frequency changing procedure                            |     |  |

|     |                | Using watchdog timer mode                                                             |     |  |

|     |                | Using interval timer mode                                                             |     |  |

| 6.5 | Power          | management unit (PMU)                                                                 | 161 |  |

|     | 6.5.1          | Types of power-down modes                                                             | 162 |  |

|     | 6.5.2          | Register configuration                                                                | 164 |  |

|     |                |                                                                                       |     |  |

- 477 -

STMicroelectronics SH-4, ST40 System Architecture, Volume 1: System

#### **PRELIMINARY DATA**

|     | 6.5.3 | Pin conf  | iguration                                                   | 165     |

|-----|-------|-----------|-------------------------------------------------------------|---------|

|     | 6.5.4 | Register  | descriptions                                                | 165     |

|     |       | -         | Standby control register (CPG.STBCR)                        |         |

|     |       |           | Bit 7: standby (STBY)                                       |         |

|     |       |           | Bit 6: peripheral module pin high impedance (PHZ)           | control |

|     |       |           | Bit 5: peripheral module pin pull-up control (              | PPU)    |

|     |       |           | Bit 4: unused                                               |         |

|     |       |           | Bit 3: module stop 3 (MSTP3)                                |         |

|     |       |           | Bit 2: module stop 2 (MSTP2)                                |         |

|     |       |           | Bit 1: module stop 1 (MSTP1)                                |         |

|     |       |           | Bit 0: module stop 0 (MSTP0)                                |         |

|     |       |           | Peripheral module pin pull-up control                       |         |

|     |       |           | Standby control register 2 (CPG.STBCR2)                     |         |

|     |       |           | Bit 7: unused                                               |         |

|     |       |           | Bit 6: status pin high-impedance control (STH               | HZ)     |

|     |       |           | Bits 5 to 2: reserved                                       |         |

|     |       |           | Bit 1: module stop 6 (MSTP6)                                |         |

|     |       |           | Bit 0: module stop 5 (MSTP5)                                |         |

|     |       |           | Standby control request register                            |         |

|     |       |           | (CLOCKGEN.STBREQCR)                                         |         |

|     |       |           | Standby control acknowledge register<br>(CLOCKGEN.STBACKCR) |         |

| 6.6 | Funct | ionality  |                                                             | 171     |

|     | 6.6.1 | Sleep m   | ode                                                         | 171     |

|     |       | 1         | Transition to sleep mode                                    |         |

|     |       |           | Exit from sleep mode                                        |         |

|     |       |           | Exit by interrupt                                           |         |

|     |       |           | Exit by reset                                               |         |

|     | 6.6.2 | Deep sle  | eep mode                                                    | 172     |

|     |       | -         | -<br>Transition to deep sleep mode                          |         |

|     |       |           | Exit from deep sleep mode                                   |         |

|     | 6.6.3 | Standby   |                                                             | 172     |

|     |       | 5         | Transition to standby mode                                  |         |

|     |       |           | Exit from standby mode                                      |         |

|     |       |           | Exit by interrupt                                           |         |

|     |       |           | Exit by reset                                               |         |

|     | 6.6.4 | Clock pa  | ause function                                               | 174     |

| 6.7 | Modu  | le standt | by function                                                 | 175     |

| 0.7 | wiouu | ic stanut |                                                             | 175     |

- // -

STMicroelectronics SH-4, ST40 System Architecture, Volume 1: System

|   |     | 6.7.1  | Transition to module standby function<br>(CPG modules)      | 175 |

|---|-----|--------|-------------------------------------------------------------|-----|

|   |     | 6.7.2  | Transition to module standby function<br>(CLOCKGEN modules) | 176 |

|   |     | 6.7.3  | Exit from module standby function<br>(CPG modules)          | 176 |

|   |     | 6.7.4  | Exit from module standby function<br>(CLOCKGEN modules)     | 177 |

|   | 6.8 | STAT   | US pin change timing                                        | 177 |

| 7 | Rea | l-time | e clock (RTC)                                               | 179 |

|   | 7.1 | Overv  | view                                                        | 179 |

|   |     | 7.1.1  | Features                                                    | 179 |

|   |     | 7.1.2  | Block diagram                                               | 181 |

|   |     | 7.1.3  | Pin configuration                                           | 182 |

|   |     | 7.1.4  | Register configuration                                      | 182 |

|   |     | 7.1.5  | Register initialization                                     | 184 |

|   | 7.2 | Regis  | ter descriptions                                            | 185 |

|   |     | 7.2.1  | 64 Hz counter (RTC.R64CNT)                                  | 185 |

|   |     | 7.2.2  | Second counter (RTC.RSECCNT)                                | 186 |

|   |     | 7.2.3  | Minute counter (RTC.RMINCNT)                                | 188 |

|   |     | 7.2.4  | Hour counter (RTC.RHRCNT)                                   | 190 |

|   |     | 7.2.5  | Day-of-week counter (RTC.RWKCNT)                            | 192 |

|   |     | 7.2.6  | Day counter (RTC.RDAYCNT)                                   | 194 |

|   |     | 7.2.7  | Month counter (RTC.RMONCNT)                                 | 196 |

|   |     | 7.2.8  | Year counter (RTC.RYRCNT)                                   | 198 |

|   |     | 7.2.9  | Second alarm register (RTC.RSECAR)                          | 200 |

|   |     | 7.2.10 | Minute alarm register (RTC.RMINAR)                          | 202 |

|   |     | 7.2.11 | Hour alarm register (RTC.RHRAR)                             | 204 |

|   |     | 7.2.12 | Day-of-week alarm register (RTC.RWKAR)                      | 206 |

|   |     | 7.2.13 | Day alarm register (RTC.RDAYAR)                             | 208 |

|   |     | 7.2.14 | Month alarm register (RTC.RMONAR)                           | 210 |

|   |     | 7.2.15 | RTC control register 1 (RTC.RCR1)                           | 212 |

|   |     | 7.2.16 | RTC control register 2 (RTC.RCR2)                           | 215 |

- 477 -

#### PRELIMINARY DATA

|   | 7.3 | Opera  | Operation                                                                                        |     |  |

|---|-----|--------|--------------------------------------------------------------------------------------------------|-----|--|

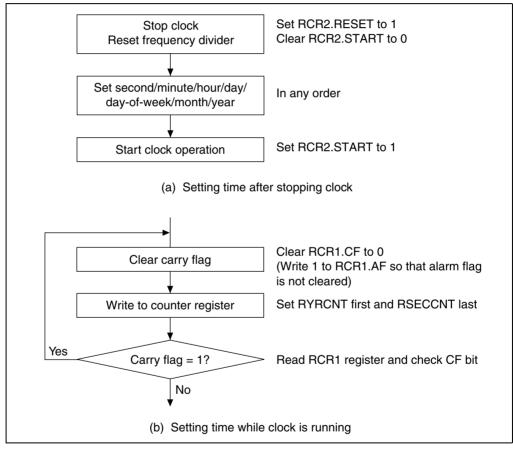

|   |     | 7.3.1  | Time setting procedures                                                                          | 219 |  |

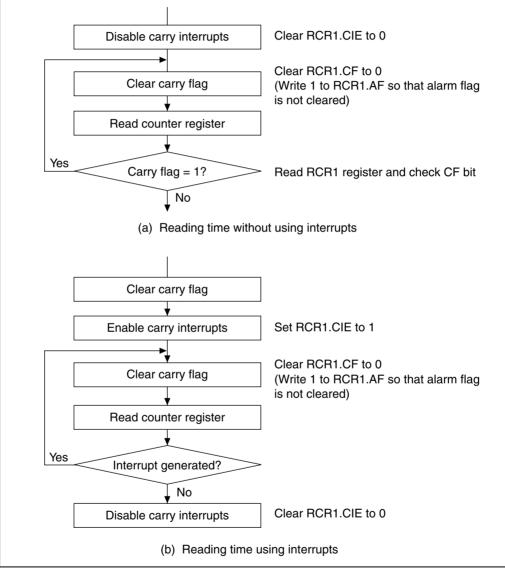

|   |     | 7.3.2  | Time reading procedures                                                                          | 221 |  |

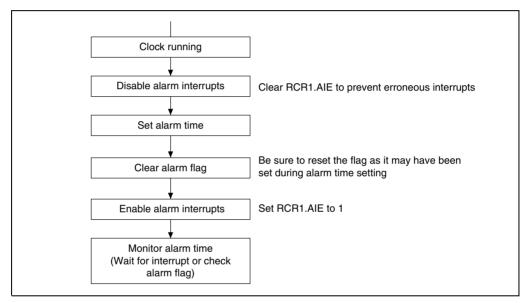

|   |     | 7.3.3  | Alarm function                                                                                   | 222 |  |

|   | 7.4 | Intern | rupts                                                                                            | 223 |  |

|   | 7.5 | Usage  | e notes                                                                                          | 223 |  |

|   |     | 7.5.1  | Register initialization                                                                          | 223 |  |

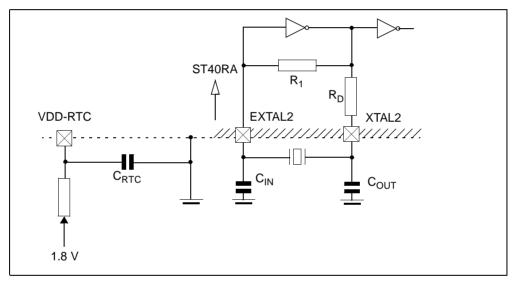

|   |     | 7.5.2  | Crystal oscillator circuit                                                                       | 224 |  |

| 8 | Tim | ner un | it (TMU)                                                                                         | 227 |  |

|   | 8.1 | Overv  | view                                                                                             | 227 |  |

|   |     | 8.1.1  | Features                                                                                         | 227 |  |

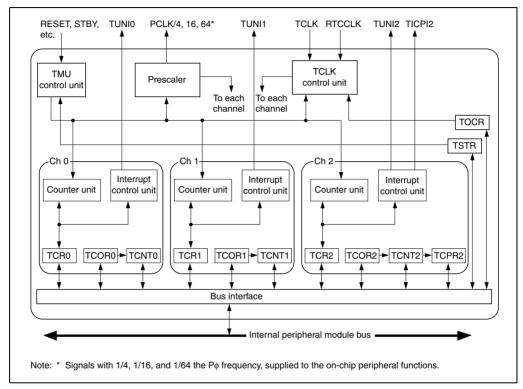

|   |     | 8.1.2  | Block diagram                                                                                    | 229 |  |

|   |     | 8.1.3  | Pin configuration                                                                                | 229 |  |

|   |     | 8.1.4  | Register configuration                                                                           | 230 |  |

|   | 8.2 | Regis  | ter descriptions                                                                                 | 232 |  |

|   |     | 8.2.1  | Timer output control register (TMU.TOCR)                                                         | 232 |  |

|   |     | 8.2.2  | Timer start register (TMU.TSTR)                                                                  | 233 |  |

|   |     | 8.2.3  | Timer constant registers (TMU.TCOR)                                                              | 234 |  |

|   |     | 8.2.4  | Timer counters (TMU.TCNT)                                                                        | 235 |  |

|   |     | 8.2.5  | Timer control registers (TMU.TCR)                                                                | 236 |  |

|   |     | 8.2.6  | Input capture register (TMU.TCPR2)                                                               | 243 |  |

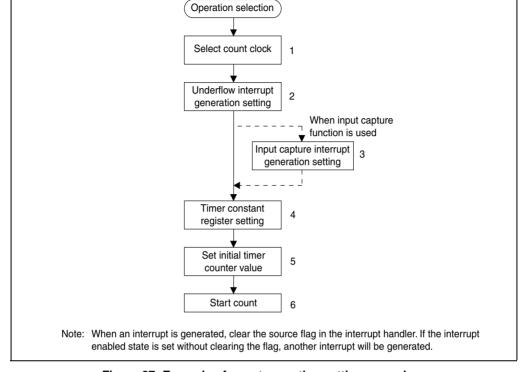

|   | 8.3 | Opera  | ation                                                                                            | 244 |  |

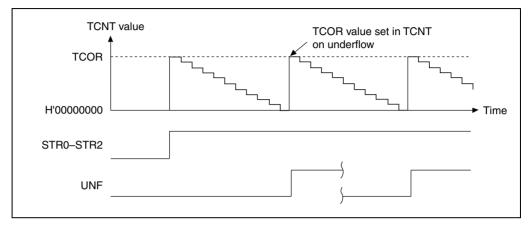

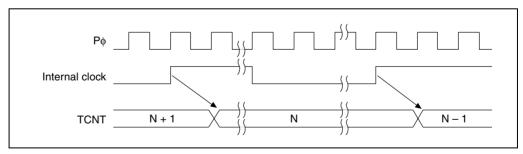

|   |     | 8.3.1  | Counter operation                                                                                | 244 |  |

|   |     |        | Example of count operation setting procedure<br>Auto-reload count operation<br>TCNT count timing |     |  |

|   |     | 8.3.2  | Input capture function                                                                           | 248 |  |

|   | 8.4 | Interi | rupts                                                                                            | 249 |  |

|   | 8.5 |        | e notes                                                                                          | 250 |  |

|   |     | 8.5.1  | Register writes                                                                                  | 250 |  |

|   |     | 8.5.2  | TCNT register reads                                                                              | 250 |  |

|   |     |        |                                                                                                  |     |  |

STMicroelectronics SH-4, ST40 System Architecture, Volume 1: System

- // -

|     | 8.5.4     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

|-----|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|     |           | External clock frequency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 250 |

| 9 S | erial con | nmunication interface with FIFO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

|     | (SC       | CIF)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 251 |

| 9.  | 1 Overv   | iew                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 251 |

|     | 9.1.1     | Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 251 |

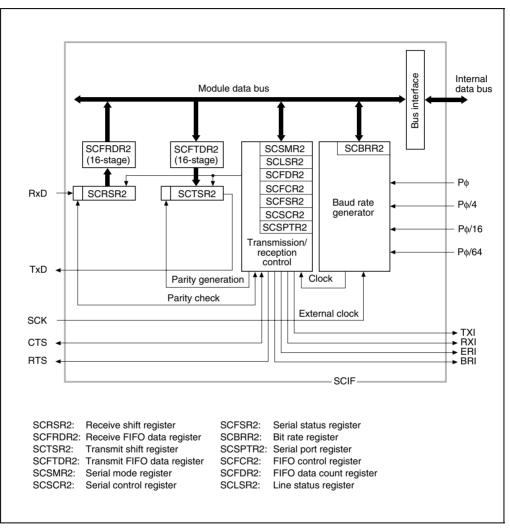

|     | 9.1.2     | Block diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 253 |

|     | 9.1.3     | Pin configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 254 |

|     | 9.1.4     | Register configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 255 |

| 9.  | 2 Regist  | er descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 256 |

|     | 9.2.1     | Receive shift register (SCIF.SCRSR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 256 |

|     | 9.2.2     | Receive FIFO data register (SCIF.SCFRDR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 256 |

|     | 9.2.3     | Transmit shift register (SCIF.SCTSR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 257 |

|     | 9.2.4     | Transmit FIFO data register (SCIF.SCFTDR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 258 |

|     | 9.2.5     | Serial mode register (SCIF.SCSMR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 259 |

|     | 9.2.6     | Bits 15 to 7: reserved<br>Bit 6: character length (CHR)<br>Bit 5: parity enable (PE)<br>Bit 4: parity mode (O/E)<br>Bit 3: stop bit length (STOP)<br>Bit 2: reserved<br>Bits 1 and 0: clock select 1 and 0 (CKS1, CKS0)<br>Serial control register (SCIF.SCSCR)<br>Bits 15 to 8 and 2: reserved<br>Bit 7: transmit interrupt enable (TIE)<br>Bit 6: receive interrupt enable (RIE)<br>Bit 5: transmit enable (TE)<br>Bit 4: receive enable (RE)<br>Bit 3: receive error interrupt enable (REIE)<br>Bit 2: reserved | 264 |

|     | 9.2.7     | Clock enable (CKE0 and CKE1)<br>Serial status register (SCIF.SCFSR)<br>Bits 15 to 12: number of parity errors (PER3 to I<br>Bits 11 to 8: number of framing errors (FER3 to                                                                                                                                                                                                                                                                                                                                        |     |

xiv

- 477 ------

|     |        | Bit 6: transmit end (TEND)                                              |     |

|-----|--------|-------------------------------------------------------------------------|-----|

|     |        | Bit 5: transmit-FIFO-data-empty (TDFE)                                  |     |

|     |        | Bit 4: break detect (BRK)                                               |     |

|     |        | Bit 3: framing error (FER)                                              |     |

|     |        | Bit 2: parity error (PER)                                               |     |

|     |        | Bit 1: receive-FIFO-data-full (RDF)                                     |     |

|     |        | Bit 0: receive data ready (DR)                                          |     |

|     | 9.2.8  | Bit rate register (SCIF.SCBRR)                                          | 282 |

|     | 9.2.9  | FIFO control register (SCIF.SCFCR)                                      | 284 |

|     |        | Bits 15 to 11: reserved                                                 |     |

|     |        | Bits 10, 9 and 8: RTS output active trigger (RSTRG2, RSTRG1 and RSTRG0) |     |

|     |        | Bits 7 and 6: receive FIFO data number trigger (RTRG1, RTRG0)           |     |

|     |        | Bits 5 and 4: transmit FIFO data number trigger<br>(TTRG1, TTRG0)       |     |

|     |        | Bit 3: modem control enable (MCE)                                       |     |

|     |        | Bit 2: transmit FIFO data register reset (TFRST)                        | J   |

|     |        | Bit 1: receive FIFO data register reset (RFRST)                         |     |

|     |        | Bit 0: loopback test (LOOP)                                             |     |

|     | 9.2.10 | FIFO data count register (SCIF.SCFDR)                                   | 291 |

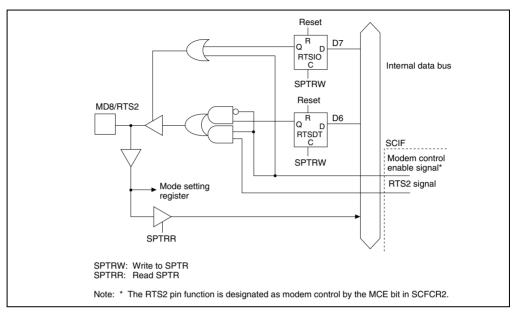

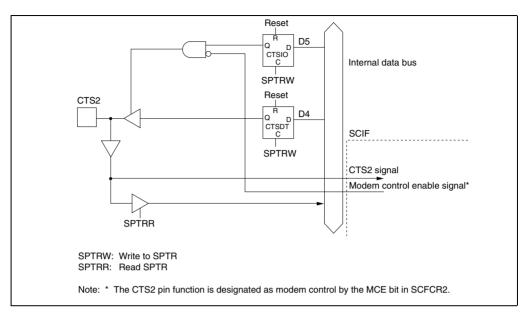

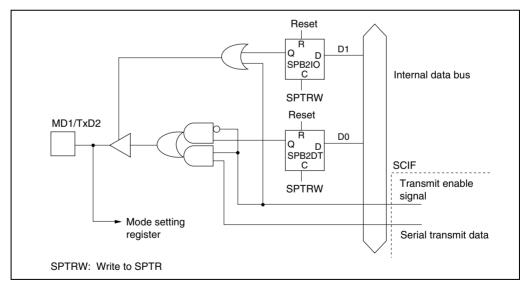

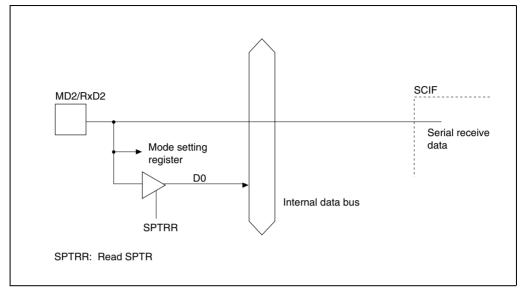

|     | 9.2.11 | Serial port register (SCIF.SCSPTR)                                      | 293 |

|     |        | Bits 15 to 8: reserved                                                  |     |

|     |        | Bit 7: serial port RTS port I/O (RTSIO)                                 |     |

|     |        | Bit 6: serial port RTS port data (RTSDT)                                |     |

|     |        | Bit 5: serial port CTS port I/O (CTSIO)                                 |     |

|     |        | Bit 4: serial port CTS port data (CTSDT)                                |     |

|     |        | Bit 3: serial port clock port data (SCKIO)                              |     |

|     |        | Bit 2: serial port clock port data (SCKDT)                              |     |

|     |        | Bit 1: serial port break I/O (SPB2IO)                                   |     |

|     |        | Bit 0: serial port break data (SPB2DT)                                  |     |

|     | 9.2.12 | Line status register (SCIF.SCLSR)                                       | 301 |

|     |        | Bits 15 to 1: reserved                                                  |     |

|     |        | Bit 0: overrun error (ORER)                                             |     |

| 9.3 | Opera  | tion                                                                    | 303 |

|     | 9.3.1  | Overview                                                                | 303 |

|     | 9.3.2  | Serial operation                                                        | 305 |

|     |        | Data transfer format                                                    |     |

|     |        | Clock                                                                   |     |

|     |        | Data transfer operations                                                |     |

- // -

ADCS 7153464G

STMicroelectronics SH-4, ST40 System Architecture, Volume 1: System

#### PRELIMINARY DATA

|    |      |             | Serial data reception                                                                                                                      |          |

|----|------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------|----------|

|    | 9.4  | SCIF        | interrupt sources and the DMAC                                                                                                             | 315      |

|    | 9.5  | Usage notes |                                                                                                                                            | 316      |

|    |      | 9.5.1       | SCIF.SCFTDR writing and the TDFE flag                                                                                                      | 316      |

|    |      | 9.5.2       | SCIF.SCFRDR reading and the RDF flag                                                                                                       | 317      |

|    |      | 9.5.3       | Break detection and processing                                                                                                             | 317      |

|    |      | 9.5.4       | Sending a break signal                                                                                                                     | 317      |

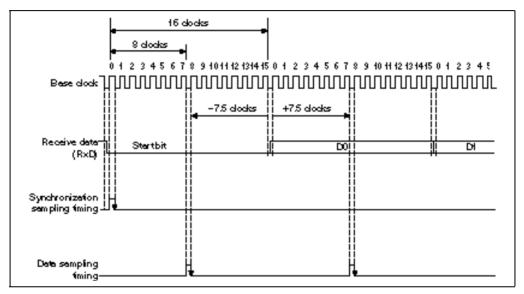

|    |      | 9.5.5       | Receive data sampling timing and receive margin                                                                                            | 318      |

|    |      | 9.5.6       | SCK/MRESET                                                                                                                                 | 319      |

|    |      | 9.5.7       | When using the DMAC                                                                                                                        | 319      |

|    |      | 9.5.8       | Serial ports                                                                                                                               | 319      |

| 10 | Usei | r brea      | k controller (UBC)                                                                                                                         | 321      |

|    | 10.1 | Overv       | iew                                                                                                                                        | 321      |

|    |      | 10.1.1      | Features                                                                                                                                   | 321      |

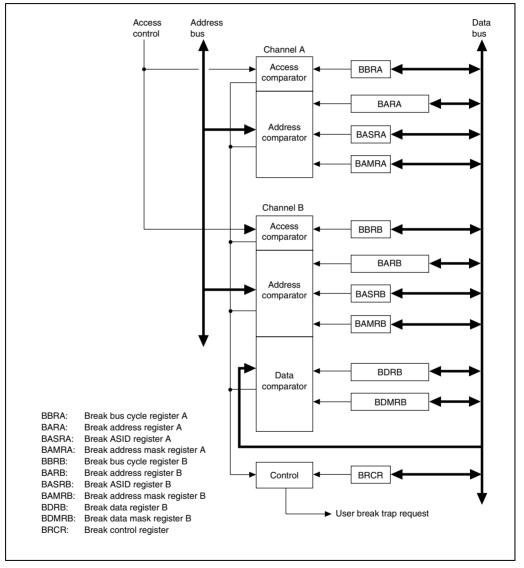

|    |      | 10.1.2      | Block diagram                                                                                                                              | 323      |

|    | 10.2 | Regist      | er overview                                                                                                                                | 324      |

|    | 10.3 | Regist      | er descriptions                                                                                                                            | 327      |

|    |      | 10.3.1      | Access to UBC control registers                                                                                                            | 327      |

|    |      | 10.3.2      | Break address register A (UBC.BARA)                                                                                                        | 328      |

|    |      |             | Bits 31 to 0: break address A31 to A0 (BAA31 t                                                                                             | to BAA0) |

|    |      | 10.3.3      | Break ASID register A (UBC.BASRA)                                                                                                          | 329      |

|    |      |             | Bits 7 to 0: break ASID A7 to A0 (BASA7 to BA                                                                                              | ASA0)    |

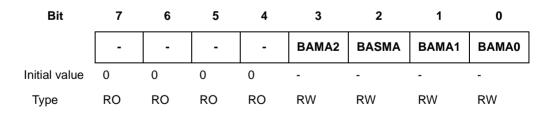

|    |      | 10.3.4      | Break address mask register A (UBC.BAMRA)                                                                                                  | 329      |

|    |      |             | Bits 7 to 4: reserved<br>Bit 2: break ASID mask A (BASMA):<br>Bits 3, 1, and 0: break address mask A2 to A0<br>(BAMA2 to BAMA0):           |          |

|    |      | 10.3.5      | Break bus cycle register A (UBC.BBRA)                                                                                                      | 331      |

|    |      |             | Bits 15 to 7: reserved<br>Bits 5 and 4: instruction access/operand access<br>(IDA1, IDA0):<br>Bits 3 and 2: read/write select A (RWA1, RWA |          |

|    |      |             | Bits 6, 1, and 0: operand size select A (SZA2 to                                                                                           |          |

- 477 -

#### **PRELIMINARY DATA**

|      | 10.3.6  | Break address register B (UBC.BARB)                                                                                                                           | 333  |

|------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

|      | 10.3.7  | Break ASID register B (UBC.BASRB)                                                                                                                             | 333  |

|      | 10.3.8  | Break address mask register B (UBC.BAMRB)                                                                                                                     | 333  |

|      | 10.3.9  | Break data register B (UBC.BDRB)                                                                                                                              | 334  |

|      |         | Bits 31 to 0: break data B31 to B0 (BDB31 to BD                                                                                                               | B0): |

|      | 10.3.10 | Break data mask register B (UBC.BDMRB)                                                                                                                        | 335  |

|      |         | Bits 31 to 0: break data mask B31 to B0<br>(BDMB31 to BDMB0)                                                                                                  |      |

|      | 10.3.11 | Break bus cycle register B (UBC.BBRB)                                                                                                                         | 336  |

|      | 10.3.12 | Break control register (UBC.BRCR)                                                                                                                             | 337  |

|      |         | Bit 15: condition match flag A (CMFA)<br>Bit 14: condition match flag B (CMFB)<br>Bits 13 to 11: reserved<br>Bit 10: instruction access break select A (PCBA) |      |

|      |         | Bits 9 and 8: reserved                                                                                                                                        |      |

|      |         | Bit 7: data break enable B (DBEB)                                                                                                                             |      |

|      |         | Bit 6: PC break select B (PCBB)<br>Bits 5 and 4: reserved                                                                                                     |      |

|      |         | Bit 3: sequence condition select (SEQ)                                                                                                                        |      |

|      |         | Bits 2 and 1: reserved                                                                                                                                        |      |

|      |         | Bit 0: user break debug enable (UBDE)                                                                                                                         |      |

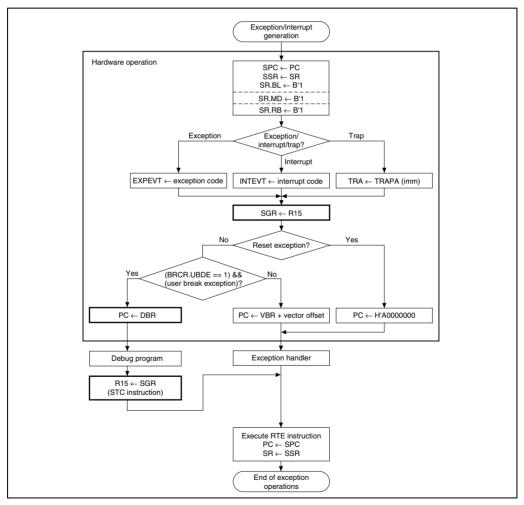

| 10.4 | Operat  | ion                                                                                                                                                           | 341  |

|      | 10.4.1  | Explanation of terms relating to accesses                                                                                                                     | 341  |

|      | 10.4.2  | Explanation of terms relating to instruction intervals                                                                                                        | 341  |

|      |         | Example of sequence of instructions with no bran<br>Example of sequence of instructions with a branc                                                          |      |

|      | 10.4.3  | User break operation sequence                                                                                                                                 | 342  |

|      | 10.4.4  | Instruction access cycle break                                                                                                                                | 344  |

|      | 10.4.5  | Operand access cycle break                                                                                                                                    | 345  |

|      | 10.4.6  | Condition match flag setting                                                                                                                                  | 346  |

|      |         | Instruction access with post-execution condition,<br>operand access<br>Instruction access with pre-execution condition                                        | or   |

|      | 10.4.7  | Program counter (PC) value saved                                                                                                                              | 347  |

|      | 10.4.8  | Contiguous A and B settings for sequential conditions                                                                                                         |      |

|      | 20110   | Instruction access matches on both channel A and<br>channel B<br>Instruction access match on channel A, operand a                                             | đ    |

STMicroelectronics SH-4, ST40 System Architecture, Volume 1: System

- // -

|    |                            |                       | match on channel B<br>Operand access match on channel A, instruction         | n 200055  |

|----|----------------------------|-----------------------|------------------------------------------------------------------------------|-----------|

|    |                            |                       | match on channel B                                                           | ll access |

|    |                            |                       | Operand access matches on both channel A and                                 | channel B |

|    | 10.5                       | Usage                 | notes                                                                        | 350       |

|    | 10.6                       | User b                | User break debug support function                                            |           |

|    | 10.7                       | Exam                  | ples of use                                                                  | 353       |

|    |                            | 10.7.1                | Instruction access cycle break condition settings                            | 353       |

|    |                            |                       | Independent channel A channel B mode: user b interrupt generated             | reak      |

|    |                            |                       | Channel A channel B sequential mode: user bre<br>interrupt generated         | eak       |

|    |                            |                       | Independent channel A channel B mode: user b<br>interrupts not generated     | reak      |

|    |                            | 10.7.2                | Operand access cycle break condition settings                                | 356       |

|    |                            | 10.7.3                | User break controller stop function                                          | 358       |

|    |                            | 10.7.4                | Transition to user break controller stopped state                            | 358       |

|    |                            | 10.7.5                | Cancelling the user break controller stopped state                           | 359       |

|    |                            | 10.7.6                | Examples of stopping and restarting the user break controller                | 359       |

| 11 | User debug interface (UDI) |                       |                                                                              | 361       |

|    | 11.1                       | Overv                 | iew                                                                          | 361       |

|    |                            | 11.1.1                | Features                                                                     | 361       |

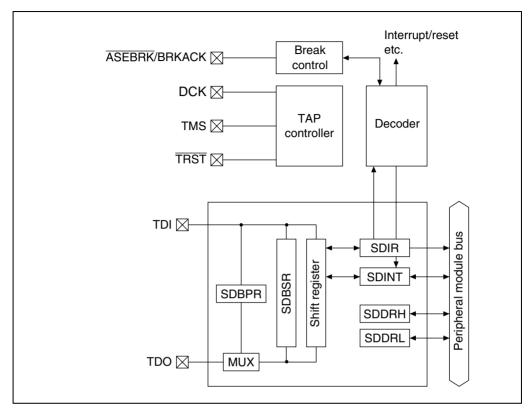

|    |                            | 11.1.2                | Block diagram                                                                | 361       |

|    |                            | 11.1.3                | Pin configuration                                                            | 363       |

|    |                            | 11.1.4                | Register configuration                                                       | 364       |

|    | 11.2                       | Register descriptions |                                                                              | 367       |

|    |                            | 11.2.1                | Instruction register (SDIR)                                                  | 367       |

|    |                            |                       | Bits 15 to 8:<br>Test instruction bits (TI7 to TI0)<br>Bits 7 to 0: reserved |           |

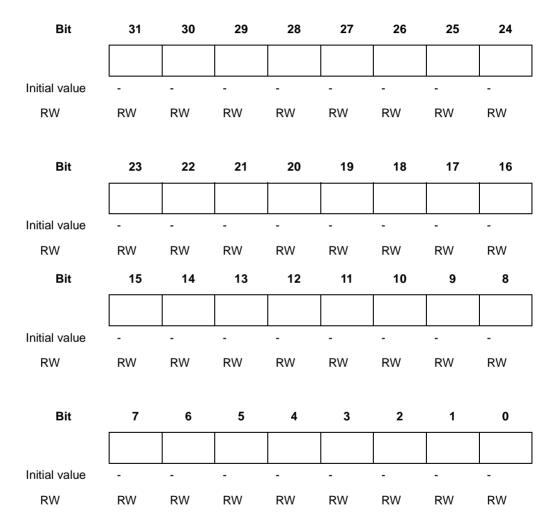

|    |                            | 11.2.2                | Data register (SDDR)                                                         | 370       |

|    |                            |                       | Bits 31 to 0: D                                                              | R Data    |

|    |                            | 11.2.3                | Bypass register (SDBPR)                                                      | 371       |

|    |                            |                       |                                                                              |           |

xviii

- 477 -

#### PRELIMINARY DATA

|    |      | 11.2.4           | Interrupt factor register (SDINT)<br>Bits 15 to 1: reserved<br>Bit 0: interrupt request bit (INTREQ) | 371          |

|----|------|------------------|------------------------------------------------------------------------------------------------------|--------------|

|    |      | 11.2.5           | Brown Brown Berner (SDBSR)                                                                           | 372          |

|    | 11.3 |                  |                                                                                                      | 372          |

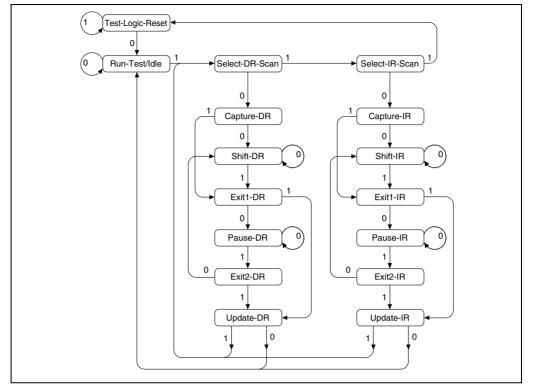

|    | 11.0 | 11.3.1           | TAP control                                                                                          | 372          |

|    |      | 11.3.1           |                                                                                                      | 372          |

|    |      | 11.3.2           |                                                                                                      | 373          |

|    |      | 11.3.4           | Bypass                                                                                               | 374          |

|    |      | 11.3.4           | Boundary scan (EXTEST, SAMPLE/RELOAD)                                                                | 374          |

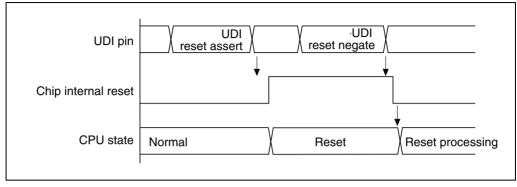

|    | 11.4 | Usage            |                                                                                                      | 375          |

|    |      | 11.4.1           | SDIR command                                                                                         | 375          |

|    |      | 11.4.1           |                                                                                                      | 375          |

|    |      | 11.4.2           | Emulator                                                                                             | 375          |

|    |      | 111110           |                                                                                                      | 010          |

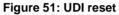

| 12 | Adv  | anced            | l user debugger (AUD)                                                                                | 377          |

|    | 12.1 | Overv            | iew                                                                                                  | 377          |

|    |      | 12.1.1           | Features                                                                                             | 377          |

|    |      | 12.1.2           | Block diagram                                                                                        | 378          |

|    | 12.2 | AUD i            | nterface pins                                                                                        | 379          |

|    | 12.3 | Register summary |                                                                                                      | 380          |

|    |      | U                | 5                                                                                                    |              |

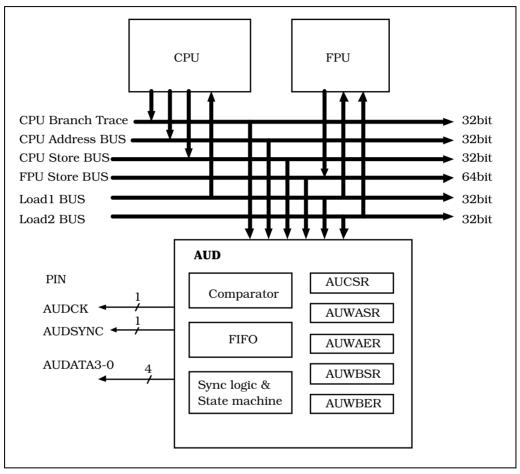

| 13 | ASE  | hard             | ware break controller                                                                                | 381          |

|    | 13.1 | Overview         |                                                                                                      | 381          |

|    |      | 13.1.1           | Features                                                                                             | 381          |

|    |      | 13.1.2           | Differences between the user break controller an hardware break controller                           | d ASE<br>382 |

|    |      | 13.1.3           | Block diagram                                                                                        | 383          |

|    | 13.2 |                  | <b>U</b>                                                                                             | 384          |

|    | 10.4 | Register summary |                                                                                                      | 504          |

- // -

xix

### Appendices

| Α | ST40 system architectural conventions |              |                                  | 389 |

|---|---------------------------------------|--------------|----------------------------------|-----|

|   | A.1                                   | Introduction |                                  | 389 |

|   |                                       | A.1.1        | Memory blocks                    | 389 |

|   |                                       | A.1.2        | Control registers                | 390 |

|   |                                       |              | Register conventions             |     |

|   |                                       |              | Field conventions                |     |

|   |                                       |              | Control register layout          |     |

|   |                                       | A.1.3        | Version control registers        | 394 |

|   |                                       | A.1.4        | P-ERROR flags                    | 397 |

|   |                                       | A.1.5        | M-ERROR flags                    | 401 |

|   |                                       | A.1.6        | Memory map conventions           | 401 |

|   |                                       | A.1.7        | P-MODULE specification standards | 402 |

| B | Register address list                 |              | 403                              |     |

|   | Ind                                   | ex           |                                  | 417 |

# **Preface**

This document is part of the SuperH Documentation Suite detailed below. Comments on this or other manuals in the SuperH Documentation Suite should be made by contacting your local STMicroelectronics Limited Sales Office or distributor.

## **Document identification and control**

Each book carries a unique identifier in the form:

ADCS nnnnnnx

**Where**, nnnnnn is the document number and x is the revision.

Whenever making comments on a document the complete identification ADCS nnnnnnx should be quoted.

## **ST40 documentation suite**

The ST40 documentation suite comprises the following volumes:

#### ST40 Micro Toolset User's Guide

*ADCS 7379953.* This manual provides an introduction to the ST40 Micro Toolset and instructions for getting a simple OS21 application run on an STMicroelectronics' MediaRef platform. It also describes how to boot OS21 applications from ROM and how to port applications which use STMicroelectronics' STLite/OS20 operating systems to OS21.

- 77 -

STMicroelectronics

SH-4, ST40 System Architecture, Volume 1: System

#### **OS21 User's Manual**

*ADCS 7358306*. This manual describes the generic use of OS21 across supported platforms. It describes all the core features of OS21and their use and details the OS21 function definitions. It also explains how OS21 differs to STLite/OS20, the API targeted at ST20.

#### **OS21 for ST40 User Manual**

*ADCS 7358673.* This manual describes the use of OS21 on ST40 platforms. It describes how specific ST40 facilities are exploited by the OS21 API. It also describes the OS21 board support packages for ST40 platforms.

#### 32-Bit RISC Series, SH-4 CPU Core Architecture

*ADCS 7182230*. This manual describes the architecture and instruction set of the SH4-1xx (previously known a ST40-C200) core as used by STMicroelectronics.

#### 32-Bit RISC Series, SH-4, ST40 System Architecture

This manual describes the ST40 family system architecture. It is split into four volumes:

ST40 System Architecture - Volume 1 System - ADCS 7153464.

ST40 System Architecture - Volume 2 Bus Interfaces - ADCS 7171720.

ST40 System Architecture - Volume 3 Video Devices - ADCS 7225754.

ST40 System Architecture - Volume 4 I/O Devices - ADCS 7225754.

## **Conventions used in this guide**

#### **General notation**

The notation in this document uses the following conventions:

- Sample code, keyboard input and file names,

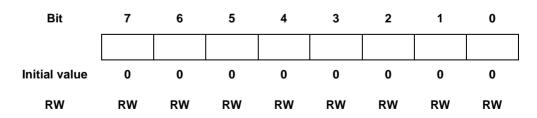

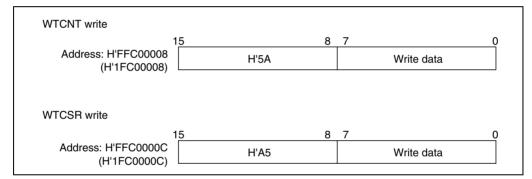

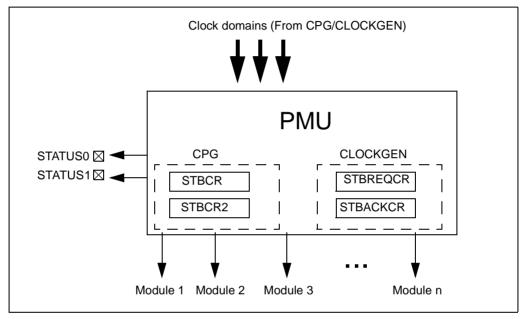

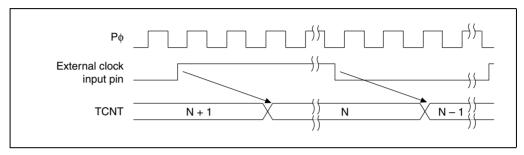

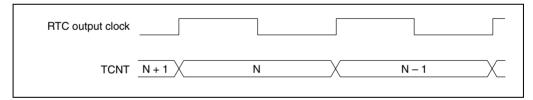

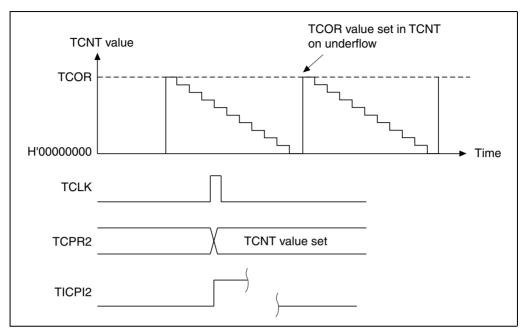

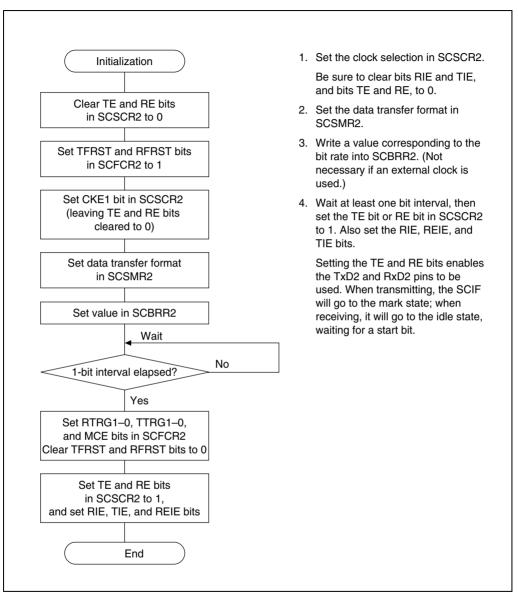

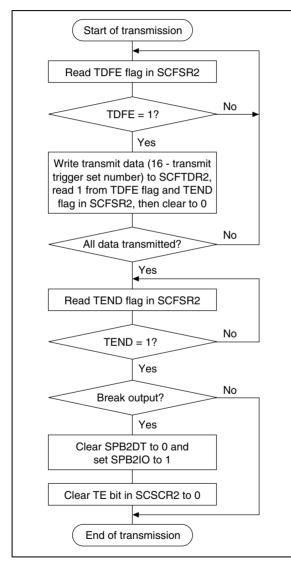

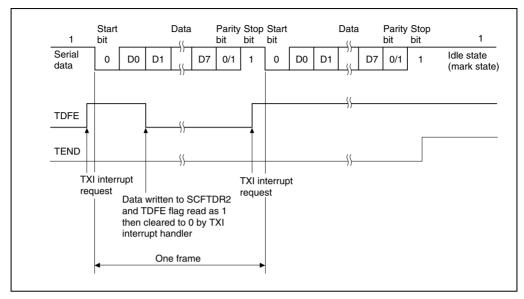

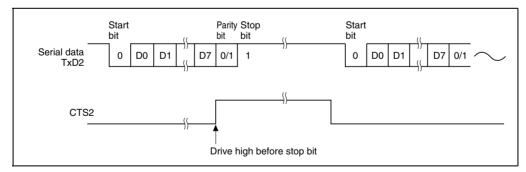

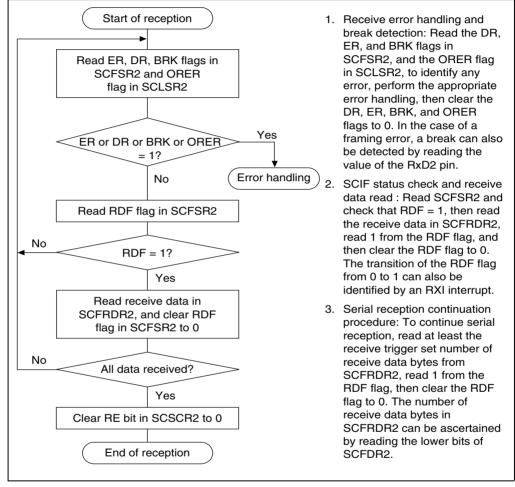

- Variables and code variables,