# Intel<sup>®</sup> Stratix<sup>®</sup> 10 H-Tile/L-Tile Avalon<sup>®</sup> Memory Mapped (Avalon-MM) Hard IP for PCI Express\* User Guide

Updated for Intel<sup>®</sup> Quartus<sup>®</sup> Prime Design Suite: **19.3**

# Contents

| 1. Intro | oduction                                                                           | 5   |

|----------|------------------------------------------------------------------------------------|-----|

| 1.       | .1. Avalon-MM Interface for PCIe                                                   | . 5 |

| 1.       | .2. Features                                                                       | .6  |

| 1.       | .3. Release Information                                                            | .7  |

| 1.       | .4. Device Family Support                                                          | .8  |

| 1.       | .5. Recommended Speed Grades                                                       | . 9 |

| 1.       | .6. Performance and Resource Utilization                                           | 10  |

| 1.       | .7. Transceiver Tiles                                                              | 10  |

| 1.       | .8. PCI Express IP Core Package Layout                                             | 11  |

| 1.       | .9. Channel Availability                                                           | 15  |

| 2 Quic   | k Start Guide                                                                      | 17  |

| -        | .1. Design Components                                                              |     |

|          | .2. Directory Structure                                                            |     |

|          | .3. Generating the Design Example                                                  |     |

|          |                                                                                    |     |

|          | .4. Simulating the Design Example                                                  |     |

|          | .6. Installing the Linux Kernel Driver                                             |     |

|          | .7. Running the Design Example Application                                         |     |

|          |                                                                                    |     |

| 3. Inter | rface Overview                                                                     | 25  |

| 3.       | .1. Avalon-MM DMA Interfaces when Descriptor Controller Is Internally Instantiated | 25  |

| 3.       | .2. Avalon-MM DMA Interfaces when Descriptor Controller is Externally Instantiated | 29  |

| 3.       | .3. Other Avalon-MM Interfaces                                                     |     |

|          | 3.3.1. Avalon-MM Master Interfaces                                                 |     |

|          | 3.3.2. Avalon-MM Slave Interfaces                                                  | 32  |

|          | 3.3.3. Control Register Access (CRA) Avalon-MM Slave                               |     |

|          | .4. Clocks and Reset                                                               |     |

| 3.       | .5. System Interfaces                                                              | 33  |

| 4. Para  | meters                                                                             | 35  |

| 4.       | .1. Avalon-MM Settings                                                             | 36  |

|          | .2. Base Address Registers                                                         |     |

|          | .3. Device Identification Registers                                                |     |

|          | .4. PCI Express and PCI Capabilities Parameters                                    |     |

|          | 4.4.1. Device Capabilities                                                         |     |

|          | 4.4.2. Link Capabilities                                                           |     |

|          | 4.4.3. MSI and MSI-X Capabilities                                                  |     |

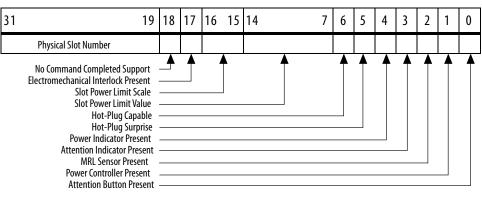

|          | 4.4.4. Slot Capabilities                                                           |     |

|          | 4.4.5. Power Management                                                            |     |

|          | 4.4.6. Vendor Specific Extended Capability (VSEC)                                  |     |

| 4.       | .5. Configuration, Debug and Extension Options                                     |     |

| 4.       | .6. PHY Characteristics                                                            | 43  |

|          | .7. Example Designs                                                                |     |

| 5 Decir  | gning with the IP Core                                                             | 14  |

| _        | .1. Generation                                                                     |     |

|          | .2. Simulation                                                                     |     |

| 5.       | .2. 311101811011                                                                   | 44  |

Contents

| 5.3. IP Core Generation Output (Intel Quartus Prime Pro Edition)                                                                                                                                    | 45                       |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| 5.4. Channel Layout and PLL Usage                                                                                                                                                                   |                          |

| 6. Block Descriptions                                                                                                                                                                               | 54                       |

| 6.1. Interfaces                                                                                                                                                                                     |                          |

| 6.1.1. Intel Stratix 10 DMA Avalon-MM DMA Interface to the Application Laye                                                                                                                         |                          |

| 6.1.2. Avalon-MM Interface to the Application Layer                                                                                                                                                 |                          |

| 6.1.3. Clocks and Reset                                                                                                                                                                             |                          |

| 6.1.4. Interrupts                                                                                                                                                                                   |                          |

| 6.1.5. Flush Requests                                                                                                                                                                               |                          |

| 6.1.6. Serial Data, PIPE, Status, Reconfiguration, and Test Interfaces                                                                                                                              |                          |

|                                                                                                                                                                                                     |                          |

| 7. Registers                                                                                                                                                                                        |                          |

| 7.1. Configuration Space Registers                                                                                                                                                                  |                          |

| 7.1.1. Register Access Definitions                                                                                                                                                                  |                          |

| 7.1.2. PCI Configuration Header Registers                                                                                                                                                           |                          |

| 7.1.3. PCI Express Capability Structures                                                                                                                                                            |                          |

| 7.1.4. Intel Defined VSEC Capability Header                                                                                                                                                         |                          |

| 7.1.5. Uncorrectable Internal Error Status Register                                                                                                                                                 | 92                       |

| 7.1.6. Uncorrectable Internal Error Mask Register                                                                                                                                                   |                          |

| 7.1.7. Correctable Internal Error Status Register                                                                                                                                                   |                          |

| 7.1.8. Correctable Internal Error Mask Register                                                                                                                                                     | 93                       |

| 7.2. Avalon-MM DMA Bridge Registers                                                                                                                                                                 |                          |

| 7.2.1. PCI Express Avalon-MM Bridge Register Address Map                                                                                                                                            |                          |

| 7.2.2. DMA Descriptor Controller Registers                                                                                                                                                          |                          |

| 8. Programming Model for the DMA Descriptor Controller                                                                                                                                              | 105                      |

|                                                                                                                                                                                                     |                          |

|                                                                                                                                                                                                     |                          |

| 8.1. Read DMA Example                                                                                                                                                                               | 107                      |

| 8.1. Read DMA Example                                                                                                                                                                               | 107<br>110               |

| 8.1. Read DMA Example<br>8.2. Write DMA Example<br>8.3. Software Program for Simultaneous Read and Write DMA                                                                                        | 107<br>110<br>113        |

| <ul> <li>8.1. Read DMA Example</li> <li>8.2. Write DMA Example</li> <li>8.3. Software Program for Simultaneous Read and Write DMA</li> <li>8.4. Read DMA and Write DMA Descriptor Format</li> </ul> | 107<br>110<br>113<br>114 |

| <ul> <li>8.1. Read DMA Example</li></ul>                                                                                                                                                            |                          |

| 10.5.3. ebfm_barrd_wait Procedure                                     | 136 |

|-----------------------------------------------------------------------|-----|

| 10.5.4. ebfm_barrd_nowt Procedure                                     | 136 |

| 10.5.5. ebfm_cfgwr_imm_wait Procedure                                 | 137 |

| 10.5.6. ebfm_cfgwr_imm_nowt Procedure                                 | 137 |

| 10.5.7. ebfm_cfgrd_wait Procedure                                     | 138 |

| 10.5.8. ebfm_cfgrd_nowt Procedure                                     | 138 |

| 10.5.9. BFM Configuration Procedures                                  | 139 |

| 10.5.10. BFM Shared Memory Access Procedures                          | 140 |

| 10.5.11. BFM Log and Message Procedures                               | 142 |

| 10.5.12. Verilog HDL Formatting Functions                             | 145 |

| 11. Troubleshooting and Observing the Link                            |     |

| 11.1. Troubleshooting                                                 |     |

| 11.1.1. Simulation Fails To Progress Beyond Polling. Active State     |     |

| 11.1.2. Hardware Bring-Up Issues                                      |     |

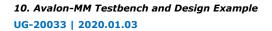

| 11.1.3. Link Training                                                 |     |

| 11.1.4. Use Third-Party PCIe Analyzer                                 |     |

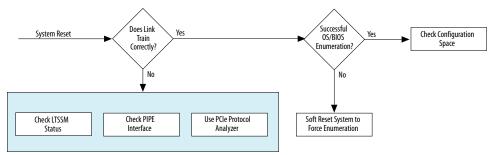

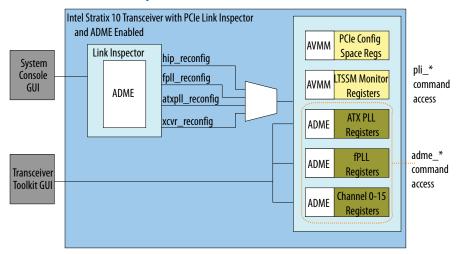

| 11.2. PCIe Link Inspector Overview                                    |     |

| 11.2.1. PCIe Link Inspector Hardware                                  |     |

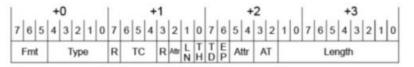

| A. PCI Express Core Architecture                                      |     |

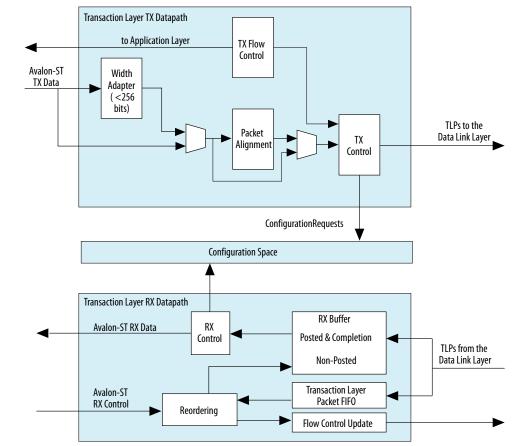

| A.1. Transaction Layer                                                | 166 |

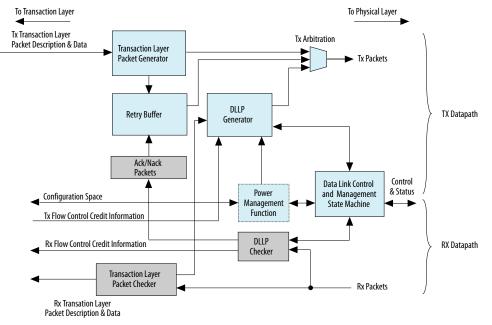

| A.2. Data Link Layer                                                  |     |

| A.3. Physical Layer                                                   |     |

| B. Document Revision History                                          |     |

| B.1. Document Revision History for the Intel Stratix 10               |     |

| Avalon Memory Mapped (Avalon-MM) Hard IP for PCI Express User Guide . | 172 |

# **1. Introduction**

This User Guide is applicable to the H-Tile and L-Tile variants of the  $Intel^{\$}$  Stratix  $^{\$}$  10 devices.

# **1.1. Avalon-MM Interface for PCIe**

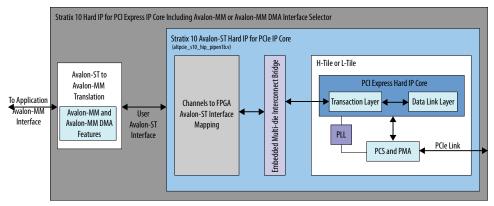

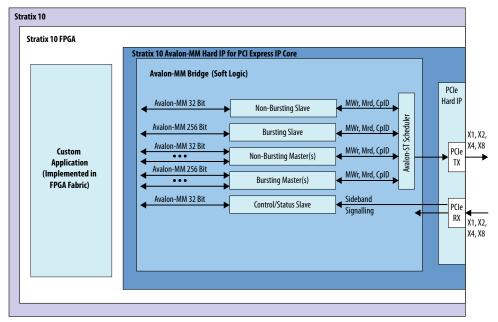

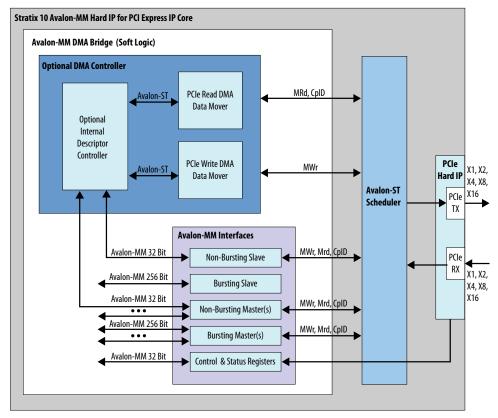

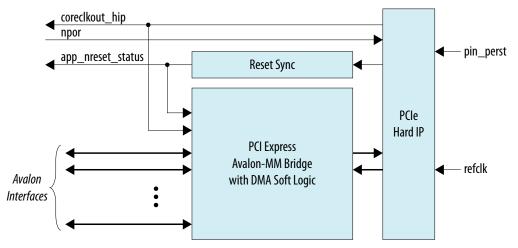

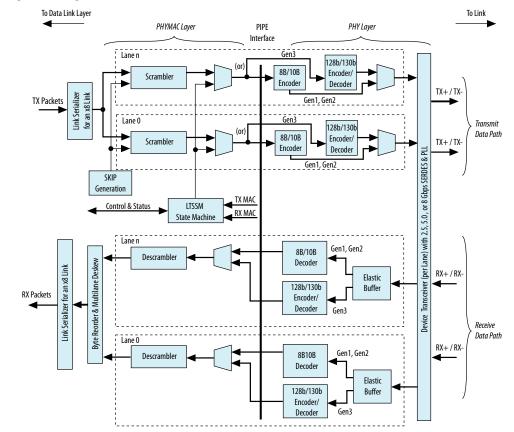

Intel Stratix 10 FPGAs include a configurable, hardened protocol stack for PCI Express\* that is compliant with *PCI Express Base Specification 3.0*. This IP core combines the functionality of previous Avalon<sup>®</sup> Memory-Mapped (Avalon-MM) and Avalon-MM direct memory access (DMA) interfaces. It supports the same functionality for Intel Stratix 10 as the Avalon-MM and Avalon-MM with DMA variants for Arria<sup>®</sup> 10 devices.

The Hard IP for PCI Express IP core using the Avalon-MM interface removes many of the complexities associated with the PCIe protocol. It handles all of the Transaction Layer Packet (TLP) encoding and decoding, simplifying the design task. This IP core also includes optional Read and Write Data Mover modules facilitating the creation of high-performance DMA designs. Both the Avalon-MM interface and the Read and Write Data Mover modules are implemented in soft logic.

The Avalon-MM Intel Stratix 10 Hard IP for PCI Express IP Core supports Gen1, Gen2 and Gen3 data rates and x1, x2, x4, and x8 configurations. Gen1 and Gen2 data rates are also supported with the x16 configuration.

*Note:* The Gen3 x16 configuration is supported by another IP core, the Avalon-MM Intel Stratix 10 Hard IP+ core. For details, refer to the *Avalon-MM Intel Stratix 10 Hard IP*+ *for PCIe*\* *Solutions User Guide*.

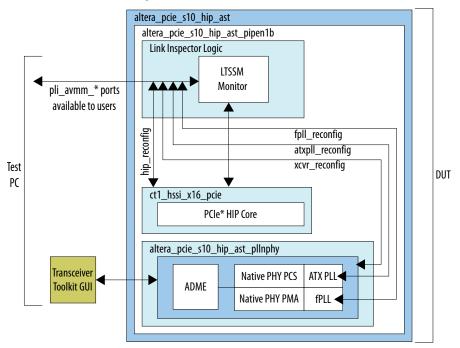

#### Figure 1. Intel Stratix 10 PCIe IP Core Variant with Avalon-MM Interface

Intel Corporation. All rights reserved. Agilex, Altera, Arria, Cyclone, Enpirion, Intel, the Intel logo, MAX, Nios, Quartus and Stratix words and logos are trademarks of Intel Corporation or its subsidiaries in the U.S. and/or other countries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services. \*Other names and brands may be claimed as the property of others.

#### Table 1. **PCI Express Data Throughput**

The following table shows the theoretical link bandwidth of a PCI Express link for Gen1, Gen2, and Gen3 for 1, 2, 4, 8, and 16 lanes excluding overhead. This table provides bandwidths for a single transmit (TX) or receive (RX) channel. The numbers double for duplex operation. The protocol specifies 2.5 giga-transfers per second (GT/s) for Gen1, 5.0 GT/s for Gen2, and 8.0 GT/s for Gen3. Gen1 and Gen2 use 8B/10B encoding which introduces a 20% overhead. Gen3 uses 128b/130b encoding which an overhead of 1.54%. The following table shows the actual usable data bandwidth in gigabytes per second (GBps). The encoding and decoding overhead has been removed.

|                             |      | Link Width      |      |    |                                  |  |  |  |

|-----------------------------|------|-----------------|------|----|----------------------------------|--|--|--|

|                             | ×1   | ×1 ×2 ×4 ×8 ×16 |      |    |                                  |  |  |  |

| PCI Express Gen1 (2.5 Gbps) | 2    | 4               | 8    | 16 | 32                               |  |  |  |

| PCI Express Gen2 (5.0 Gbps) | 4    | 8               | 16   | 32 | 64                               |  |  |  |

| PCI Express Gen3 (8.0 Gbps) | 7.87 | 15.75           | 31.5 | 63 | Not available in current release |  |  |  |

#### **Related Information**

- Creating a System with Platform Designer

- PCI Express Base Specification 3.0

- Avalon-MM Intel Stratix 10 Hard IP+ for PCIe\* Solutions User Guide

#### 1.2. Features

New features in the Intel Quartus® Prime Pro Edition Software:

- Support for Programmer Object File (\*.pof) generation for up to Gen3 x8 variants.

- Support for a PCIe\* Link Inspector including the following features:

- Read and write access to the Configuration Space registers.

- LTSSM monitoring.

- PLL lock and calibration status monitoring.

- Read and write access to PCS and PMA registers.

- Software application for Linux demonstrating PCIe accesses in hardware with dynamically generated design examples

- Support for instantiation as a stand-alone IP core from the Intel Quartus Prime Pro Edition IP Catalog, as well as Platform Designer instantiation.

The Avalon-MM Stratix 10 Hard IP for PCI Express IP Core supports the following features:

- A migration path for Avalon-MM or Avalon-MM DMA implemented in earlier device families.

- Standard Avalon-MM master and slave interfaces:

- High throughput bursting Avalon-MM slave with optional address mapping.

- Avalon-MM slave with byte granularity enable support for single DWORD ports and DWORD granularity enable support for high throughput ports.

- Up to 6 Avalon-MM masters associated to 1 or more BARs with byte enable support.

- High performance, bursting Avalon-MM master ports.

- Optional DMA data mover with high throughput, bursting, Avalon-MM master:

- Write Data Mover moves data to PCIe system memory using PCIe Memory Write (MemWr) Transaction Layer Packets (TLPs).

- Read Data Mover moves data to local memory using PCIe Memory Read (MemRd) TLPs.

- Modular implementation to select the required features for a specific application:

- Simultaneous support for DMA modules and high throughput Avalon-MM slaves and masters.

- Avalon-MM slave to easily access the entire PCIe address space without requiring any PCI Express specific knowledge.

- Support for 256-bit and 64-bit application interface widths.

- Advanced Error Reporting (AER): In Intel Stratix 10 devices, Advanced Error Reporting is always enabled in the PCIe Hard IP for both the L and H transceiver tiles.

- Available in both Intel Quartus Prime Pro Edition and Platform Designer IP Catalogs.

- Optional internal DMA Descriptor controller.

- Autonomous Hard IP mode, allowing the PCIe IP core to begin operation before the FPGA fabric is programmed. This mode is enabled by default. It cannot be disabled.

- Operates at up to 250 MHz in -2 speed grade device.

- *Note:* For a detailed understanding of the PCIe protocol, please refer to the *PCI Express Base Specification.*

# **1.3. Release Information**

#### Table 2. Hard IP for PCI Express Release Information

| Item                                                  | Description                  |  |  |

|-------------------------------------------------------|------------------------------|--|--|

| Version Intel Quartus Prime Pro Edition 18.0 Software |                              |  |  |

| Release Date                                          | May 2018                     |  |  |

| Ordering Codes                                        | No ordering code is required |  |  |

Intel verifies that the current version of the Intel Quartus Prime Pro Edition software compiles the previous version of each IP core, if this IP core was included in the previous release. Intel reports any exceptions to this verification in the Intel IP Release Notes or clarifies them in the Intel Quartus Prime Pro Edition IP Update tool. Intel does not verify compilation with IP core versions older than the previous release.

#### **Related Information**

#### **Timing and Power Models**

Reports the default device support levels in the current version of the Quartus Prime Pro Edition software.

## 1.4. Device Family Support

The following terms define device support levels for Intel FPGA IP cores:

- Advance support—the IP core is available for simulation and compilation for this device family. Timing models include initial engineering estimates of delays based on early post-layout information. The timing models are subject to change as silicon testing improves the correlation between the actual silicon and the timing models. You can use this IP core for system architecture and resource utilization studies, simulation, pinout, system latency assessments, basic timing assessments (pipeline budgeting), and I/O transfer strategy (data-path width, burst depth, I/O standards tradeoffs).

- **Preliminary support**—the IP core is verified with preliminary timing models for this device family. The IP core meets all functional requirements, but might still be undergoing timing analysis for the device family. It can be used in production designs with caution.

- **Final support**—the IP core is verified with final timing models for this device family. The IP core meets all functional and timing requirements for the device family and can be used in production designs.

#### Table 3. **Device Family Support**

| Device Family         | Support Level                                                                                                                                  |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| Intel Stratix 10      | Preliminary support.                                                                                                                           |

| Other device families | No support.<br>Refer to the <i>Intel PCI Express Solutions</i> web page on the Intel website for support information on other device families. |

#### **Related Information**

PCI Express Solutions Web Page

# **1.5. Recommended Speed Grades**

# Table 4.Intel Stratix 10 Recommended Speed Grades for All Avalon-MM with DMA<br/>Widths and Frequencies

| Lane Rate | Lane Rate Link Width Inte |          | Application Clock<br>Frequency (MHz) | Recommended Speed<br>Grades |

|-----------|---------------------------|----------|--------------------------------------|-----------------------------|

| Gen1      | x1, x2, x4, x8, x16       | 256 Bits | 125                                  | -1, -2                      |

| Gen2      | x1, x2, x4, x8,           | 256 bits | 125                                  | -1, -2                      |

| Genz      | x16                       | 256 bits | 250                                  | -1, -2                      |

| Car2      | x1, x2, x4                | 256 bits | 125                                  | -1, -2                      |

| Gen3      | ×8                        | 256 bits | 250                                  | -1, -2                      |

The recommended speed grades are for production parts.

# **1.6. Performance and Resource Utilization**

The Avalon-MM Intel Stratix 10 variants include an Avalon-MM DMA bridge implemented in soft logic. It operates as a front end to the hardened protocol stack. The resource utilization table below shows results for the Gen1 x1 and Gen3 x8 Simple DMA dynamically generated design examples.

The results are for the current version of the Intel Quartus Prime Pro Edition software. With the exception of M20K memory blocks, the numbers are rounded up to the nearest 50.

# Table 5. Resource Utilization Avalon-MM Intel Stratix 10 Hard IP for PCI Express IP Core

| Variant | Typical ALMs | M20K Memory<br>Blocks <sup>(1)</sup> | Logic Registers |

|---------|--------------|--------------------------------------|-----------------|

| Gen1 x1 | 3,018        | 64                                   | 4,690           |

| Gen3 x8 | 15,976       | 69                                   | 32,393          |

#### **Related Information**

Running the Fitter

For information on Fitter constraints.

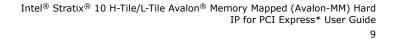

## **1.7. Transceiver Tiles**

Intel Stratix 10 introduces several transceiver tile variants to support a wide variety of protocols.

#### Figure 2. Intel Stratix 10 Transceiver Tile Block Diagram

<sup>&</sup>lt;sup>(1)</sup> These results include the logic necessary to implement the 2, On-Chip Memories and the PCIe DMA 256-bit Controller which are included in the designs.

| Tile   | Device Type | Channel C                         | Channel Hard IP Access            |                        |

|--------|-------------|-----------------------------------|-----------------------------------|------------------------|

| The    |             | Chip-to-Chip                      | Backplane                         | Channel Hard IP Access |

| L-Tile | GX          | 26 Gbps (NRZ) 12.5 Gbps (NRZ)     |                                   | PCIe Gen3x16           |

| H-Tile | GX          | 28.3 Gbps (NRZ)                   | 28.3 Gbps (NRZ)                   | PCIe Gen3x16           |

| E-Tile | GXE         | 30 Gbps (NRZ),<br>56 Gbps (PAM-4) | 30 Gbps (NRZ),<br>56 Gbps (PAM-4) | 100G Ethernet          |

#### Table 6.Transceiver Tiles Channel Types

#### **L-Tile and H-Tile**

Both L and H transceiver tiles contain four transceiver banks-with a total of 24 duplex channels, eight ATX PLLs, eight fPLLs, eight CMU PLLs, a PCIe Hard IP block, and associated input reference and transmitter clock networks. L and H transceiver tiles also include 10GBASE-KR/40GBASE-KR4 FEC block in each channel.

L-Tiles have transceiver channels that support up to 26 Gbps chip-to-chip or 12.5 Gbps backplane applications. H-Tiles have transceiver channels to support 28 Gbps applications. H-Tile channels support fast lock-time for Gigabit-capable passive optical network (GPON).

Intel Stratix 10 GX/SX devices incorporate L-Tiles or H-Tiles. Package migration is available with Intel Stratix 10 GX/SX from L-Tile to H-Tile variants.

#### **E-Tile**

E-Tiles are designed to support 56 Gbps with PAM-4 signaling or up to 30 Gbps backplane with NRZ signaling. E-Tiles do not include any PCIe Hard IP blocks.

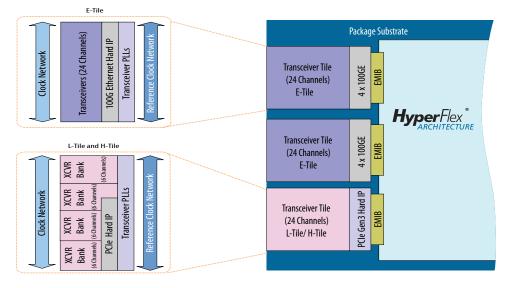

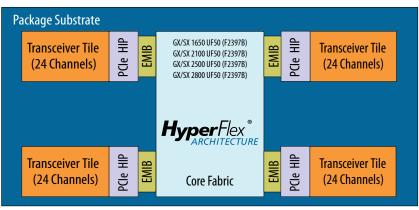

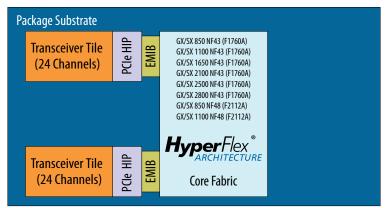

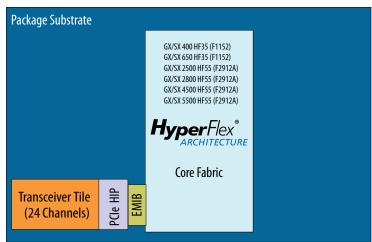

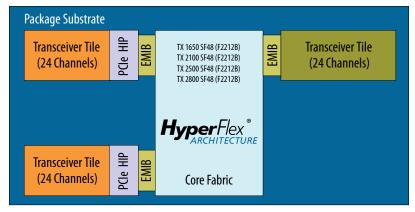

### **1.8. PCI Express IP Core Package Layout**

Intel Stratix 10 devices have high-speed transceivers implemented on separate transceiver tiles. The transceiver tiles are on the left and right sides of the device.

Each 24-channel transceiver L- or H- tile includes one x16 PCIe IP Core implemented in hardened logic. The following figures show the layout of PCIe IP cores in Intel Stratix 10 devices. Both L- and H-tiles are orange. E-tiles are green.

# Figure 3. Intel Stratix 10 GX/SX Devices with 4 PCIe Hard IP Cores and 96 Transceiver Channels

# Figure 4. Intel Stratix 10 GX/SX Devices with 2 PCIe Hard IP Cores and 48 Transceiver Channels

Figure 5. Intel Stratix 10 GX/SX Devices with 2 PCIe Hard IP Cores and 48 Transceiver Channels - Transceivers on Both Sides

| Package Substrate                     |                                        |                  |                                   |  |  |  |

|---------------------------------------|----------------------------------------|------------------|-----------------------------------|--|--|--|

|                                       | GX/SX 650 NF43 (F1760C)                |                  |                                   |  |  |  |

|                                       | HyperFlex <sup>®</sup><br>ARCHITECTURE |                  |                                   |  |  |  |

| Transceiver Tile<br>(24 Channels) = 2 | Core Fabric                            | EMIB<br>PCIe HIP | Transceiver Tile<br>(24 Channels) |  |  |  |

Figure 6. Intel Stratix 10 Migration Device with 2 Transceiver Tiles and 48 Transceiver Channels

| Package Substrate |                  |                        |      |          |                  |  |

|-------------------|------------------|------------------------|------|----------|------------------|--|

|                   |                  | GX 2800 NF45 (F1932)   |      |          |                  |  |

|                   |                  |                        |      |          |                  |  |

|                   |                  | HyperFlex <sup>®</sup> |      |          |                  |  |

|                   |                  | - ARCHITECTURE         |      |          |                  |  |

| Transceiver Tile  | PCIe HIP<br>EMIB |                        | EMIB | PCIe HIP | Transceiver Tile |  |

| (24 Channels)     | PCle<br>EN       | Core Fabric            | E    | PCle     | (24 Channels)    |  |

*Note:* 1. Intel Stratix 10 migration device contains 2 L-Tiles which match Intel Arria 10 migration device.

# Figure 7. Intel Stratix 10 GX/SX Devices with 1 PCIe Hard IP Core and 24 Transceiver Channels

# Figure 8. Intel Stratix 10 TX Devices with 1 PCIe Hard IP Core and 144 Transceiver Channels

| Package Substrate                 |          |      |                                                |      |                                   |  |

|-----------------------------------|----------|------|------------------------------------------------|------|-----------------------------------|--|

| Transceiver Tile<br>(24 Channels) |          | EMIB | TX 1650 YF55 (F2912B)<br>TX 2100 YF55 (F2912B) | EMIB | Transceiver Tile<br>(24 Channels) |  |

| Transceiver Tile<br>(24 Channels) |          | EMIB | HyperFlex <sup>®</sup>                         | EMIB | Transceiver Tile<br>(24 Channels) |  |

| Transceiver Tile<br>(24 Channels) | PCIe HIP | EMIB | Core Fabric                                    | EMIB | Transceiver Tile<br>(24 Channels) |  |

Note:

- 1. Intel Stratix 10 TX Devices use a combination of E-Tiles and H-Tiles.

- 2. Five E-Tiles support 57.8G PAM-4 and 28.9G NRZ backplanes.

- 3. One H-Tile supports up to 28.3G backplanes and PCIe up to Gen3 x16.

#### Intel Stratix 10 TX Devices with 1 PCIe Hard IP Core and 96 Transceiver Figure 9. Channels

| Package S                         | Substrate            |          | _                                                                                                |                                        |                                   |                                   |

|-----------------------------------|----------------------|----------|--------------------------------------------------------------------------------------------------|----------------------------------------|-----------------------------------|-----------------------------------|

| Transceiver Tile<br>(24 Channels) |                      | EMIB     | TX 1650 UF50 (F2397C)<br>TX 2100 UF50 (F2397C)<br>TX 2500 UF50 (F2397C)<br>TX 2800 UF50 (F2397C) |                                        | Transceiver Tile<br>(24 Channels) |                                   |

|                                   |                      |          |                                                                                                  | HyperFlex <sup>®</sup><br>Architecture |                                   |                                   |

|                                   | iver Tile<br>annels) | PCIe HIP | EMIB                                                                                             | Core Fabric                            | EMIB                              | Transceiver Tile<br>(24 Channels) |

Note: 1. Intel Stratix 10 TX Devices use a combination of E-Tiles and H-Tiles.

- 2. Three E-Tiles support 57.8G PAM-4 and 28.9G NRZ backplanes.

- 3. One H-Tile supports up to 28.3G backplanes PCIe up to Gen3 x16..

#### Figure 10. Intel Stratix 10 TX Devices with 2 PCIe Hard IP Cores and 72 Transceiver **Channels**

Note:

- 1. Intel Stratix 10 TX Devices use a combination of E-Tiles and H-Tiles.

- 2. One E-Tile support 57.8G PAM-4 and 28.9G NRZ backplanes.

- 3. Two H-Tiles supports up to 28.3G backplanes PCIe up to Gen3 x16..

#### **Related Information**

#### Stratix 10 GX/SX Device Overview

For more information about Stratix 10 devices.

# **1.9. Channel Availability**

#### **PCIe Hard IP Channel Restrictions**

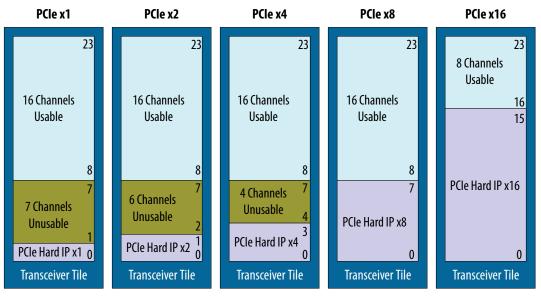

Each L- or H-Tile transceiver tile contains one PCIe Hard IP block. The following table and figure show the possible PCIe Hard IP channel configurations, the number of unusable channels, and the number of channels available for other protocols. For example, a PCIe x4 variant uses 4 channels and 4 additional channels are unusable.

#### Table 7.Unusable Channels

| PCIe Hard IP Configuration | Number of Unusable Channels | Usable Channels |

|----------------------------|-----------------------------|-----------------|

| PCIe x1                    | 7                           | 16              |

| PCIe x2                    | 6                           | 16              |

| PCIe x4                    | 4                           | 16              |

| PCIe x8                    | 0                           | 16              |

| PCIe x16                   | 0                           | 8               |

#### *Note:* The PCIe Hard IP uses at least the bottom eight Embedded Multi-Die Interconnect Bridge (EMIB) channels, no matter how many PCIe lanes are enabled. Thus, these EMIB channels become unavailable for other protocols.

#### Figure 11. PCIe Hard IP Channel Configurations Per Transceiver Tile

The table below maps all transceiver channels to PCIe Hard IP channels in available tiles.

Send Feedback

| Tile Channel<br>Sequence | PCIe Hard IP<br>Channel | Index within<br>I/O Bank | Bottom Left<br>Tile Bank<br>Number | Top Left Tile<br>Bank Number | Bottom Right<br>Tile Bank<br>Number | Top Right Tile<br>Bank Number |

|--------------------------|-------------------------|--------------------------|------------------------------------|------------------------------|-------------------------------------|-------------------------------|

| 23                       | N/A                     | 5                        | 1F                                 | 1N                           | 4F                                  | 4N                            |

| 22                       | N/A                     | 4                        | 1F                                 | 1N                           | 4F                                  | 4N                            |

| 21                       | N/A                     | 3                        | 1F                                 | 1N                           | 4F                                  | 4N                            |

| 20                       | N/A                     | 2                        | 1F                                 | 1N                           | 4F                                  | 4N                            |

| 19                       | N/A                     | 1                        | 1F                                 | 1N                           | 4F                                  | 4N                            |

| 18                       | N/A                     | 0                        | 1F                                 | 1N                           | 4F                                  | 4N                            |

| 17                       | N/A                     | 5                        | 1E                                 | 1M                           | 4E                                  | 4M                            |

| 16                       | N/A                     | 4                        | 1E                                 | 1M                           | 4E                                  | 4M                            |

| 15                       | 15                      | 3                        | 1E                                 | 1M                           | 4E                                  | 4M                            |

| 14                       | 14                      | 2                        | 1E                                 | 1M                           | 4E                                  | 4M                            |

| 13                       | 13                      | 1                        | 1E                                 | 1M                           | 4E                                  | 4M                            |

| 12                       | 12                      | 0                        | 1E                                 | 1M                           | 4E                                  | 4M                            |

| 11                       | 11                      | 5                        | 1D                                 | 1L                           | 4D                                  | 4L                            |

| 10                       | 10                      | 4                        | 1D                                 | 1L                           | 4D                                  | 4L                            |

| 9                        | 9                       | 3                        | 1D                                 | 1L                           | 4D                                  | 4L                            |

| 8                        | 8                       | 2                        | 1D                                 | 1L                           | 4D                                  | 4L                            |

| 7                        | 7                       | 1                        | 1D                                 | 1L                           | 4D                                  | 4L                            |

| 6                        | 6                       | 0                        | 1D                                 | 1L                           | 4D                                  | 4L                            |

| 5                        | 5                       | 5                        | 1C                                 | 1K                           | 4C                                  | 4К                            |

| 4                        | 4                       | 4                        | 1C                                 | 1K                           | 4C                                  | 4K                            |

| 3                        | 3                       | 3                        | 1C                                 | 1K                           | 4C                                  | 4K                            |

| 2                        | 2                       | 2                        | 1C                                 | 1K                           | 4C                                  | 4K                            |

| 1                        | 1                       | 1                        | 1C                                 | 1K                           | 4C                                  | 4К                            |

| 0                        | 0                       | 0                        | 1C                                 | 1K                           | 4C                                  | 4K                            |

#### Table 8. PCIe Hard IP channel mapping across all tiles

#### PCIe Soft IP Channel Usage

PCI Express soft IP PIPE-PHY cores available from third-party vendors are not subject to the channel usage restrictions described above. Refer to Intel FPGA > Products > Intellectual Property for more information about soft IP cores for PCI Express.

# 2. Quick Start Guide

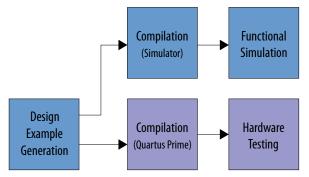

Using Intel Quartus Prime Pro Edition, you can generate a simple DMA design example for the Avalon-MM Intel Stratix 10 Hard IP for PCI Express IP core. The generated design example reflects the parameters that you specify. It automatically creates the files necessary to simulate and compile in the Intel Quartus Prime Pro Edition software. You can download the compiled design to the Intel Stratix 10-GX Development Board. To download to custom hardware, update the Intel Quartus Prime Settings File (.qsf) with the correct pin assignments .

#### Figure 12. Development Steps for the Design Example

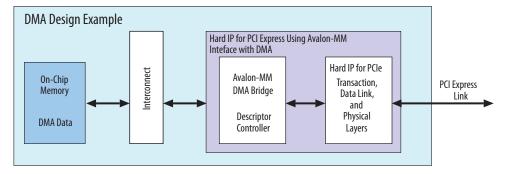

## 2.1. Design Components

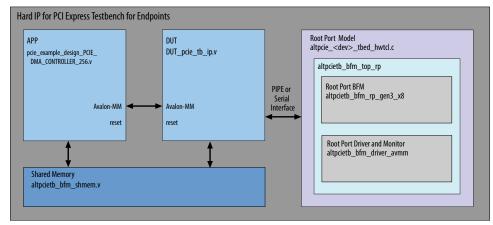

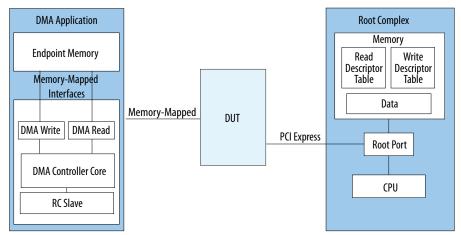

#### Figure 13. Block Diagram for the Avalon-MM DMA for PCIe Design Example

Intel Corporation. All rights reserved. Agilex, Altera, Arria, Cyclone, Enpirion, Intel, the Intel logo, MAX, Nios, Quartus and Stratix words and logos are trademarks of Intel Corporation or its subsidiaries in the U.S. and/or other countries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services. \*Other names and brands may be claimed as the property of others.

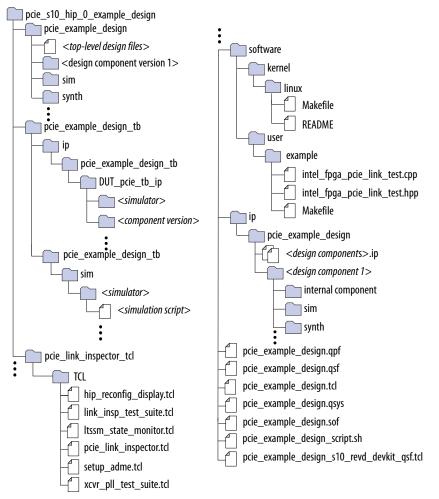

# 2.2. Directory Structure

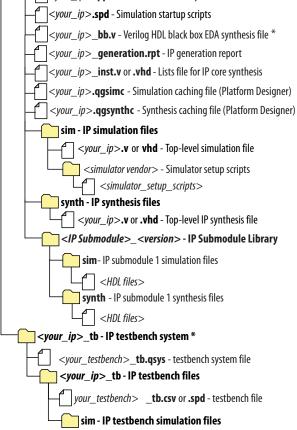

#### Figure 14. **Directory Structure for the Generated Design Example**

# **2.3. Generating the Design Example**

Follow these steps to generate your design:

#### Figure 15. Procedure

- In the Intel Quartus Prime Pro Edition software, create a new project (File ➤ New Project Wizard).

- 2. Specify the Directory, Name, and Top-Level Entity.

- 3. For Project Type, accept the default value, Empty project. Click Next.

- 4. For Add Files click Next.

- 5. For Family, Device & Board Settings under Family, select Intel Stratix 10 (GX/SX/MX/TX) and the Target Device for your design.

- 6. Click Finish.

- 7. In the IP Catalog locate and add the Avalon-MM Intel Stratix 10 Hard IP for PCI Express.

- 8. In the **New IP Variant** dialog box, specify a name for your IP. Click **Create**.

- 9. On the **IP Settings** tabs, specify the parameters for your IP variation.

- 10. On the **Example Designs** tab, make the following selections:

- a. For Available Example Designs, select DMA.

- *Note:* The **DMA** design example is only available when you turn on **Enable Avalon-MM DMA** on the **Avalon-MM Settings** tab.

- *Note:* If you do not turn on **Enable Avalon-MM DMA**, you can still choose either a **PIO** or a **Simple DMA** design example.

- b. For Example Design Files, turn on the Simulation and Synthesis options. If you do not need these simulation or synthesis files, leaving the corresponding option(s) turned off significantly reduces the example design generation time.

- c. For **Generated HDL Format**, only Verilog is available in the current release.

- d. For Target Development Kit, select the appropriate option.

- *Note:* If you select **None**, the generated design example targets the device you specified in Step 5 above. If you intend to test the design in hardware, make the appropriate pin assignments in the .qsf file. You can also use the pin planner tool to make pin assignments.

- 11. Select **Generate Example Design** to create a design example that you can simulate and download to hardware. If you select one of the Intel Stratix 10 development boards, the device on that board overwrites the device previously selected in the Intel Quartus Prime project if the devices are different. When the prompt asks you to specify the directory for your example design, you can accept the default directory, <example\_design>/

pcie\_s10\_hip\_avmm\_bridge\_0\_example\_design, or choose another directory.

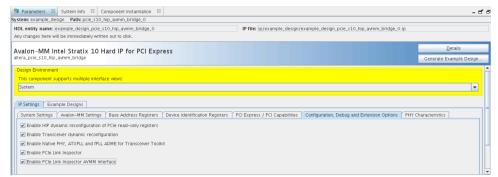

#### Figure 16. Example Design Tab

| valon-MM Intel Stratix 10 Hard IP for PCI Express                       | Details                  |  |

|-------------------------------------------------------------------------|--------------------------|--|

| tera_pcie_s10_hip_avmm_bridge                                           | Generate Example Design. |  |

| Design Environment                                                      |                          |  |

| This component supports multiple interface views:                       |                          |  |

| Standalone                                                              |                          |  |

|                                                                         |                          |  |

| IP Settings Example Designs                                             |                          |  |

| * Available Example Designs                                             |                          |  |

| Select design: DMA -                                                    |                          |  |

| * Example Design Files                                                  |                          |  |

| Simulation                                                              |                          |  |

| ✓ Synthesis                                                             |                          |  |

| * Generated HDL Format                                                  |                          |  |

| Generated file format: Verilog                                          |                          |  |

| * Target Development Kit                                                |                          |  |

| Current development kit:: Stratix 10 GX L-Tile ES2 FPGA Development Kit |                          |  |

When you generate an Intel Stratix 10 example design, a file called recommended\_pinassignments\_s10.txt is created in the directory pcie\_s10\_hip\_avmm\_bridge\_0\_example\_design.<sup>(2)</sup>

- 12. Click **Finish**. You may save your .ip file when prompted, but it is not required to be able to use the example design.

- 13. The prompt, **Recent changes have not been generated. Generate now?**, allows you to create files for simulation and synthesis of the IP core variation that you specified in Step 9 above. Click **No** if you only want to work with the design example you have generated.

- 14. Close the dummy project.

- 15. Open the example design project.

- 16. Compile the example design project to generate the .sof file for the complete example design. This file is what you download to a board to perform hardware verification.

- 17. Close your example design project.

#### **Related Information**

AN-811: Using the Avery BFM for PCI Express Gen3x16 Simulation on Intel Stratix 10 Devices

<sup>(2)</sup> This file contains the recommended pin assignments for all the pins in the example design. If you select a development kit option in the pull-down menu for Target Development Kit, the pin assignments in the recommended\_pinassignments\_s10.txt file match those that are in the .qsf file in the same directory. If you chose NONE in the pull-down menu, the .qsf file does not contain any pin assignments\_s10.txt file to the .qsf file. You can always change any pin assignment in the .qsf file to satisfy your design or board requirements.

# 2.4. Simulating the Design Example

#### Figure 17. Procedure

- 1. Change to the testbench simulation directory, pcie\_example\_design\_tb.

- 2. Run the simulation script for the simulator of your choice. Refer to the table below.

- 3. Analyze the results.

#### Table 9. Steps to Run Simulation

| Simulator                      | Working Directory                                                                                              | Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                |

|--------------------------------|----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ModelSim*                      | <pre><example_design>/ pcie_example_design_tb/ pcie_example_design_tb/sim/mentor/</example_design></pre>       | <ol> <li>Invoke vsim (by typing vsim, which brings up<br/>a console window where you can run the<br/>following commands).</li> <li>do msim_setup.tcl<br/>Note: Alternatively, instead of doing Steps 1<br/>and 2, you can type: vsim -c -do<br/>msim_setup.tcl.</li> <li>ld_debug</li> <li>run -all</li> <li>A successful simulation ends with the following<br/>message, "Simulation stopped due to<br/>successful completion!"</li> </ol> |

| VCS*                           | <pre><example_design>/ pcie_example_design_tb/ pcie_example_design_tb/sim/ synopsys/vcs</example_design></pre> | <ol> <li>sh vcs_setup.sh<br/>USER_DEFINED_COMPILE_OPTIONS=""<br/>USER_DEFINED_ELAB_OPTIONS="-xlrm\<br/>uniq_prior_final"<br/>USER_DEFINED_SIM_OPTIONS=""</li> <li>A successful simulation ends with the following<br/>message, "Simulation stopped due to<br/>successful completion!"</li> </ol>                                                                                                                                            |

| NCSim*                         | <pre><example_design>/ pcie_example_design_tb/ pcie_example_design_tb/sim/cadence</example_design></pre>       | <ol> <li>sh ncsim_setup.sh<br/>USER_DEFINED_SIM_OPTIONS=""<br/>USER_DEFINED_ELAB_OPTIONS="-<br/>timescale\ lns/lps"</li> <li>A successful simulation ends with the following<br/>message, "Simulation stopped due to<br/>successful completion!"</li> </ol>                                                                                                                                                                                 |

| Xcelium* Parallel<br>Simulator | <pre><example_design>/ pcie_example_design_tb/ pcie_example_design_tb/sim/xcelium</example_design></pre>       | <ol> <li>sh xcelium_setup.sh<br/>USER_DEFINED_SIM_OPTIONS=""<br/>USER_DEFINED_ELAB_OPTIONS ="-<br/>timescale\ lns/lps\ -NOWARN\<br/>CSINFI"</li> <li>A successful simulation ends with the following<br/>message, "Simulation stopped due to<br/>successful completion!"</li> </ol>                                                                                                                                                         |

The DMA testbench completes the following tasks:

- 1. Writes to the Endpoint memory using the DUT Endpoint non-bursting Avalon-MM master interface.

- 2. Reads from Endpoint memory using the DUT Endpoint non-bursting Avalon-MM master interface.

- 3. Verifies the data using the shmem\_chk\_ok task.

- 4. Writes to the Endpoint DMA controller, instructing the DMA controller to perform a MRd request to the PCIe address space in host memory.

- 5. Writes to the Endpoint DMA controller, instructing the DMA controller to perform a MWr request to PCIe address space in host memory. This MWr uses the data from the previous MRd.

- 6. Verifies the data using the shmem\_chk\_ok task.

The simulation reports, "Simulation stopped due to successful completion" if no errors occur.

#### Figure 18. Partial Transcript from Successful Simulation Testbench

| # | INFO:         | 88656 1     | ns Maximum Link Width: x8                             |

|---|---------------|-------------|-------------------------------------------------------|

| # | INFO:         | 88656 1     | s Supported Link Speed: 8.0GT/s or 5.0GT/s or 2.5GT/s |

| # | INFO:         | 88656 1     | LOS Entry: Supported                                  |

| # | INFO:         | 88656 1     | L1 Entry: Not Supported                               |

| # | INFO:         | 88656 1     | s LOs Exit Latency: 2 us to 4 us                      |

| # | INFO:         | 88656 1     | s L1 Exit Latency: Less Than 1 us                     |

| # | INFO:         | 99928 1     | s BAR Address Assignments:                            |

| # | INFO:         | 99928 1     | s BAR Size Assigned Address Type                      |

| # | INFO:         | 99928 1     |                                                       |

| # | INFO:         | 99928 1     | s BAR1:0 4 KBytes 00000000 80000000 Prefetchable      |

| # | INFO:         | 99928 1     | s BAR3:2 64 KBytes 00000000 80010000 Prefetchable     |

| # | INFO:         | 99928 1     | is BAR4 Disabled                                      |

| # | INFO:         | 99928 1     | s BAR5 Disabled                                       |

| # | INFO:         | 99928 1     | s ExpROM Disabled                                     |

| # | INFO:         | 100704 1    | as Completed configuration of Endpoint BARs.          |

| # | INFO:         | 101608 r    | s Starting Target Write/Read Test.                    |

| # | INFO:         | 101608 1    | as Target BAR = 0                                     |

| ŧ | INFO:         | 101608 1    | s Length = 000512, Start Offset = 000000              |

| # | INFO:         | 103096 1    | Is Target Write and Read compared okay!               |

| ŧ | INFO:         | 103096 1    | ns Starting DMA Read/Write Test.                      |

| # | INFO:         | 103096 1    | s Setup BAR = 2                                       |

| ŧ | INFO:         | 103096 1    | s Length = 000512, Start Offset = 000000              |

| # | INFO:         | 106882 1    | is Clear Interrupt INTA                               |

| ŧ | INFO:         | 111416 1    | s MSI recieved!                                       |

| # | INFO:         | 111416 1    | DMA Read and Write compared okay!                     |

| ŧ | SUCCESS: Simu | alation sto | opped due to successful completion!                   |

| # | Simulation pa | assed       |                                                       |

# 2.5. Compiling the Design Example and Programming the Device

- 1. Navigate to <project\_dir>/

pcie\_s10\_hip\_avmm\_bridge\_0\_example\_design/ and open

pcie\_example\_design.qpf.

- 2. On the Processing menu, select Start Compilation.

- 3. After successfully compiling your design, program the targeted device with the Programmer.

# 2.6. Installing the Linux Kernel Driver

Before you can test the design example in hardware, you must install the Linux kernel driver. You can use this driver to perform the following tests:

- A PCIe link test that performs 100 writes and reads

- Memory space DWORD<sup>(3)</sup> reads and writes •

- Configuration Space DWORD reads and writes ٠

In addition, you can use the driver to change the value of the following parameters:

- The BAR being used •

- The selects device by specifying the bus, device and function (BDF) numbers for the required device

Complete the following steps to install the kernel driver:

- 1. Navigate to ./software/kernel/linux under the example design generation directory.

- 2. Change the permissions on the install, load, and unload files:

\$ chmod 777 install load unload

3. Install the driver:

\$ sudo ./install

4. Verify the driver installation:

\$ lsmod | grep intel\_fpga\_pcie\_drv

Expected result:

intel fpga pcie drv 17792 0

5. Verify that Linux recognizes the PCIe design example:

\$ lspci -d 1172:000 -v | grep intel\_fpga\_pcie\_drv Note: If you have changed the Vendor ID, substitute the new Vendor ID for Intel's Vendor ID in this command.

Expected result:

Kernel driver in use: intel\_fpga\_pcie\_drv

### 2.7. Running the Design Example Application

- 1. Navigate to ./software/user/example under the design example directory.

- 2. Compile the design example application:

- \$ make

- 3. Run the test:

- \$ sudo ./intel\_fpga\_pcie\_link\_test

<sup>&</sup>lt;sup>(3)</sup> Throughout this user guide, the terms word, DWORD and QWORD have the same meaning that they have in the PCI Express Base Specification. A word is 16 bits, a DWORD is 32 bits, and a QWORD is 64 bits.

You can run the Intel FPGA IP PCIe link test in manual or automatic mode.

- In automatic mode, the application automatically selects the device. The test selects the Intel Stratix 10 PCIe device with the lowest BDF by matching the Vendor ID. The test also selects the lowest available BAR.

- In manual mode, the test queries you for the bus, device, and function number and BAR.

For the Intel Stratix 10 GX Development Kit, you can determine the BDF by typing the following command:

\$ lspci -d 1172

4. Here are sample transcripts for automatic and manual modes:

```

Intel FPGA PCIe Link Test - Automatic Mode

Version 2.0

0: Automatically select a device

1: Manually select a device

* * * *

*****

>0

Opened a handle to BAR 0 of a device with BDF 0x100

0: Link test - 100 writes and reads

1: Write memory space

2: Read memory space

3: Write configuration space

4: Read configuration space

5: Change BAR

6: Change device

7: Enable SR-IOV

8: Do a link test for every enabled virtual function

belonging to the current device

9: Perform DMA

10: Quit program

*****

> 0

Doing 100 writes and 100 reads . .

Number of write errors:

Number of read errors:

0

0

Number of DWORD mismatches: 0

Intel FPGA PCIe Link Test - Manual Mode

Version 1.0

0: Automatically select a device

1: Manually select a device

*****

*****

> 1

Enter bus number:

> 1

Enter device number:

> 0

Enter function number:

> 0

BDF is 0x100

Enter BAR number (-1 for none):

> 4

Opened a handle to BAR 4 of a device with BDF 0x100

```

#### **Related Information**

#### PCIe Link Inspector Overview

Use the PCIe Link Inspector to monitor the link at the Physical, Data Link and Transaction Layers.

# **3. Interface Overview**

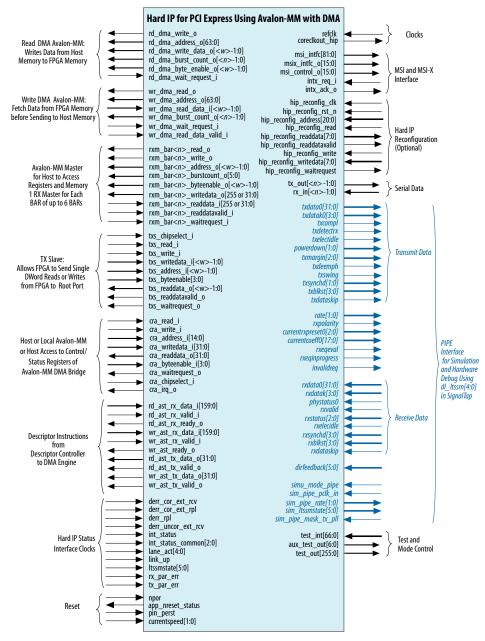

The Avalon-MM Intel Stratix 10 Hard IP for PCIe IP core includes many interface types to implement different functions.

These include:

- Avalon-MM interfaces to translate the PCIe TLPs into standard memory-mapped reads and writes

- DMA interfaces to transfer large blocks of data

- *Note:* DMA operations are only available when the application interface width is 256-bit, but not when it is 64-bit. You choose the interface width by selecting **IP Settings**, then **System Settings**, and finally **Application interface width**.

- Standard PCIe serial interfaces to transfer data over the PCIe link or links

- System interfaces for interrupts, clocking, reset, and test

- Optional reconfiguration interface to dynamically change the value of configuration space registers at run-time

- Optional status interface for debug

Unless otherwise noted, all interfaces are synchronous to the rising edge of the main system clock coreclkout\_hip. You enable the interfaces using the component GUI.

#### **Related Information**

Interfaces on page 55

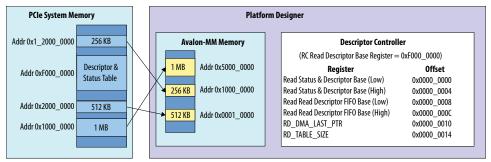

# **3.1. Avalon-MM DMA Interfaces when Descriptor Controller Is Internally Instantiated**

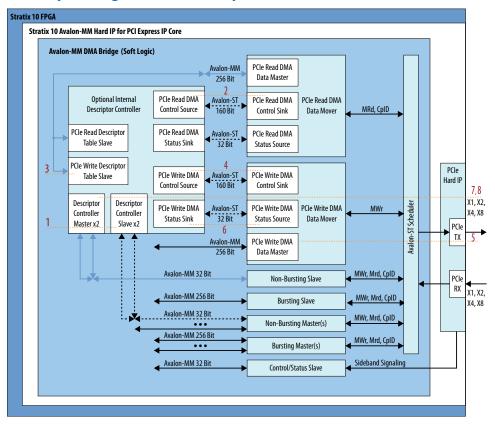

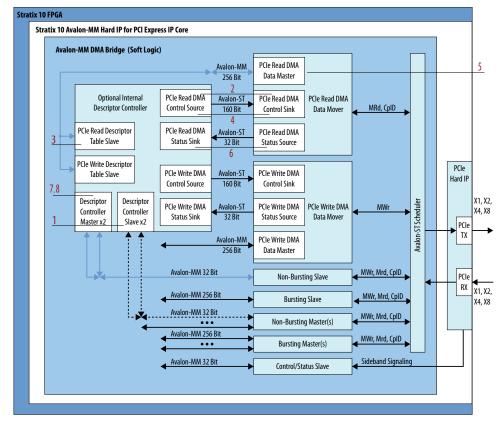

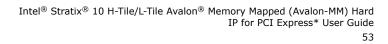

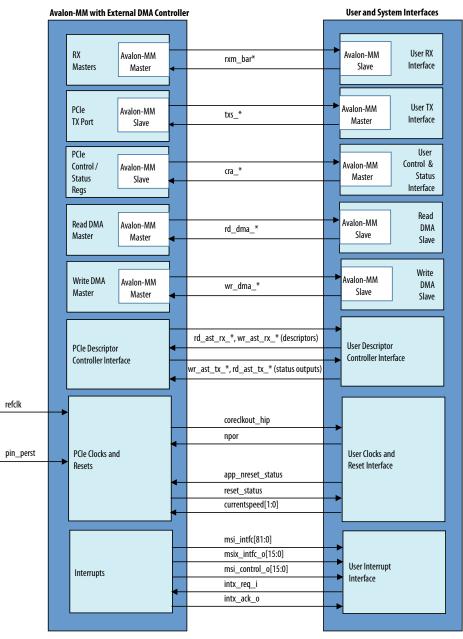

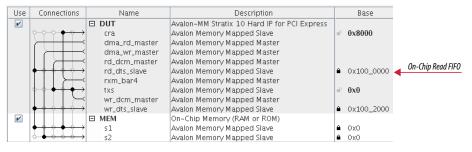

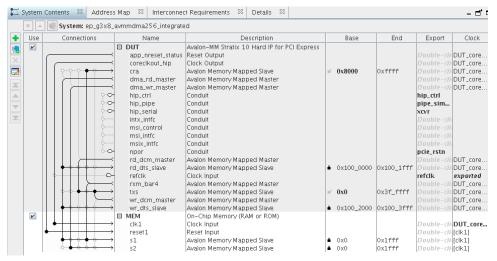

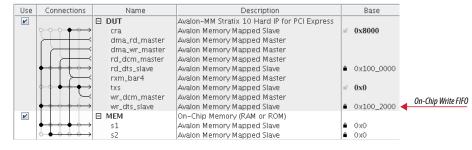

This configuration results from selecting both **Enable Avalon-MM DMA** and **Instantiate internal descriptor controller** in the component GUI.

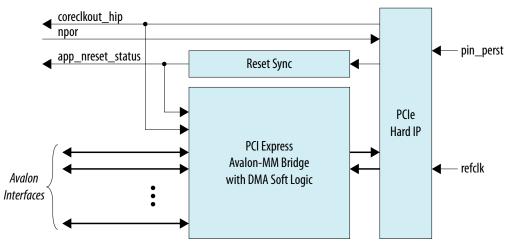

The following figure shows the Avalon-MM DMA Bridge, implemented in soft logic. It interfaces to the Hard IP for PCIe through Avalon-ST interfaces.

In the following figure, Avalon-ST connections and the connection from the BAR0 nonbursting master to the Descriptor Controller slaves are internal. Dashed black lines show these connections. Connections between the Descriptor Controller Masters and the non-bursting slave and the connections between the Read DMA Data Master and the Descriptor Table Slaves are made in the Platform Designer. Blue lines show these connections.

Intel Corporation. All rights reserved. Agilex, Altera, Arria, Cyclone, Enpirion, Intel, the Intel logo, MAX, Nios, Quartus and Stratix words and logos are trademarks of Intel Corporation or its subsidiaries in the U.S. and/or other countries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services. \*Other names and brands may be claimed as the property of others.

*Note:* In the following diagrams and text descriptions, the terms Read and Write are from the system memory perspective. Thus, a Read transaction reads data from the system memory and writes it to the local memory in Avalon-MM address space. A Write transaction writes the data that was read from the local memory in Avalon-MM address space to the system memory.

#### Figure 19. Avalon-MM DMA Bridge Block Diagram with Optional Internal Descriptor Controller (Showing DMA Write Flow)

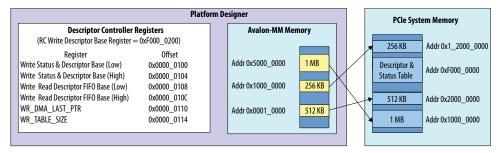

The numbers in this figure describe the following steps in the DMA write flow:

- 1. The CPU writes registers in the Descriptor Controller Slave to start the DMA.

- 2. The Descriptor Controller instructs the Read Data Mover to fetch the descriptor table.

- 3. The Read Data Mover forwards the descriptor table to the PCIe Write Descriptor Table Slave.

- 4. The Descriptor Controller instructs the Write Data Mover to transfer data.

- 5. The Write Data Mover transfers data from FPGA to system memory.

- 6. The Write Data Mover notifies the Descriptor Controller of the completion of the data transfer using the done bit.

- 7. The Descriptor Controller Master updates the status of the descriptor table in system memory.

- 8. The Descriptor Controller Master sends an MSI interrupt to the host.

#### Figure 20. Avalon-MM DMA Bridge Block Diagram with Optional Internal Descriptor Controller (Showing DMA Read Flow)

The numbers in this figure describe the following steps in the DMA read flow:

- 1. The CPU writes registers in the Descriptor Controller Slave to start the DMA.

- The Descriptor Controller instructs the Read Data Mover to fetch the descriptor table.

- The Read Data Mover forwards the descriptor table to the PCIe Read Descriptor Table Slave.

- 4. The Descriptor Controller instructs the Read Data Mover to transfer data.

- 5. The Read Data Mover transfers data from system memory to FPGA.

- 6. The Read Data Mover notifies the Descriptor Controller of the completion of the data transfer using the done bit.

- 7. The Descriptor Controller Master updates the status of the descriptor table in system memory.

- 8. The Descriptor Controller Master sends an MSI interrupt to the host.

When the optional Descriptor Controller is included in the bridge, the Avalon-MM bridge includes the following Avalon interfaces to implement the DMA functionality:

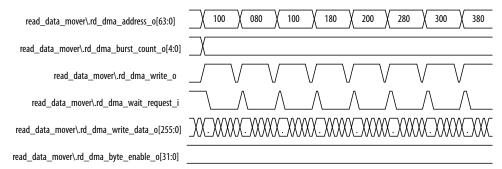

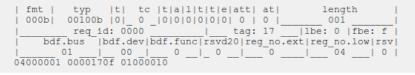

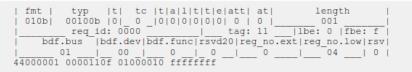

- PCIe Read DMA Data Master (rd\_dma): This is a 256-bit wide write only Avalon-MM master interface which supports bursts of up to 16 cycles with the rd\_dma\* prefix. The Read Data Mover uses this interface to write at high throughput the blocks of data that it has read from the PCIe system memory space. This interface writes descriptors to the Read and Write Descriptor table slaves and to any other Avalon-MM connected slaves interfaces.

- PCIe Write DMA Data Master (wr\_dma): This read-only interface transfers blocks of data from the Avalon-MM domain to the PCIe system memory space at high throughput. It drives read transactions on its bursting Avalon-MM master interface. It also creates PCIe Memory Write (MWr) TLPs with data payload from Avalon-MM reads. It forwards the MWr TLPs to the Hard IP for transmission on the link. The Write Data Mover module decomposes the transfers into the required number of Avalon-MM burst read transactions and PCIe MWr TLPs. This is a bursting, 256-bit Avalon-MM interface with the wr\_dma prefix.

- PCIe Read Descriptor Table Slave (rd\_dts): This is a 256-bit Avalon-MM slave interface that supports write bursts of up to 16 cycles. The PCIe Read DMA Data Master writes descriptors to this table. This connection is made outside the DMA bridge because the Read Data Mover also typically connects to other Avalon-MM slaves. The prefix for this interface is rd\_dts.

- PCIe Write Descriptor Table Slave (wr\_dts): This is a 256-bit Avalon-MM slave interface that supports write bursts of up to 16 cycles. The PCIe Read DMA Data Master writes descriptors to this table. The PCIe Read DMA Data Master must connect to this interface outside the DMA bridge because the bursting master interface may also need to be connected to the destination of the PCIe Read Data Mover. The prefix for this interface is wr\_dts.

- Descriptor Controller Master (DCM): This is a 32-bit, non-bursting Avalon-MM master interface with write-only capability. It controls the non-bursting Avalon-MM slave that transmits single DWORD DMA status information to the host. The prefixes for this interface are wr\_dcm and rd\_dcm.

- Descriptor Controller Slave (DCS): This is a 32-bit, non-bursting Avalon-MM slave interface with read and write access. The host accesses this interface through the BAR0 Non-Bursting Avalon-MM Master, to program the Descriptor Controller.

- *Note:* This is not a top-level interface of the Avalon-MM Bridge. Because it connects to BAR0, you cannot use BAR0 to access any other Avalon-MM slave interface.

#### **Related Information**

Programming Model for the DMA Descriptor Controller on page 105

Send Feedback

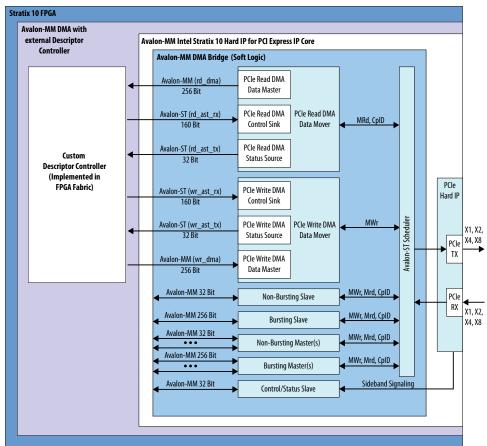

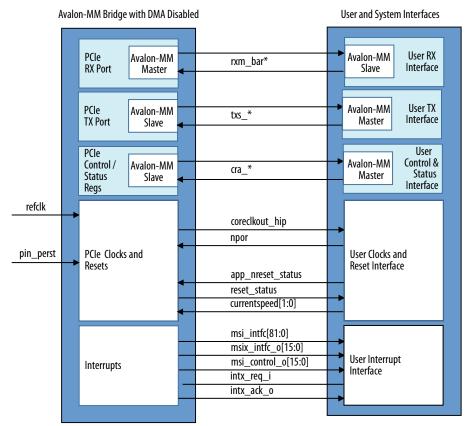

# **3.2. Avalon-MM DMA Interfaces when Descriptor Controller is Externally Instantiated**

This configuration results from selecting **Enable Avalon-MM DMA** and disabling **Instantiate internal descriptor controller** in the component GUI. This configuration requires you to include a custom DMA descriptor controller in your application.

Using the external DMA descriptor controller provides more flexibility. You can either modify the example design's DMA Descriptor Controller or replace it to meet your system requirements. You may need to modify the DMA Descriptor Controller for the following reasons:

- To implement multi-channel operation

- To implement the descriptors as a linked list or to implement a custom DMA programming model

- To fetch descriptors from local memory, instead of system (host-side) memory

To interface to the DMA logic included in this variant, the custom DMA descriptor controller must implement the following functions:

- It must provide the descriptors to the PCIe Read DMA Data Mover and PCIe Write DMA Data Mover.

- It must process the status that the DMA Avalon-MM write (wr\_dcm) and read (rd\_dcm) masters provide.

The following figure shows the Avalon-MM DMA Bridge when the a custom descriptor controller drives the PCIe Read DMA and Write DMA Data Movers.

#### Figure 21. Avalon-MM DMA Bridge Block Diagram with Externally Instantiated **Descriptor Controller**

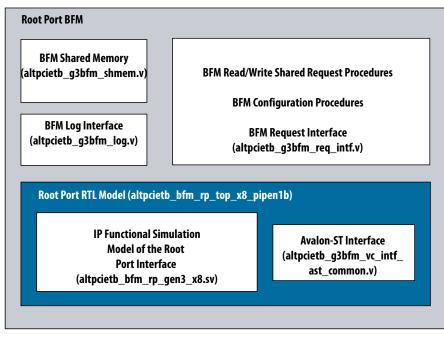

This configuration includes the PCIe Read DMA and Write DMA Data Movers. The custom DMA descriptor controller must connect to the following Data Mover interfaces:

- PCIe Read DMA Control Sink: This is a 160-bit, Avalon-ST sink interface. The custom DMA descriptor controller drives descriptor table entries on this bus. The prefix for the interface is rd ast rx\*.

- PCIe Write DMA Control Sink: This is a 160-bit, Avalon-ST sink interface. The custom DMA descriptor controller drives write table entries on this bus. The prefix for this interface is wr\_ast\_rx\*.

- PCIe Read DMA Status Source: The Read Data Mover reports status to the custom ٠ DMA descriptor controller on this interface. The prefix for this interface is rd\_ast\_tx\_\*.

- PCIe Write DMA Status Source: The Write Data Mover reports status to the custom DMA descriptor controller on this interface. The prefix for this interface is wr\_ast\_tx\_\*.

# 3.3. Other Avalon-MM Interfaces

This configuration results from deselecting Enable Avalon-MM DMA in the component GUI.

This variant hides the complexity of the PCIe Protocol by translating between the TLPs exchanged on the PCIe link into memory-mapped reads and writes in the Avalon-MM domain. The following figure shows the Avalon-MM DMA Bridge interfaces available when the bridge does not enable the PCIe Read DMA and Write DMA Data Movers.

#### Figure 22. Avalon-MM DMA Bridge Block Diagram without DMA Functionality

#### 3.3.1. Avalon-MM Master Interfaces

Avalon-MM Master modules translate PCI Express MRd and MWr TLP requests received from the PCI Express link to Avalon-MM read and write transactions on their Avalon-MM interface. The Avalon-MM master modules return the read data received on their Avalon-MM interface using PCI Express Completion TLPs (CpID).

Up to six Avalon-MM Master interfaces can be enabled at configuration time, one for each of the six supported BARs. Each of the enabled Avalon-MM Master interfaces can be set to be bursting or non-bursting in the component GUI. Bursting Avalon-MM Masters are designed for high throughput transfers, and the application interface data bus width can be either 256-bit or 64-bit. Non-bursting Avalon-MM Masters are designed for small transfers requiring finer granularity for byte enable control, or for control of 32-bit Avalon-MM Slaves. The prefix for signals comprising this interface is rxm\_bar<br/>bar\_num>\*.

| Avalon-MM Master<br>Type | Data Bus Width | Max Burst Size | Byte Enable<br>Granularity | Maximum<br>Outstanding Read<br>Requests |

|--------------------------|----------------|----------------|----------------------------|-----------------------------------------|

| Non-bursting             | 32-bit         | 1 cycle        | Byte                       | 1                                       |

| Bursting                 | 256-bit        | 16 cycles      | DWord <sup>(4)</sup>       | 32                                      |

| Bursting                 | 64-bit         | 64 cycles      | Byte                       | 16                                      |

#### Table 10. Avalon-MM Master Module Features

## 3.3.2. Avalon-MM Slave Interfaces

Avalon-MM Slave Interfaces: The Avalon-MM Slave modules translate read and write transactions on their Avalon-MM interface to PCI Express MRd and MWr TLP requests. These modules return the data received in PCI Express Completion TLPs on the read data bus of their Avalon-MM interface.

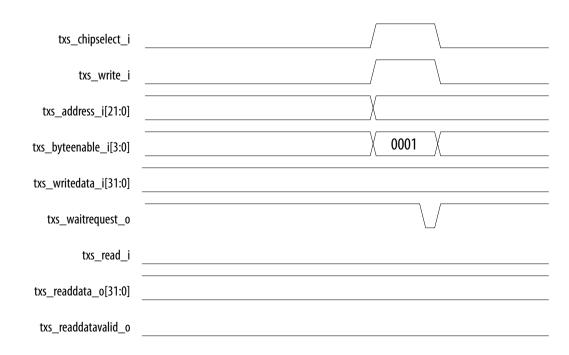

Two versions of Avalon-MM Slave modules are available: the bursting Avalon-MM Slave is for high throughput transfers, and the application interface data bus width can be either 256-bit or 64-bit. The non-bursting Avalon-MM Slave is for small transfers requiring finer granularity for byte enable control. The prefix for the non-bursting Avalon-MM Slave interface is  $txs^*$ . The prefix for the bursting Avalon-MM Slave interface is  $hptxs_*$

#### Table 11. Avalon-MM Slave Module Features

| Avalon-MM Slave<br>Type | Data Bus Width | Max Burst Size | Byte Enable<br>Granularity | Maximum<br>Outstanding Read<br>Requests |

|-------------------------|----------------|----------------|----------------------------|-----------------------------------------|

| Non-bursting            | 32-bit         | 1 cycle        | Byte                       | 1                                       |

| Bursting                | 256-bit        | 16 cycles      | DWord                      | 32                                      |

| Bursting                | 64-bit         | 64 cycles      | Byte                       | 16                                      |

The bursting Avalon-MM Slave adheres to the maximum payload size and maximum read request size values set by the system software after enumeration. It generates multiple PCIe TLPs for a single Avalon-MM burst transaction when required.

# Table 12.Number of TLPs generated for Each Burst Size as Function of Maximum<br/>Payload Size and Maximum Read Request Size

| Bursteeunt | Maximum Pay | load Size or Maximum Read Request Size |           |  |

|------------|-------------|----------------------------------------|-----------|--|

| Burstcount | 128 bytes   | 256 bytes                              | 512 bytes |  |

| 1 - 4      | 1 TLP       | 1 TLP                                  | 1 TLP     |  |

| 5 - 8      | 2 TLPs      | 1 TLP                                  | 1 TLP     |  |

| 9 - 12     | 3 TLPs      | 2 TLPs                                 | 1 TLP     |  |

| 13 - 16    | 4 TLPs      | 2 TLPs                                 | 1 TLP     |  |

*Note:* The burst sizes in the table above are for the 256-bit application interface width.

## 3.3.3. Control Register Access (CRA) Avalon-MM Slave

This optional, 32-bit Avalon-MM Slave provides access to the Control and Status registers. You must enable this interface when you enable address mapping for any of the Avalon-MM slaves or if interrupts are implemented.

The address bus width of this interface is fixed at 15 bits. The prefix for this interface is  $cra^*$ .

<sup>&</sup>lt;sup>(4)</sup> Using less than DWORD granularity has unpredictable results. Buffers must be sized to accommodate DWORD granularity.

## 3.4. Clocks and Reset

The Stratix 10 Hard IP for PCI Express generates the Application clock, coreclkout\_hip and reset signal. The Avalon-MM bridge provides a synchronized version of the reset signal, app\_nreset\_status, to the Application. This is an active low reset.

#### Figure 23. Avalon-MM Intel Stratix 10 Hard IP for PCI Express Clock and Reset Connections

*Note:* The input reference clock, refclk, must be stable and free-running at device powerup for a successful device configuration.

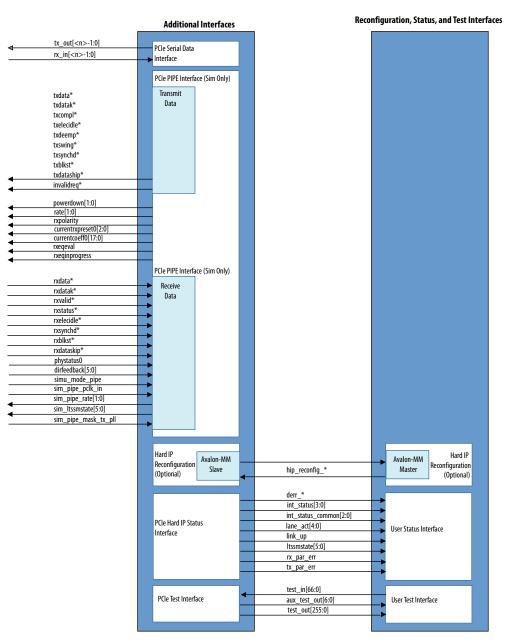

# 3.5. System Interfaces

#### **TX and RX Serial Data**