# Intel<sup>®</sup> Stratix<sup>®</sup> 10 High-Speed LVDS I/O User Guide

Updated for Intel<sup>®</sup> Quartus<sup>®</sup> Prime Design Suite: **19.4**

## Contents

| 1. Int | tel <sup>®</sup> Stratix <sup>®</sup> 10 High-Speed LVDS I/O Overview                  | 4   |

|--------|----------------------------------------------------------------------------------------|-----|

|        | 1.1. Intel Stratix 10 LVDS SERDES Usage Modes                                          | 4   |

|        | 1.2. Intel Stratix 10 LVDS Channels Support                                            |     |

|        | 1.3. Intel Stratix 10 GPIO Banks, SERDES, and DPA Locations                            | . 5 |

| 2. Int | tel Stratix 10 High-Speed LVDS I/O Architecture and Features                           | 7   |

|        | 2.1. Intel Stratix 10 LVDS SERDES I/O Standards Support                                |     |

|        | 2.2. LVDS Transmitter Programmable I/O Features                                        |     |

|        | 2.2.1. Programmable Pre-Emphasis                                                       |     |

|        | 2.2.2. Programmable Differential Output Voltage                                        | 9   |

|        | 2.3. SERDES Circuitry                                                                  |     |

|        | 2.4. Differential Transmitter in Intel Stratix 10 Devices                              | 11  |

|        | 2.4.1. Transmitter Blocks in Intel Stratix 10 Devices                                  |     |

|        | 2.4.2. Serializer Bypass for DDR and SDR Operations                                    | .11 |

|        | 2.5. Differential Receiver in Intel Stratix 10 Devices                                 | 12  |

|        | 2.5.1. Receiver Blocks in Intel Stratix 10 Devices                                     | 13  |

|        | 2.5.2. Receiver Modes in Intel Stratix 10 Devices                                      | 17  |

| 3. Str | atix 10 High-Speed LVDS I/O Design Considerations                                      | 20  |

|        | 3.1. PLLs and Clocking for Intel Stratix 10 Devices                                    |     |

|        | 3.1.1. Clocking Differential Transmitters                                              |     |

|        | 3.1.2. Clocking Differential Receivers                                                 |     |

|        | 3.1.3. Guideline: LVDS Reference Clock Source                                          |     |

|        | 3.1.4. Guideline: Use PLLs in Integer PLL Mode for LVDS                                |     |

|        | 3.1.5. Guideline: Use High-Speed Clock from PLL to Clock LVDS SERDES Only              | 22  |

|        | 3.1.6. Guideline: Pin Placement for Differential Channels                              | 22  |

|        | 3.1.7. LVDS Interface with External PLL Mode                                           | 25  |

|        | 3.2. Source-Synchronous Timing Budget                                                  |     |

|        | 3.2.1. Differential Data Orientation                                                   |     |

|        | 3.2.2. Differential I/O Bit Position                                                   |     |

|        | 3.2.3. Transmitter Channel-to-Channel Skew                                             |     |

|        | 3.2.4. Receiver Skew Margin for Non-DPA Mode                                           |     |

|        | 3.3. Guideline: LVDS SERDES IP Core Instantiation                                      |     |

|        | 3.4. Guideline: LVDS SERDES Pin Pairs for Soft-CDR Mode                                |     |

|        | 3.5. Guideline: LVDS Transmitters and Receivers in the Same I/O Bank                   |     |

|        | 3.5.1. Using the Duplex Feature                                                        |     |

|        | 3.6. Guideline: LVDS SERDES Limitation for Intel Stratix 10 GX 400, SX 400, and TX 400 |     |

|        |                                                                                        |     |

| 4. Int | tel Stratix 10 High-Speed LVDS I/O Implementation Guides                               |     |

|        | 4.1. LVDS SERDES Intel FPGA IP                                                         |     |

|        | 4.1.1. LVDS SERDES IP Core Features.                                                   |     |

|        | 4.1.2. LVDS SERDES IP Core Functional Modes                                            |     |

|        | 4.1.3. LVDS SERDES IP Core Functional Description                                      |     |

|        | 4.2.1. Initializing the LVDS SERDES IP Core in Non-DPA Mode                            |     |

|        | 4.2.1. Initializing the LVDS SERDES IP Core in DPA Mode                                |     |

|        | 4.2.3. Resetting the DPA                                                               |     |

|        |                                                                                        |     |

| 4.2.4. Word Boundaries Alignment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 45                                                 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| 4.3. LVDS SERDES IP Core Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                    |

| 4.3.1. I/O Timing Analysis.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 47                                                 |

| 4.3.2. FPGA Timing Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 48                                                 |

| 4.3.3. Timing Analysis for the External PLL Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                    |

| 4.3.4. Timing Closure Guidelines for Internal FPGA Paths                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 49                                                 |

| 4.3.5. Guideline: Use Clock Phase Alignment Block to Improve Timing Closure                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 49                                                 |

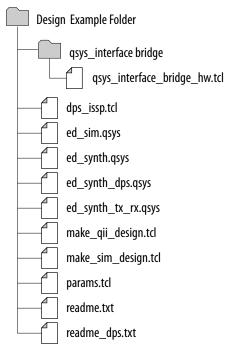

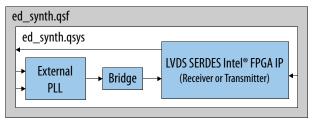

| 4.4. LVDS SERDES IP Core Design Examples                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 50                                                 |

| 4.4.1. LVDS SERDES IP Core Synthesizable Intel Quartus Prime Design Examples.                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 50                                                 |

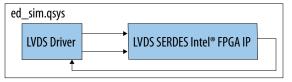

| 4.4.2. LVDS SERDES IP Core Simulation Design Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 52                                                 |

| 4.4.3. Combined LVDS SERDES IP Core Transmitter and Receiver Design Example                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                    |

| 4.4.4. LVDS SERDES IP Core Dynamic Phase Shift Design Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                    |

| 4.5. IP Migration Flow for Arria V, Cyclone V, and Stratix V Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                    |

| 4.5.1. Migrating Your ALTLVDS_TX and ALTLVDS_RX IP Cores                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 55                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                    |

| 5. LVDS SERDES Intel FPGA IP References                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 56                                                 |

| 5. LVDS SERDES Intel FPGA IP References                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <b> 56</b><br>56                                   |

| 5. LVDS SERDES Intel FPGA IP References<br>5.1. LVDS SERDES IP Core Parameter Settings<br>5.1.1. LVDS SERDES IP Core General Settings                                                                                                                                                                                                                                                                                                                                                                                           | <b> 56</b><br>56<br>56                             |

| 5. LVDS SERDES Intel FPGA IP References                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <b> 56</b><br>56<br>56<br>57                       |

| 5. LVDS SERDES Intel FPGA IP References<br>5.1. LVDS SERDES IP Core Parameter Settings<br>5.1.1. LVDS SERDES IP Core General Settings<br>5.1.2. LVDS SERDES IP Core PLL Settings                                                                                                                                                                                                                                                                                                                                                | <b>56</b><br>56<br>56<br>57<br>58                  |

| 5. LVDS SERDES Intel FPGA IP References<br>5.1. LVDS SERDES IP Core Parameter Settings<br>5.1.1. LVDS SERDES IP Core General Settings<br>5.1.2. LVDS SERDES IP Core PLL Settings<br>5.1.3. LVDS SERDES IP Core Receiver Settings                                                                                                                                                                                                                                                                                                | 56<br>56<br>56<br>57<br>58<br>61                   |

| <ul> <li>5. LVDS SERDES Intel FPGA IP References.</li> <li>5.1. LVDS SERDES IP Core Parameter Settings.</li> <li>5.1.1. LVDS SERDES IP Core General Settings.</li> <li>5.1.2. LVDS SERDES IP Core PLL Settings.</li> <li>5.1.3. LVDS SERDES IP Core Receiver Settings.</li> <li>5.1.4. LVDS SERDES IP Core Transmitter Settings.</li> <li>5.1.5. LVDS SERDES IP Core Clock Resource Summary.</li> <li>5.2. LVDS SERDES IP Core Signals.</li> </ul>                                                                              | 56<br>56<br>57<br>58<br>61<br>63<br>63             |

| <ul> <li>5. LVDS SERDES Intel FPGA IP References.</li> <li>5.1. LVDS SERDES IP Core Parameter Settings.</li> <li>5.1.1. LVDS SERDES IP Core General Settings.</li> <li>5.1.2. LVDS SERDES IP Core PLL Settings.</li> <li>5.1.3. LVDS SERDES IP Core Receiver Settings.</li> <li>5.1.4. LVDS SERDES IP Core Transmitter Settings.</li> <li>5.1.5. LVDS SERDES IP Core Clock Resource Summary.</li> </ul>                                                                                                                         | 56<br>56<br>57<br>58<br>61<br>63<br>63             |

| <ul> <li>5. LVDS SERDES Intel FPGA IP References.</li> <li>5.1. LVDS SERDES IP Core Parameter Settings.</li> <li>5.1.1. LVDS SERDES IP Core General Settings.</li> <li>5.1.2. LVDS SERDES IP Core PLL Settings.</li> <li>5.1.3. LVDS SERDES IP Core Receiver Settings.</li> <li>5.1.4. LVDS SERDES IP Core Transmitter Settings.</li> <li>5.1.5. LVDS SERDES IP Core Clock Resource Summary.</li> <li>5.2. LVDS SERDES IP Core Signals.</li> <li>5.3. Comparison of LVDS SERDES Intel FPGA IP with Stratix V SERDES.</li> </ul> | 56<br>56<br>57<br>58<br>61<br>63<br>63             |

| <ul> <li>5. LVDS SERDES Intel FPGA IP References.</li> <li>5.1. LVDS SERDES IP Core Parameter Settings.</li> <li>5.1.1. LVDS SERDES IP Core General Settings.</li> <li>5.1.2. LVDS SERDES IP Core PLL Settings.</li> <li>5.1.3. LVDS SERDES IP Core Receiver Settings.</li> <li>5.1.4. LVDS SERDES IP Core Transmitter Settings.</li> <li>5.1.5. LVDS SERDES IP Core Clock Resource Summary.</li> <li>5.2. LVDS SERDES IP Core Signals.</li> </ul>                                                                              | 56<br>56<br>57<br>58<br>61<br>63<br>63<br>66<br>67 |

Send Feedback

## **1. Intel<sup>®</sup> Stratix<sup>®</sup> 10 High-Speed LVDS I/O Overview**

The Intel<sup>®</sup> Stratix<sup>®</sup> 10 device family supports high-speed LVDS protocols through the LVDS I/O banks, the LVDS SERDES Intel FPGA IP, and the GPIO Intel FPGA IP.

Intel Stratix 10 devices support LVDS on all LVDS I/O banks:

- All LVDS I/O banks support true LVDS input with  $R_{\rm D}$  OCT and true LVDS output buffer.

- The devices do not support emulated LVDS channels.

- The devices support true differential I/O reference clock for the I/O PLL that drives the serializer/deserializer (SERDES).

- You can use each LVDS I/O pins pair as LVDS receiver or LVDS transmitter.

- The LVDS SERDES IP core can place transmitter and receiver channels in the same I/O bank by using the **Duplex Feature** option.

#### **Related Information**

- High-Speed I/O Specifications, Intel Stratix 10 Device Datasheet Lists the performance specifications of the SERDES in different modes.

- Document Revision History for the Intel Stratix 10 High-Speed LVDS I/O User Guide on page 68

- LVDS SERDES Intel FPGA IP on page 38

- GPIO Intel FPGA IP, Intel Stratix 10 General Purpose I/O User Guide

- Intel Stratix 10 High-Speed LVDS I/O User Guide Archives on page 67

Provides a list of user guides for previous versions of the LVDS SERDES Intel

FPGA IP.

## **1.1. Intel Stratix 10 LVDS SERDES Usage Modes**

#### Table 1.Usage Modes Summary of the Intel Stratix 10 LVDS SERDES

All SERDES usage modes in this table support SERDES factors of 3 to 10.

| Usage Mode   | Quick Guideline                                                                                                                                                                                                     |  |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Transmitter  | In this mode, the SERDES block acts as a serializer.                                                                                                                                                                |  |

| DPA Receiver | <ul> <li>This mode is useful for source-synchronous clocking applications.</li> <li>The dynamic phase alignment block (DPA) automatically adjusts the clock phase to achieve optimal data-to-clock skew.</li> </ul> |  |

|              | continued                                                                                                                                                                                                           |  |

Intel Corporation. All rights reserved. Agilex, Altera, Arria, Cyclone, Enpirion, Intel, the Intel logo, MAX, Nios, Quartus and Stratix words and logos are trademarks of Intel Corporation or its subsidiaries in the U.S. and/or other countries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services. \*Other names and brands may be claimed as the property of others.

1. Intel<sup>®</sup> Stratix<sup>®</sup> 10 High-Speed LVDS I/O Overview UG-S10LVDS | 2020.01.03

| Usage Mode        | Quick Guideline                                                                                                                                                                                                                                                       |  |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Non-DPA Receiver  | <ul><li>This mode is useful for source-synchronous clocking applications.</li><li>You must manage the data-to-clock skew.</li></ul>                                                                                                                                   |  |

| Soft-CDR Receiver | <ul> <li>The soft clock data recovery (soft-CDR) mode is useful for asynchronous clocking application</li> <li>An asynchronous clock drives the LVDS SERDES IP core. The IP core outputs a recovered clo<br/>from the received data.</li> </ul>                       |  |

| Bypass the SERDES | <ul> <li>You can bypass the serializer to use SERDES factor of 2 by using the GPIO IP core:</li> <li>Single data rate (SDR) mode—you do not require clocks.</li> <li>Double data rate (DDR) mode—useful for slow source-synchronous clocking applications.</li> </ul> |  |

## 1.2. Intel Stratix 10 LVDS Channels Support

The LVDS channels available vary among Intel Stratix 10 devices. In Intel Stratix 10 devices, you can use the LVDS I/O pin pairs as LVDS transmitter or receiver channels.

Refer to the Intel Stratix 10 device pin-out files for the LVDS channels counts.

#### **Related Information**

Intel Stratix 10 Device Pin-Out Files

## 1.3. Intel Stratix 10 GPIO Banks, SERDES, and DPA Locations

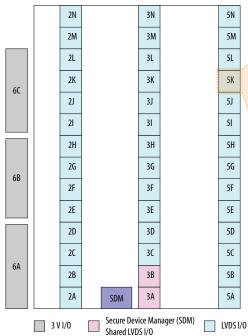

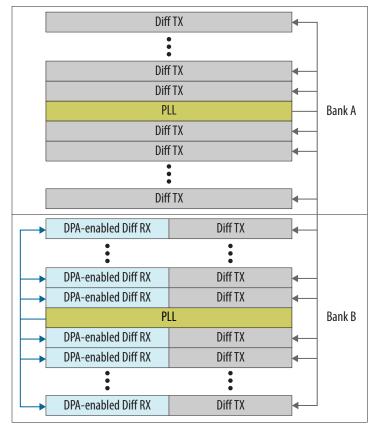

The I/O banks are located in I/O columns. Each I/O bank contains its own PLL, dynamic phase alignment (DPA), and SERDES circuitries.

#### Figure 1. I/O Bank Structure with I/O PLL, DPA, and SERDES

This figure shows an example of I/O banks in one Intel Stratix 10 device. The I/O banks availability and locations vary among Intel Stratix 10 devices.

## **Related Information**

- Secure Device Manager

- Intel Stratix 10 Device Pin-Out Files

- Provides pin-out files that lists LVDS I/O banks locations and availability in different devices and packages.

## Send Feedback

## **2. Intel Stratix 10 High-Speed LVDS I/O Architecture and** Features

The high-speed differential I/O interfaces and DPA features in Intel Stratix 10 devices provide advantages over single-ended I/Os and contribute to the achievable overall system bandwidth. Intel Stratix 10 devices support the LVDS, mini-LVDS, and reduced swing differential signaling (RSDS) differential I/O standards.

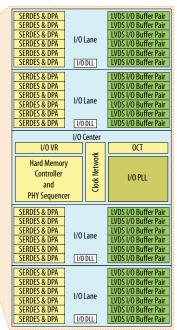

## Figure 2. I/O Bank Support for Dedicated SERDES Circuitry in Intel Stratix 10 Devices

## 2.1. Intel Stratix 10 LVDS SERDES I/O Standards Support

# Table 2. Intel Stratix 10 SERDES Transmitter and Receiver High-Speed I/O Standards Support Support

| I/O Standard | Intel Quartus <sup>®</sup> Prime Software I/O Assignment Value |

|--------------|----------------------------------------------------------------|

| True LVDS    | LVDS                                                           |

| mini-LVDS    | mini-LVDS                                                      |

| RSDS         | RSDS                                                           |

Intel Corporation. All rights reserved. Agilex, Altera, Arria, Cyclone, Enpirion, Intel, the Intel logo, MAX, Nios, Quartus and Stratix words and logos are trademarks of Intel Corporation or its subsidiaries in the U.S. and/or other countries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services. \*Other names and brands may be claimed as the property of others.

## **2.2. LVDS Transmitter Programmable I/O Features**

You can program some features of the I/O buffers according to your LVDS design requirements.

# Table 3.Summary of Supported Intel Stratix 10 LVDS Transmitter Programmable I/O<br/>Features and Settings

| Feature                     | Setting                                                                 | Assignment Name                                                | Supported I/O Standards             |

|-----------------------------|-------------------------------------------------------------------------|----------------------------------------------------------------|-------------------------------------|

| Pre-Emphasis                | 0 (disabled), 1 (enabled).<br>Default is 1.                             | Programmable Pre-emphasis                                      | <ul><li>LVDS</li><li>RSDS</li></ul> |

| Differential Output Voltage | 0 (low), 1 (medium low), 2<br>(medium high), 3 (high).<br>Default is 2. | Programmable Differential<br>Output Voltage (V <sub>OD</sub> ) | Mini-LVDS                           |

## **Related Information**

High-Speed I/O Specifications, Intel Stratix 10 Device Datasheet Lists the performance specifications of the SERDES in different modes.

## 2.2.1. Programmable Pre-Emphasis

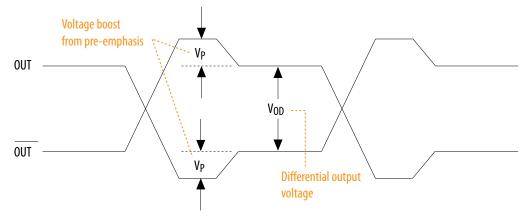

The V<sub>OD</sub> setting and the output impedance of the driver set the output current limit of a high-speed transmission signal. At a high frequency, the slew rate may not be fast enough to reach the full V<sub>OD</sub> level before the next edge, producing pattern-dependent jitter. With pre-emphasis, the output current is boosted momentarily during switching to increase the output slew rate.

Pre-emphasis increases the amplitude of the high-frequency component of the output signal, and thus helps to compensate for the frequency-dependent attenuation along the transmission line. The overshoot introduced by the extra current happens only during a change of state switching to increase the output slew rate and does not ring, unlike the overshoot caused by signal reflection. The amount of pre-emphasis required depends on the attenuation of the high-frequency component along the transmission line.

## Figure 3. Programmable Pre-Emphasis

This figure shows the LVDS output with pre-emphasis.

#### Table 4. Intel Quartus Prime Software Assignment Editor—Programmable Pre-Emphasis

This table lists the assignment name for programmable pre-emphasis and its possible values in the Intel Quartus Prime software Assignment Editor.

| Field           | Assignment                               |

|-----------------|------------------------------------------|

| То              | tx_out                                   |

| Assignment name | Programmable Pre-emphasis                |

| Allowed values  | 0 (disabled), 1 (enabled). Default is 1. |

## 2.2.2. Programmable Differential Output Voltage

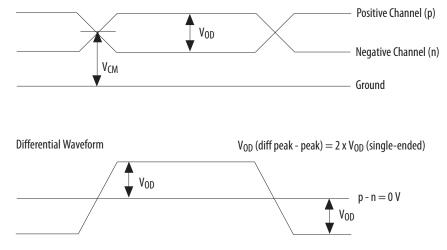

The programmable  $V_{\text{OD}}$  settings allow you to adjust the output eye opening to optimize the trace length and power consumption. A higher  $V_{\text{OD}}$  swing improves voltage margins at the receiver end, and a smaller  $V_{\text{OD}}$  swing reduces power consumption. You can statically adjust the  $V_{\text{OD}}$  of the differential signal by changing the  $V_{\text{OD}}$  settings in the Intel Quartus Prime software Assignment Editor.

## Figure 4. Differential V<sub>OD</sub>

This figure shows the  $V_{OD}$  of the differential LVDS output.

Single-Ended Waveform

## Table 5. Intel Quartus Prime Software Assignment Editor—Programmable V<sub>OD</sub>

This table lists the assignment name for programmable  $V_{\text{OD}}$  and its possible values in the Intel Quartus Prime software Assignment Editor.

| Field           | Assignment                                                           |

|-----------------|----------------------------------------------------------------------|

| То              | tx_out                                                               |

| Assignment name | Programmable Differential Output Voltage ( $V_{OD}$ )                |

| Allowed values  | 0 (low), 1 (medium low), 2 (medium high), 3 (high).<br>Default is 2. |

## **2.3. SERDES Circuitry**

Each LVDS I/O channel in Intel Stratix 10 devices has built-in serializer/deserializer (SERDES) circuitry that supports high-speed LVDS interfaces. You can configure the SERDES circuitry to support source-synchronous communication protocols such as RapidIO<sup>®</sup>, XSBI, serial peripheral interface (SPI), and asynchronous protocols.

## Figure 5. SERDES

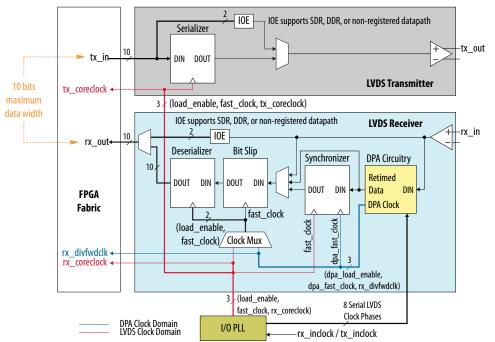

This figure shows a transmitter and receiver block diagram for the LVDS SERDES circuitry with the interface signals of the transmitter and receiver data paths. The figure shows a shared PLL between the transmitter and receiver. If the transmitter and receiver do not share the same PLL, you require two I/O PLLs. In single data rate (SDR) and double data rate (DDR) modes, the data widths are 1 and 2 bits, respectively.

The LVDS SERDES Intel FPGA IP transmitter and receiver require various clock and load enable signals from an I/O PLL. The Intel Quartus Prime software configures the PLL settings automatically. The software is also responsible for generating the various clock and load enable signals based on the input reference clock and selected data rate.

*Note:* For the maximum data rate supported by the Intel Stratix 10 devices, refer to the device datasheet.

## **Related Information**

High-Speed I/O Specifications, Intel Stratix 10 Device Datasheet Lists the performance specifications of the SERDES in different modes.

## **2.4. Differential Transmitter in Intel Stratix 10 Devices**

## Table 6. Dedicated Circuitries and Features of the Differential Transmitter

| Dedicated Circuitry / Feature | Description                         |

|-------------------------------|-------------------------------------|

| Differential I/O buffer       | Supports LVDS, mini-LVDS, and RSDS  |

| SERDES                        | 3 to 10-bit wide serializer         |

| Phase-locked loops (PLLs)     | Clocks the load and shift registers |

| Programmable V <sub>OD</sub>  | Static                              |

| Programmable pre-emphasis     | Boosts output current               |

#### **Related Information**

LVDS SERDES IP Core Signals on page 63

## 2.4.1. Transmitter Blocks in Intel Stratix 10 Devices

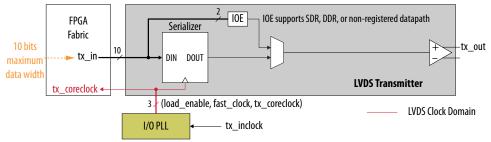

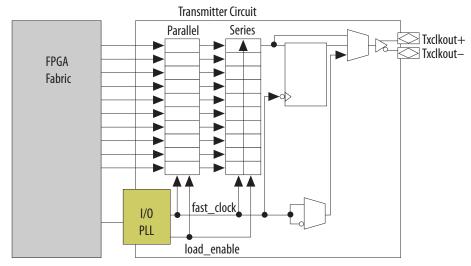

The dedicated circuitry consists of a true differential buffer, a serializer, and I/O PLLs that you can share between the transmitter and receiver. The serializer takes up to 10 bits wide parallel data from the FPGA fabric, clocks it into the load registers, and serializes it using shift registers that are clocked by the I/O PLL before sending the data to the differential buffer. The MSB of the parallel data is transmitted first.

*Note:* The PLL that drives the LVDS SERDES channel must operate in integer PLL mode. You do not need a PLL if you bypass the serializer.

#### Figure 6. LVDS Transmitter

This figure shows a block diagram of the transmitter. In SDR and DDR modes, the data width is 1 and 2 bits, respectively.

#### **Related Information**

- LVDS SERDES IP Core Signals on page 63

- Guideline: Use PLLs in Integer PLL Mode for LVDS on page 22

## **2.4.2. Serializer Bypass for DDR and SDR Operations**

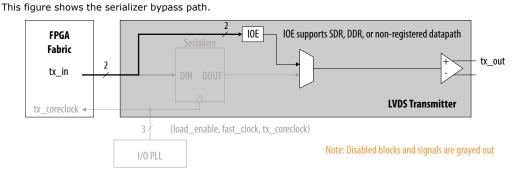

The I/O element (IOE) contains two data output registers that can each operate in either DDR or SDR mode.

You can bypass the serializer to support DDR (x2) and SDR (x1) operations to achieve a serialization factor of 2 and 1, respectively. The deserializer bypass is supported through the GPIO Intel FPGA IP.

#### Figure 7. Serializer Bypass

- In SDR mode:

- The IOE data width is 1 bit.

- Registered output path requires a clock.

- Data is passed directly through the IOE.

- In DDR mode:

- The IOE data width is 2 bits.

- The GPIO IP core requires a clock.

- tx\_inclock clocks the IOE register.

## 2.5. Differential Receiver in Intel Stratix 10 Devices

The receiver has a differential buffer and I/O PLLs that you can share among the transmitter and receiver, a DPA block, a synchronizer, a data realignment block, and a deserializer. The differential buffer can receive LVDS, mini-LVDS, and RSDS signal levels. You can statically set the I/O standard of the receiver pins to LVDS, mini-LVDS, or RSDS in the Intel Quartus Prime software Assignment Editor.

The PLL that drives the LVDS SERDES channel must operate in integer PLL mode. You Note: do not need a PLL if you bypass the deserializer

#### Table 7. **Dedicated Circuitries and Features of the Differential Receiver**

| Dedicated Circuitry / Feature | Description                                                                                |  |

|-------------------------------|--------------------------------------------------------------------------------------------|--|

| Differential I/O buffer       | Supports LVDS, mini-LVDS, and RSDS                                                         |  |

| SERDES                        | Up to 10-bit wide deserializer                                                             |  |

| Phase-locked loops (PLLs)     | Generates different phases of a clock for data synchronizer                                |  |

| Data realignment (Bit slip)   | Inserts bit latencies into serial data                                                     |  |

| DPA                           | Chooses a phase closest to the phase of the serial data                                    |  |

| Synchronizer (FIFO buffer)    | Compensate for phase differences between the data and the receiver's input reference clock |  |

| Skew adjustment               | Manual                                                                                     |  |

| On-chip termination (OCT)     | 100 $\Omega$ in LVDS I/O standards                                                         |  |

## **Related Information**

Guideline: Use PLLs in Integer PLL Mode for LVDS on page 22

## 2.5.1. Receiver Blocks in Intel Stratix 10 Devices

The Intel Stratix 10 differential receiver has the following hardware blocks:

- DPA block

- Synchronizer

- Data realignment block (bit slip)

- Deserializer

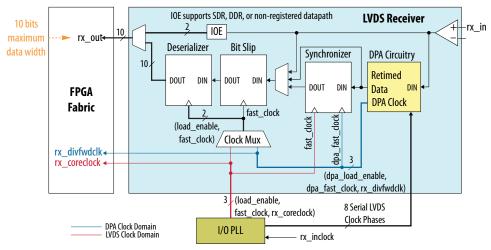

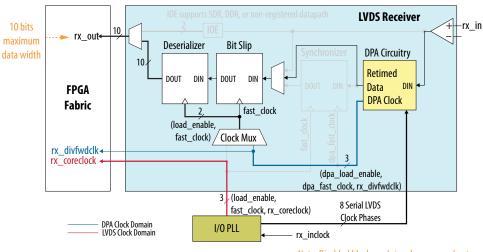

#### Figure 8. Receiver Block Diagram

This figure shows the hardware blocks of the receiver. In SDR and DDR modes, the data width from the IOE is 1 and 2 bits, respectively. The deserializer includes shift registers and parallel load registers, and sends a maximum of 10 bits to the internal logic.

## 2.5.1.1. DPA Block

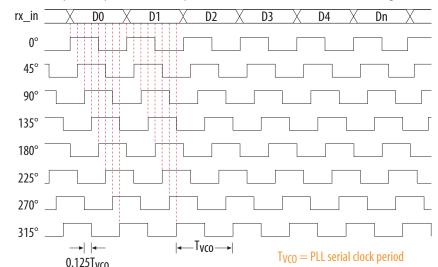

The DPA block takes in high-speed serial data from the differential input buffer and selects one of the eight phases that the I/O PLLs generate to sample the data. The DPA chooses a phase closest to the phase of the serial data. The maximum phase offset between the received data and the selected phase is 1/8 unit interval (UI)<sup>(1)</sup>, which is the maximum quantization error of the DPA. The eight phases of the clock are equally divided, offering a  $45^{\circ}$  resolution.

<sup>&</sup>lt;sup>(1)</sup> The unit interval is the period of the clock running at the serial data rate (fast clock).

## Figure 9. DPA Clock Phase to Serial Data Timing Relationship

This figure shows the possible phase relationships between the DPA clocks and the incoming serial data.

The DPA block continuously monitors the phase of the incoming serial data and selects a new clock phase if it is required. You can prevent the DPA from selecting a new clock phase by asserting the optional  $rx_dpa_hold$  port, which is available for each channel.

DPA circuitry does not require a fixed training pattern to lock to the optimum phase out of the eight phases. After reset or power up, the DPA circuitry requires transitions on the received data to lock to the optimum phase. An optional output port,  $rx_dpa_locked$ , is available to indicate an initial DPA lock condition to the optimum phase after power up or reset. Use data checkers such as a cyclic redundancy check (CRC) or diagonal interleaved parity (DIP-4) to validate the data.

An independent reset port,  $rx_dpa_reset$ , is available to reset the DPA circuitry. You must retrain the DPA circuitry after reset.

*Note:* The DPA block is bypassed in non-DPA mode.

## 2.5.1.2. Synchronizer

The synchronizer is a one-bit wide and six-bit deep FIFO buffer that compensates for the phase difference between dpa\_fast\_clock—the optimal clock that the DPA block selects—and the fast\_clock that the I/O PLLs produce. The synchronizer can only compensate for phase differences, not frequency differences, between the data and the receiver's input reference clock.

An optional port, rx\_fifo\_reset, is available to the internal logic to reset the synchronizer. The synchronizer is automatically reset when the DPA first locks to the incoming data. Intel recommends using rx\_fifo\_reset to reset the synchronizer when the data checker indicates that the received data is corrupted.

*Note:* The synchronizer circuit is bypassed in non-DPA and soft-CDR mode.

2. Intel Stratix 10 High-Speed LVDS I/O Architecture and Features UG-S10LVDS | 2020.01.03

## 2.5.1.3. Data Realignment Block (Bit Slip)

Skew in the transmitted data along with skew added by the link causes channel-tochannel skew on the received serial data streams. If you enable the DPA, the received data is captured with different clock phases on each channel. This difference may cause misalignment of the received data from channel to channel. To compensate for this channel-to-channel skew and establish the correct received word boundary at each channel, each receiver channel has a dedicated data realignment circuit that realigns the data by inserting bit latencies into the serial stream.

An optional rx\_bitslip\_ctrl port controls the bit insertion of each receiver independently controlled from the internal logic. The data slips one bit on the rising edge of rx\_bitslip\_ctrl. The requirements for the rx\_bitslip\_ctrl signal include the following items:

- The minimum pulse width is one period of the parallel clock in the logic array.

- The minimum low time between pulses is one period of the parallel clock.

- The signal is an edge-triggered signal.

- The valid data is available four parallel clock cycles after the rising edge of rx\_bitslip\_ctrl.

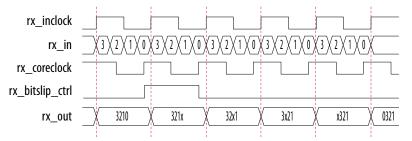

#### Figure 10. Data Realignment Timing

This figure shows receiver output (rx\_out) after one bit slip pulse with the deserialization factor set to 4.

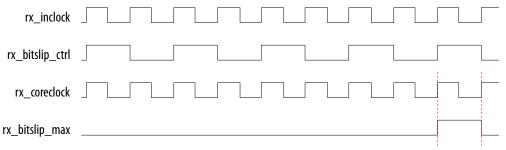

The data realignment circuit has a bit slip rollover value set to the deserialization factor. An optional status port, rx\_bitslip\_max, is available to the FPGA fabric from each channel to indicate the reaching of the preset rollover point.

#### Figure 11. Receiver Data Realignment Rollover

This figure shows a preset value of four bit cycles before rollover occurs. The rx\_bitslip\_max signal pulses for one rx\_coreclock cycle to indicate that rollover has occurred.

## 2.5.1.4. Deserializer

You can statically set the deserialization factor to x3, x4, x5, x6, x7, x8, x9, or x10 by using the Intel Quartus Prime software.

The IOE contains two data input registers that can operate in DDR or SDR mode. You can bypass the deserializer to support DDR (x2) and SDR (x1) operations. The deserializer bypass is supported through the GPIO IP core.

## Figure 12. Deserializer Bypass

This figure shows the deserializer bypass path.

- If you bypass the deserializer in SDR mode:

- The IOE data width is 1 bit.

- Registered input path requires a clock.

- Data is passed directly through the IOE.

- If you bypass the deserializer in DDR mode:

- The IOE data width is 2 bits.

- The GPIO IP core requires a clock.

- rx\_inclock clocks the IOE register. The clock must be synchronous to rx\_in.

- You must control the data-to-clock skew.

You cannot use the DPA and data realignment circuit when you bypass the deserializer.

## 2.5.2. Receiver Modes in Intel Stratix 10 Devices

The Intel Stratix 10 devices support the following receiver modes:

- Non-DPA mode

- DPA mode

- Soft-CDR mode

- *Note:* If you use DPA mode, follow the recommended initialization and reset flow. The recommended flow ensures that the DPA circuit can detect the optimum phase tap from the PLL to capture data on the receiver.

## 2.5.2.1. Non-DPA Mode

The non-DPA mode disables the DPA and synchronizer blocks. Input serial data is registered at the rising edge of the serial <code>fast\_clock</code> clock that is produced by the I/O PLLs.

The <code>fast\_clock</code> clock that is generated by the I/O PLLs clocks the data realignment and deserializer blocks.

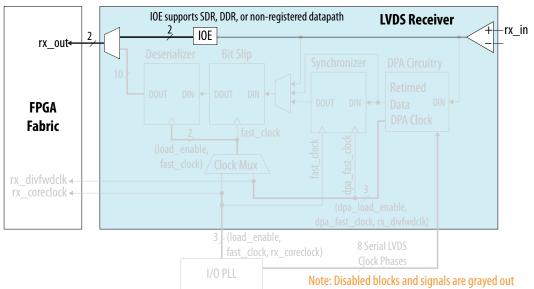

## Figure 13. Receiver Datapath in Non-DPA Mode

This figure shows the non-DPA datapath block diagram.

Note: Disabled blocks and signals are grayed out

## 2.5.2.2. DPA Mode

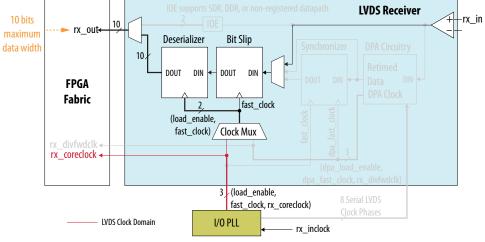

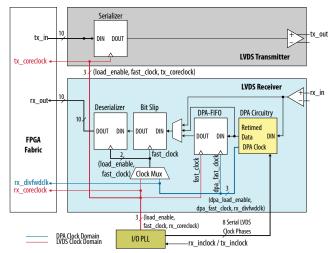

The DPA block chooses the best possible clock (dpa\_fast\_clock) from the eight fast clocks that the I/O PLL sent. This serial dpa\_fast\_clock clock is used for writing the serial data into the synchronizer. A serial fast\_clock clock is used for reading the serial data from the synchronizer. The same fast\_clock clock is used in data realignment and deserializer blocks.

## Figure 14. Receiver Datapath in DPA Mode

*Note:* In DPA mode, you must place all receiver channels of an LVDS instance in one I/O bank. Because each I/O bank has a maximum of 24 LVDS I/O buffer pairs, each LVDS instance can support a maximum of 24 DPA channels.

## 2.5.2.3. Soft-CDR Mode

The Intel Stratix 10 LVDS channel offers the soft-CDR mode to support the GbE and SGMII protocols. A receiver PLL uses the local clock source for reference.

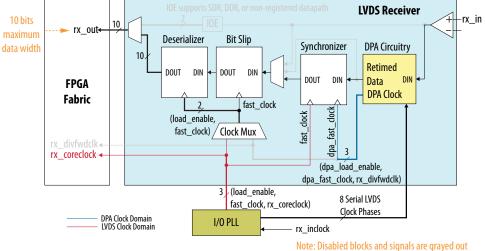

#### Figure 15. Receiver Datapath in Soft-CDR Mode

This figure shows the soft-CDR mode datapath.

Note: Disabled blocks and signals are grayed out

In soft-CDR mode, the synchronizer block is inactive. The DPA circuitry selects an optimal DPA clock phase to sample the data. This clock is used for bit slip operation and deserialization. The DPA block also forwards the selected DPA clock, divided by the deserialization factor called rx\_divfwdclk, to the FPGA fabric, along with the deserialized data. This clock signal is put on the periphery clock (PCLK) network.

If you use the soft-CDR mode, do not assert the  $rx_dpa_reset$  port after the DPA has trained. The DPA continuously chooses new phase taps from the PLL to track parts per million (PPM) differences between the reference clock and incoming data.

You can use every LVDS channel in soft-CDR mode and drive the FPGA fabric using the PCLK network in the Intel Stratix 10 device family. In soft-CDR mode, the rx\_dpa\_locked signal is not valid because the DPA continuously changes its phase to track PPM differences between the upstream transmitter and the local receiver input reference clocks. However, you can use the rx\_dpa\_locked signal to determine the initial DPA locking conditions that indicate the DPA has selected the optimal phase tap to capture the data. The rx\_dpa\_locked signal is expected to deassert when operating in soft-CDR mode. The parallel clock, rx\_coreclock, generated by the I/O PLLs, is also forwarded to the FPGA fabric.

*Note:* In soft-CDR mode, you must place all receiver channels of an LVDS instance in one I/O bank. Because each I/O bank has a maximum of 12 PCLK resources, each LVDS instance can support a maximum of 12 soft-CDR channels.

Send Feedback

## **3. Stratix 10 High-Speed LVDS I/O Design Considerations**

Follow the design considerations in this section when you are designing LVDS interfaces that use the SERDES circuitry in Intel Stratix 10 devices. Unless noted otherwise, these guidelines apply to all variants of the device family.

## **3.1. PLLs and Clocking for Intel Stratix 10 Devices**

To generate the parallel clocks (rx\_coreclock and tx\_coreclock) and high-speed clocks (fast\_clock), the Intel Stratix 10 devices provide I/O PLLs in the high-speed differential I/O receiver and transmitter channels.

## **3.1.1. Clocking Differential Transmitters**

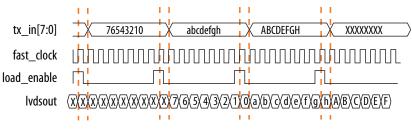

The I/O PLL generates the load enable (load\_enable) signal and the fast\_clock signal (the clock running at serial data rate) that clocks the load and shift registers. You can statically set the serialization factor to x3, x4, x5, x6, x7, x8, x9, or x10 using the Intel Quartus Prime software. The load enable signal is derived from the serialization factor setting.

You can configure any Intel Stratix 10 transmitter data channel to generate a sourcesynchronous transmitter clock output. This flexibility allows the placement of the output clock near the data outputs to simplify board layout and reduce clock-to-data skew.

Different applications often require specific clock-to-data alignments or specific datarate-to-clock-rate factors. You can specify these settings statically in the Intel Quartus Prime parameter editor:

- The transmitter can output a clock signal at the same rate as the data—with a

maximum output clock frequency that each speed grade of the device supports.

- You can divide the output clock by a factor of 1, 2, 4, 6, 8, or 10, depending on the serialization factor.

- You can set the phase of the clock in relation to the data at 0° or 180° (edge- or center-aligned). The I/O PLLs provide additional support for other phase shifts in 45° increments.

- If the tx\_outclock has a phase shift that is not a multiple of 180°, you can only place each LVDS SERDES Intel FPGA IP transmitter interface within a single I/O bank.

3. Stratix 10 High-Speed LVDS I/O Design Considerations UG-S10LVDS | 2020.01.03

#### Figure 16. Transmitter in Clock Output Mode

This figure shows the transmitter in clock output mode. In clock output mode, you can use an LVDS channel as a clock output channel.

#### **Related Information**

LVDS SERDES IP Core Transmitter Settings on page 61

## **3.1.2. Clocking Differential Receivers**

The I/O PLL receives the external clock input and generates different phases of the same clock. The DPA block automatically chooses one of the clocks from the I/O PLL and aligns the incoming data on each channel.

The synchronizer circuit is a 1-bit wide by 6-bit deep FIFO buffer that compensates for any phase difference between the DPA clock and the data realignment block. If necessary, the user-controlled data realignment circuitry inserts a single bit of latency in the serial bit stream to align to the word boundary. The deserializer includes shift registers and parallel load registers, and sends a maximum of 10 bits to the internal logic.

The physical medium connecting the transmitter and receiver LVDS channels may introduce skew between the serial data and the source-synchronous clock. The instantaneous skew between each LVDS channel and the clock also varies with the jitter on the data and clock signals as seen by the receiver. The three different modes —non-DPA, DPA, and soft-CDR—provide different options to overcome skew between the source synchronous clock (non-DPA, DPA) /reference clock (soft-CDR) and the serial data.

Non-DPA mode allows you to statically select the optimal phase between the source synchronous clock and the received serial data to compensate skew. In DPA mode, the DPA circuitry automatically chooses the best phase to compensate for the skew between the source synchronous clock and the received serial data. Soft-CDR mode provides opportunities for synchronous and asynchronous applications for chip-to-chip and short reach board-to-board applications for SGMII protocols.

*Note:* Only the non-DPA mode requires manual skew adjustment.

## **3.1.3. Guideline: LVDS Reference Clock Source**

The LVDS SERDES IP core accepts two reference clock input sources. Whichever reference clock source you select, you must ensure timing closure.

## Table 8. LVDS Reference Clock Source

| Reference Clock Input Source                              | Description                                                                                                                             | Reference Clock Promotion                      |

|-----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|

| Dedicated reference clock input within the same I/O bank. | This reference clock input source is the best choice to avoid performance and timing closure issues.                                    | Do not manually promote the reference clock.   |

| Reference clock input from other I/O banks.               | This source must come from another I/O bank and not from other sources such as the hard processor system (HPS), IOPLL IP, or other IPs. | You must manually promote the reference clock. |

To manually promote the reference clock, include this statement in your Intel Quartus Prime settings file (.qsf):

set\_instance\_assignment -name GLOBAL\_SIGNAL GLOBAL\_CLOCK -to <name of top-level

reference clock input port>

## **3.1.4. Guideline: Use PLLs in Integer PLL Mode for LVDS**

Each I/O bank has its own PLL (I/O PLL) to drive the LVDS channels. These I/O PLLs operate in integer mode only.

## **3.1.5. Guideline: Use High-Speed Clock from PLL to Clock LVDS SERDES** Only

The high-speed clock generated from the PLL is intended to clock the LVDS SERDES circuitry only. Do not use the high-speed clock to drive other logic because the allowed frequency to drive the core logic is restricted by the PLL  $F_{OUT}$  specification.

For more information about the  $F_{OUT}$  specification, refer to the device datasheet.

## **Related Information**

PLL Specifications, Intel Stratix 10 Device Datasheet

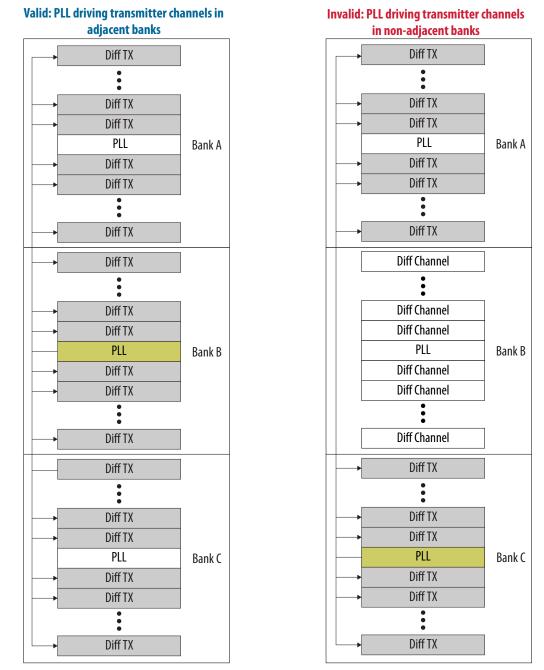

## **3.1.6. Guideline: Pin Placement for Differential Channels**

Each I/O bank contains its own PLL. The I/O bank PLL can drive all receiver and transmitter channels in the same bank, and transmitter channels in adjacent I/O banks. However, the I/O bank PLL cannot drive receiver channels in another I/O bank or transmitter channels in non-adjacent I/O banks.

## **PLLs Driving Differential Transmitter Channels**

For differential transmitters, the PLL can drive the differential transmitter channels in its own I/O bank and adjacent I/O banks. However, the PLL cannot drive the channels in a non-adjacent I/O bank.

## Figure 17. PLLs Driving Differential Transmitter Channels

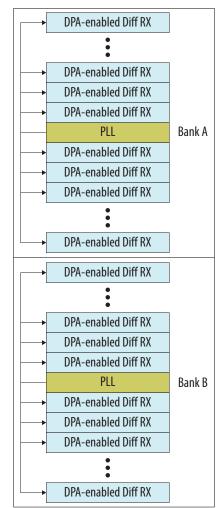

## **PLLs Driving DPA-Enabled Differential Receiver Channels**

For differential receivers, the PLL can drive all channels in the same I/O bank but cannot drive across banks.

Each differential receiver in an I/O bank has a dedicated DPA circuit to align the phase of the clock to the data phase of its associated channel. If you enable a DPA channel in a bank, you can assign the unused I/O pins in the bank to single-ended or differential I/O standards that has the same VCCIO voltage level used by the bank.

DPA usage adds some constraints to the placement of high-speed differential receiver channels. The Intel Quartus Prime compiler automatically checks the design and issues error messages if there are placement guidelines violations. Adhere to the guidelines to ensure proper high-speed I/O operation.

#### Figure 18. PLLs Driving DPA-Enabled Differential Receiver Channels

# PLLs Driving DPA-Enabled Differential Receiver and Transmitter Channels in LVDS Interface Spanning Multiple I/O Banks

If you use both differential transmitter and DPA-enabled receiver channels in a bank, the PLL can drive the transmitters spanning multiple adjacent I/O banks, but only the receivers in its own I/O bank.

## Figure 19. PLLs Driving DPA-Enabled Differential Receiver and Transmitter Channels Across I/O Banks

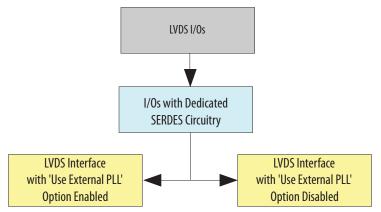

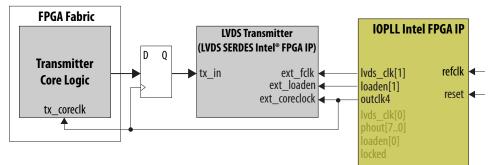

## 3.1.7. LVDS Interface with External PLL Mode

The LVDS SERDES IP core parameter editor provides an option for implementing the LVDS interface with the **Use External PLL** option. With this option enabled you can control the PLL settings, such as dynamically reconfiguring the PLL to support different data rates, dynamic phase shift, and other settings.

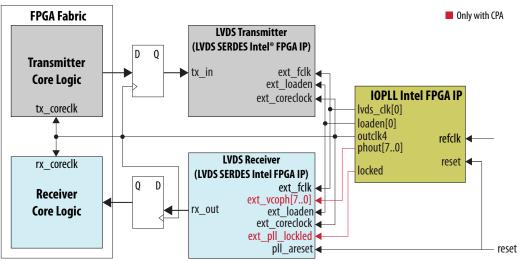

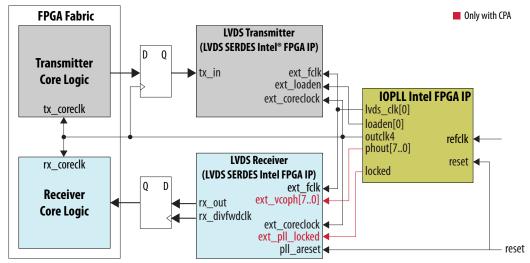

If you enable the **Use External PLL** option with the LVDS SERDES IP core transmitter and receiver, the following signals are required from the IOPLL Intel FPGA IP:

- Serial clock (fast clock) input to the SERDES of the LVDS SERDES IP core transmitter and receiver

- Load enable to the SERDES of the LVDS SERDES IP core transmitter and receiver

- Parallel clock (core clock) used to clock the transmitter FPGA fabric logic and parallel clock used for the receiver

- Asynchronous PLL reset port of the LVDS SERDES IP core receiver

- PLL VCO signal for the DPA and soft-CDR modes of the LVDS SERDES IP core receiver

The **Clock Resource Summary** tab in the LVDS SERDES IP core parameter editor provides the details for the signals in the preceding list.

Send Feedback

You must instantiate an IOPLL IP core to generate the various clocks and load enable signals. You must configure these settings in IOPLL IP core parameter editor:

- LVDS External PLL options in the Settings tab

- Output Clocks options in the PLL tab

- Compensation Mode option in the PLL tab

#### Table 9. **Compensation Mode Setting to Generate IOPLL IP Core**

When you generate the IOPLL IP core, use the PLL setting in this table for the corresponding LVDS functional mode.

| LVDS Functional Mode    | IOPLL IP Core Setting  |

|-------------------------|------------------------|

| TX, RX DPA, RX Soft-CDR | Direct mode            |

| RX non-DPA              | LVDS compensation mode |

Note:

If you are using an external PLL for a wide transmitter interface that spans multiple I/O banks, only the second pair of clocks (indexed by "[1]") from the external PLL is valid.

## **Related Information**

- Timing Analysis for the External PLL Mode on page 49

- Guideline: LVDS Transmitters and Receivers in the Same I/O Bank on page 35

- Combined LVDS SERDES IP Core Transmitter and Receiver Design Example on page 52

- LVDS SERDES IP Core PLL Settings on page 57

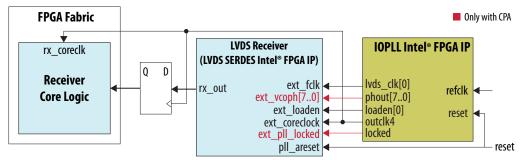

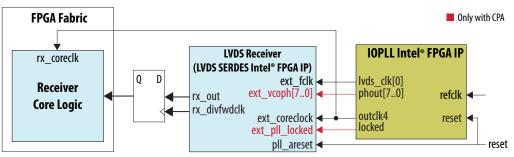

## 3.1.7.1. IOPLL IP Core Signal Interface with LVDS SERDES IP Core

#### Table 10. Signal Interface between IOPLL and LVDS SERDES IP cores

This table lists the signal interface between the output ports of the IOPLL IP core and the input ports of the LVDS SERDES IP core transmitter or receiver. The required signal interfaces differ if you turn on the Clock Phase Alignment (CPA) feature of the LVDS SERDES IP core.

| From the IOPLL IP core                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | To the LVDS SERDES IP core transmitter or receiver                                                                                   |                                                                                                                                      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Without CPA                                                                                                                          | With CPA                                                                                                                             |

| <ul> <li>lvds_clk[0] (serial clock output signal)</li> <li>Configure this signal using outclk0 in the PLL.</li> <li>Select Enable LVDS_CLK/LOADEN 0 or Enable<br/>LVDS_CLK/LOADEN 0 &amp; 1 option for the Access to<br/>PLL LVDS_CLK/LOADEN output port setting. In most<br/>cases, select Enable LVDS_CLK/LOADEN 0.</li> <li>The serial clock output can only drive ext_fclk on the<br/>LVDS SERDES IP core transmitter and receiver. This clock<br/>cannot drive the core logic.</li> </ul> | <pre>ext_fclk (serial clock input<br/>to the transmitter or<br/>receiver)</pre>                                                      | <pre>ext_fclk (serial clock input<br/>to the transmitter or<br/>receiver)</pre>                                                      |

| <ul> <li>loaden[0] (load enable output)</li> <li>Configure this signal using outclk1 in the PLL.</li> <li>Select Enable LVDS_CLK/LOADEN 0 or Enable<br/>LVDS_CLK/LOADEN 0 &amp; 1 option for the Access to<br/>PLL LVDS_CLK/LOADEN output port setting. In most<br/>cases, select Enable LVDS_CLK/LOADEN 0.</li> </ul>                                                                                                                                                                         | ext_loaden (load enable to<br>the transmitter or receiver)<br>This signal is not required<br>for LVDS receiver in soft-<br>CDR mode. | ext_loaden (load enable to<br>the transmitter or receiver)<br>This signal is not required<br>for LVDS receiver in soft-<br>CDR mode. |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                      | continued                                                                                                                            |

#### 3. Stratix 10 High-Speed LVDS I/O Design Considerations UG-S10LVDS | 2020.01.03

| From the IOPLL IP core                                                                                                                                                                                                                                                      | To the LVDS SERDES IP core transmitter or receiver                                              |                                                                                        |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|--|

|                                                                                                                                                                                                                                                                             | Without CPA                                                                                     | With CPA                                                                               |  |

| outclk4 (parallel clock output)<br>This clock is not required if you turn on <b>Use the CPA block</b><br>for improved periphery-core timing.                                                                                                                                | ext_coreclock (parallel core clock)                                                             | _                                                                                      |  |

| locked                                                                                                                                                                                                                                                                      | _                                                                                               | ext_pll_locked                                                                         |  |

| reset                                                                                                                                                                                                                                                                       | <pre>pll_areset (asynchronous PLL reset port)</pre>                                             | pll_areset (asynchronous<br>PLL reset port)                                            |  |

| <ul> <li>phout[7:0]</li> <li>This signal is required if ext_vcoph[7:0] is required.</li> <li>Configure this signal by turning on Specify VCO frequency in the PLL and specifying the VCO frequency value.</li> <li>Turn on Enable access to PLL DPA output port.</li> </ul> | ext_vcoph[7:0]<br>This signal is required only<br>for LVDS receiver in DPA or<br>soft-CDR mode. | ext_vcoph[7:0]<br>This signal is required for all<br>transmitter or receiver<br>modes. |  |

## **Related Information**

Clock Phase Alignment on page 42

Provides more information about the CPA feature of the LVDS SERDES IP core, its required conditions, and the resultant core clock duty cycles.

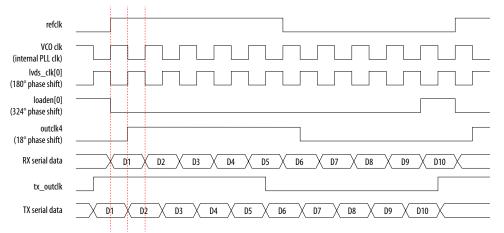

## 3.1.7.2. IOPLL Parameter Values for External PLL Mode

The following examples show the clocking requirements to generate output clocks for LVDS SERDES IP core using the IOPLL IP core. The examples set the phase shift with the assumption that the clock and data are edge aligned at the pins of the device.

*Note:* For other clock and data phase relationships, Intel recommends that you first instantiate your LVDS SERDES IP core interface without using the external PLL mode option. Compile the IP cores in the Intel Quartus Prime software and take note of the frequency, phase shift, and duty cycle settings for each clock output. Enter these settings in the IOPLL IP core parameter editor and then connect the appropriate output to the LVDS SERDES IP cores.

## Table 11. Example: Generating Output Clocks Using an IOPLL IP core (Receiver in Non-DPA Mode)

This table lists the parameter values that you can set in the IOPLL IP core parameter editor to generate three output clocks using an IOPLL IP core if you are using the non-DPA receiver.

| Parameter   | outclk0<br>(Connects as lvds_clk[0] to<br>the ext_fclk port of LVDS<br>SERDES IP core transmitter or<br>receiver) | outclk1<br>(Connects as loaden[0] to the<br>ext_loaden port of LVDS<br>SERDES IP core transmitter or<br>receiver) | outclk4 <sup>(2)</sup><br>(Used as the core clock for the<br>parallel data registers for both<br>transmitter and receiver, and<br>connects to the<br>ext_coreclock port of LVDS<br>SERDES IP core) |

|-------------|-------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Frequency   | data rate                                                                                                         | data rate/serialization factor                                                                                    | data rate/serialization factor                                                                                                                                                                     |

| Phase shift | 180°                                                                                                              | [(deserialization factor – 1)/<br>deserialization factor] x 360°                                                  | 180/serialization factor<br>(outclk0 phase shift divided by<br>the serialization factor)                                                                                                           |

| Duty cycle  | 50%                                                                                                               | 100/serialization factor                                                                                          | 50%                                                                                                                                                                                                |

<sup>&</sup>lt;sup>(2)</sup> Not required if your turn on **Use the CPA block for improved periphery-core timing**.

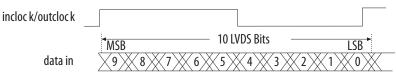

The calculations for phase shift, using the RSKM equation, assume that the input clock and serial data are edge aligned. Introducing a phase shift of 180° to sampling clock (outclk0) ensures that the input data is center-aligned with respect to the outclk0, as shown in the following figure.

# Table 12. Example: Generating Output Clocks Using an IOPLL IP core (Receiver in DPA or Soft-CDR Mode)

This table lists the parameter values that you can set in the IOPLL IP core parameter editor to generate four output clocks using an IOPLL IP core if you are using the DPA or soft-CDR receiver.

| Parameter   | outclk0<br>(Connects as<br>lvds_clk[0] to the<br>ext_fclk port of LVDS<br>SERDES IP core<br>transmitter or<br>receiver) | outclk1<br>(Connects as<br>loaden[0] to the<br>ext_loaden port of<br>LVDS SERDES IP core<br>transmitter or<br>receiver)<br>Not required for the<br>soft-CDR receiver. | outclk4 <sup>(2)</sup><br>(Used as the core clock<br>for the parallel data<br>registers for both<br>transmitter and<br>receiver, and connects<br>to the ext_coreclock<br>port of LVDS SERDES<br>IP core) | VCO Frequency<br>(Connects as<br>phout[7:0] to the<br>ext_vcoph[7:0] port<br>of LVDS SERDES IP<br>core) |

|-------------|-------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|

| Frequency   | data rate                                                                                                               | data rate/serialization<br>factor                                                                                                                                     | data rate/serialization<br>factor                                                                                                                                                                        | data rate                                                                                               |

| Phase shift | 180°                                                                                                                    | [(deserialization factor -<br>1)/deserialization factor]<br>x 360°                                                                                                    | 180/serialization factor<br>(outclk0 phase shift<br>divided by the<br>serialization factor)                                                                                                              | _                                                                                                       |

| Duty cycle  | 50%                                                                                                                     | 100/serialization factor                                                                                                                                              | 50%                                                                                                                                                                                                      | —                                                                                                       |

# Table 13.Example: Generating Output Clocks Using a Shared IOPLL IP core for<br/>Transmitter Spanning Multiple Banks Shared with Receiver Channels<br/>(Receiver in DPA or Soft-CDR Mode)

This table lists the parameter values that you can set in the IOPLL IP core parameter editor to generate six output clocks using an IOPLL IP core. Use these settings if you use transmitter channels that span multiple banks shared with receiver channels in DPA or soft-CDR mode.

| Parameter   | outclk0<br>(Connects as<br>lvds_clk[0] to the<br>ext_fclk port of LVDS<br>SERDES IP core<br>receiver)<br>outclk2<br>(Connects as<br>lvds_clk[1] to the<br>ext_fclk port of LVDS<br>SERDES IP core<br>transmitter) | outclk1<br>(Connects as<br>loaden[0] to the<br>ext_loaden port of<br>LVDS SERDES IP core<br>receiver)<br>Not required for the<br>soft-CDR receiver.<br>outclk3<br>(Connects as<br>loaden[1] to the<br>ext_loaden port of<br>LVDS SERDES IP core<br>transmitter) | outclk4 <sup>(2)</sup><br>(Used as the core clock<br>for the parallel data<br>registers for both<br>transmitter and<br>receiver, and connects<br>to the ext_coreclock<br>port of LVDS SERDES<br>IP core) | VCO Frequency<br>(Connects as<br>phout[7:0] to the<br>ext_vcoph[7:0] port<br>of LVDS SERDES IP<br>core) |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|

| Frequency   | data rate                                                                                                                                                                                                         | data rate/serialization factor                                                                                                                                                                                                                                  | data rate/serialization<br>factor                                                                                                                                                                        | data rate                                                                                               |

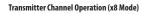

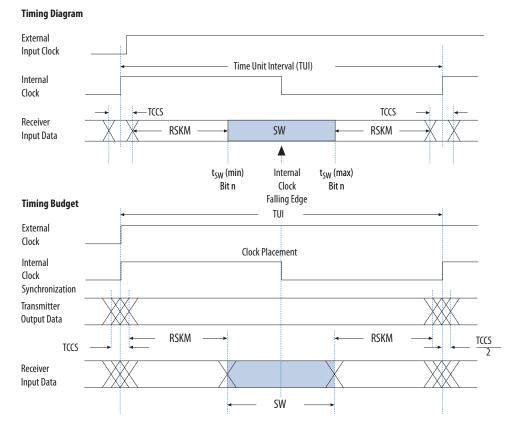

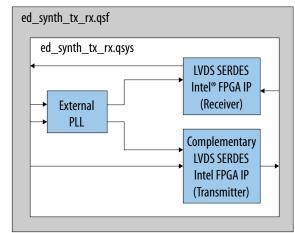

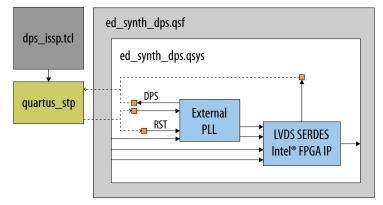

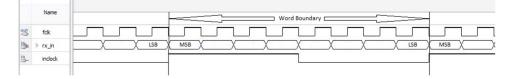

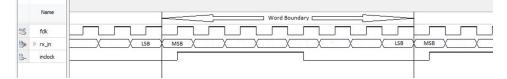

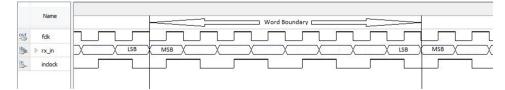

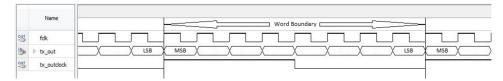

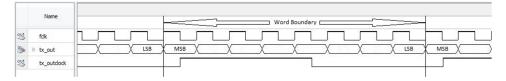

| Phase shift | 180°                                                                                                                                                                                                              | [(deserialization factor -<br>1)/deserialization factor]<br>x 360°                                                                                                                                                                                              | 180/serialization factor<br>(outclk0 phase shift<br>divided by the<br>serialization factor)                                                                                                              | _                                                                                                       |