# **Intel Stratix 10 Configuration User Guide**

Updated for Intel® Quartus® Prime Design Suite: 19.4

UG-S10CONFIG | 2020.03.06 Latest document on the web: PDF | HTML

# **Contents**

| 1. Intel® Stratix® 10 Configuration User Guide                                                          | 4  |

|---------------------------------------------------------------------------------------------------------|----|

|                                                                                                         |    |

| 1.1. Intel® Stratix® 10 Configuration Overview                                                          |    |

| 1.1.1. Configuration and Related Signals                                                                |    |

| 1.1.2. Intel Download Cables Supporting Configuration in Intel Stratix 10 Devices                       |    |

| 1.2. Intel Stratix 10 Configuration Architecture                                                        | 12 |

| 1.2.1. Secure Device Manager                                                                            | 13 |

| 2. Intel Stratix 10 Configuration Details                                                               | 18 |

| 2.1. Intel Stratix 10 Configuration Timing Diagram                                                      | 18 |

| 2.2. Configuration Flow Diagram                                                                         |    |

| 2.3. Additional Clock Requirements for HPS, PCIe, eSRAM, and HBM2                                       |    |

| 2.4. Intel Stratix 10 Configuration Pins                                                                |    |

| 2.4.1. SDM Pin Mapping                                                                                  |    |

| 2.4.2. MSEL Settings                                                                                    |    |

| 2.4.3. Device Configuration Pins for Optional Configuration Signals                                     |    |

| 2.5. Configuration Clocks                                                                               |    |

| 2.5.1. Setting Configuration Clock Source                                                               |    |

| 2.5.2. OSC CLK 1 Clock Input                                                                            |    |

|                                                                                                         |    |

| 3. Intel Stratix 10 Configuration Schemes                                                               | 40 |

| 3.1. Avalon-ST Configuration                                                                            | 40 |

| 3.1.1. Avalon-ST Configuration Scheme Hardware Components and File Types                                |    |

| 3.1.2. Enabling Avalon-ST Device Configuration                                                          |    |

| 3.1.3. The AVST_READY Signal                                                                            |    |

| 3.1.4. RBF Configuration File Format                                                                    |    |

| 3.1.5. Avalon-ST Single-Device Configuration                                                            |    |

| 3.1.6. Debugging Guidelines for the Avalon-ST Configuration Scheme                                      |    |

| 3.1.7. QSF Assignments for Avalon-ST x8                                                                 |    |

| 3.1.8. QSF Assignments for Avalon-ST x16                                                                |    |

| 3.1.9. QSF Assignments for Avalon-ST x32                                                                |    |

| 3.1.10. IP for Use with the Avalon-ST Configuration Scheme: Intel FPGA Parallel Flash Loader II IP Core |    |

| 3.2. AS Configuration                                                                                   |    |

|                                                                                                         |    |

### Contents

|           | 3.2.1. AS Configuration Scheme Hardware Components and File Types   |     |

|-----------|---------------------------------------------------------------------|-----|

|           | 3.2.2. AS Single-Device Configuration                               | 88  |

|           | 3.2.3. AS Using Multiple Serial Flash Devices                       |     |

|           | 3.2.4. AS Configuration Timing Parameters                           | 92  |

|           | 3.2.5. Maximum Allowable External AS_DATA Pin Skew Delay Guidelines | 93  |

|           | 3.2.6. Programming Serial Flash Devices                             | 94  |

|           | 3.2.7. Serial Flash Memory Layout                                   | 98  |

|           | 3.2.8. AS_CLK                                                       | 99  |

|           | 3.2.9. Active Serial Configuration Software Settings                | 100 |

|           | 3.2.10. Intel Quartus Prime Programming Steps                       |     |

|           | 3.2.11. Debugging Guidelines for the AS Configuration Scheme        |     |

|           | 3.2.12. QSF Assignments for AS                                      | 107 |

|           | 3.3. SD/MMC Configuration                                           | 110 |

|           | 3.3.1. SD/MMC Single-Device Configuration                           | 111 |

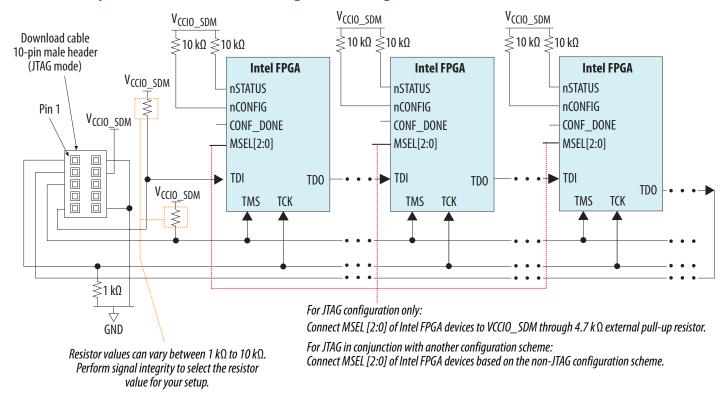

|           | 3.4. JTAG Configuration                                             |     |

|           | 3.4.1. JTAG Configuration Scheme Hardware Components and File Types | 114 |

|           | 3.4.2. JTAG Device Configuration                                    |     |

|           | 3.4.3. JTAG Multi-Device Configuration                              |     |

|           | 3.4.4. Debugging Guidelines for the JTAG Configuration Scheme       | 119 |

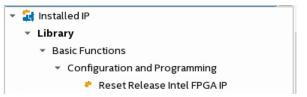

| 4.        | Including the Reset Release Intel FPGA IP in Your Design            | 122 |

|           | 4.1. Understanding the Reset Release IP Requirement                 |     |

|           | 4.2. Assigning INIT_DONE To an SDM_IO Pin                           |     |

|           | 4.3. Instantiating the Reset Release IP In Your Design              |     |

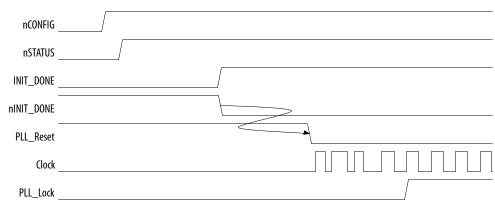

|           | 4.4. Gating the PLL Reset Signal                                    | 126 |

|           | 4.5. Guidance When Using Partial Reconfiguration (PR)               | 127 |

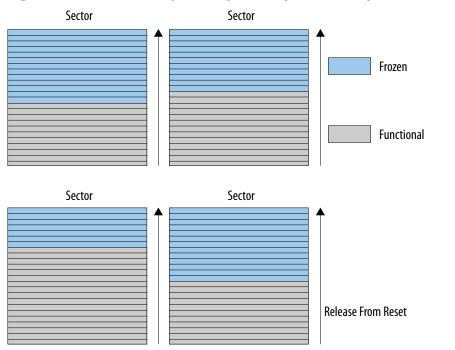

|           | 4.6. Detailed Description of Device Configuration                   | 127 |

|           | 4.6.1. Device Initialization                                        | 129 |

|           | 4.6.2. Preventing Register Initialization During Power-On           | 129 |

|           | 4.6.3. Embedded Memory Block Initial Conditions                     | 131 |

|           | 4.6.4. Protecting State Machine Logic                               | 131 |

| <b>5.</b> | Remote System Update (RSU)                                          | 133 |

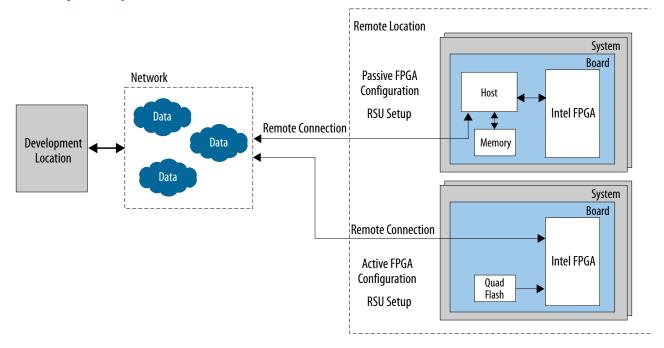

|           | 5.1. Remote System Update Functional Description                    |     |

|           | 5.1.1. RSU Glossary                                                 |     |

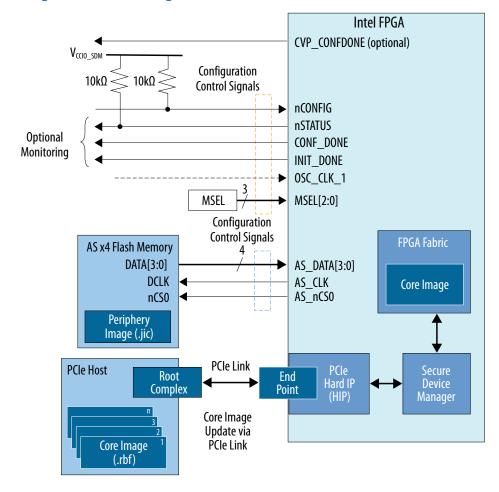

|           | 5.1.2. Remote System Update Using AS Configuration                  |     |

|           | /                                                                   |     |

| 5.1.3. Remote System Update Configuration Images                                                      |     |

|-------------------------------------------------------------------------------------------------------|-----|

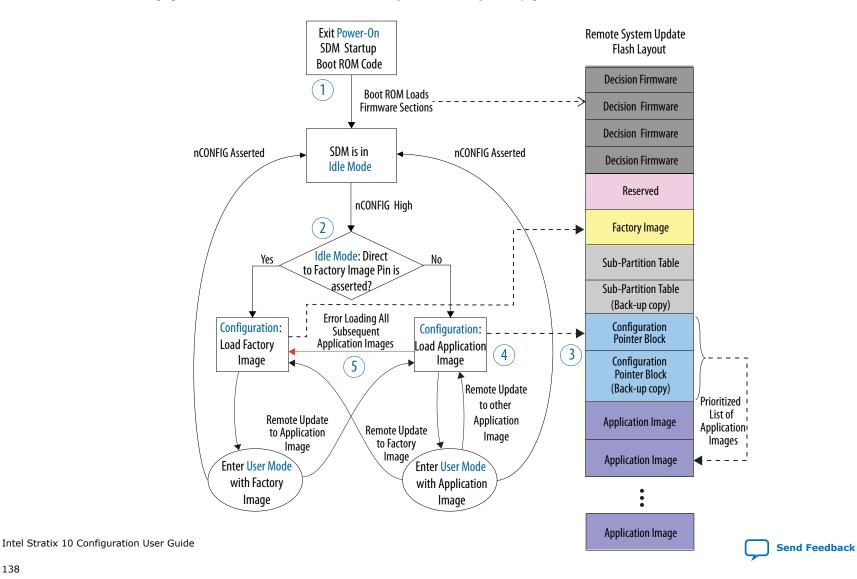

| 5.1.4. Remote System Update Configuration Sequence                                                    | 138 |

| 5.1.5. RSU Recovery from Corrupted Images                                                             | 139 |

| 5.1.6. Updates with the Factory Update Image                                                          | 142 |

| 5.2. Guidelines for Performing Remote System Update Functions for Non-HPS                             | 143 |

| 5.3. Commands and Responses                                                                           |     |

| 5.3.1. Operation Commands                                                                             |     |

| 5.3.2. Error Code Responses                                                                           | 154 |

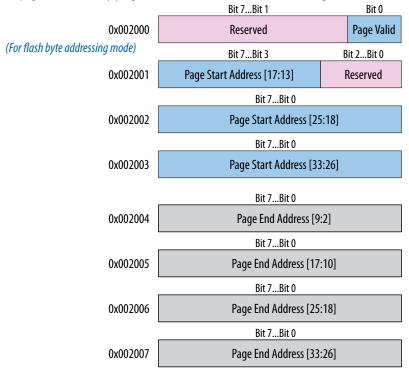

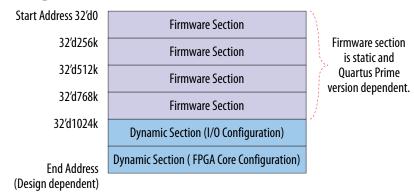

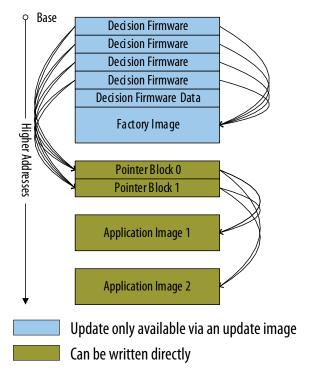

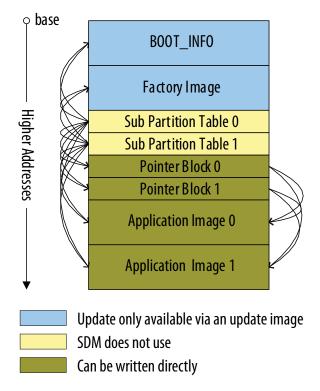

| 5.4. Quad SPI Flash Layout                                                                            | 155 |

| 5.4.1. High Level Flash Layout                                                                        |     |

| 5.4.2. Detailed Quad SPI Flash Layout                                                                 |     |

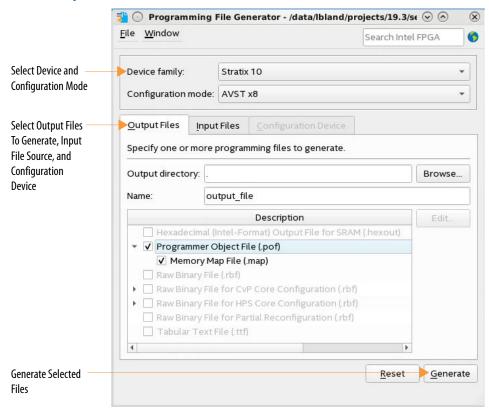

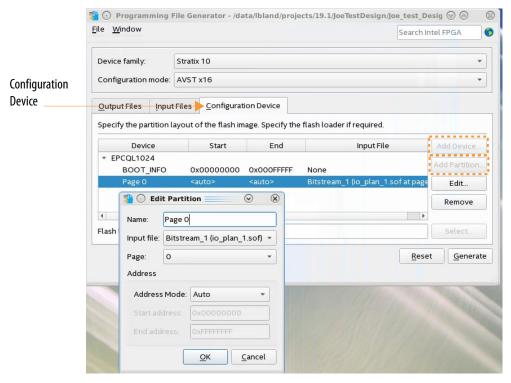

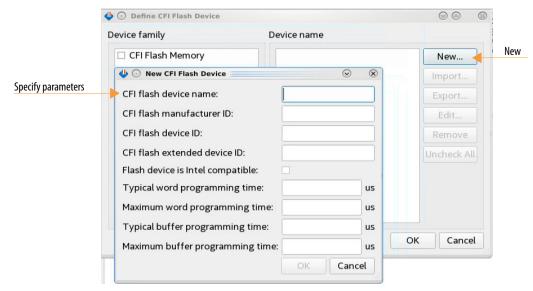

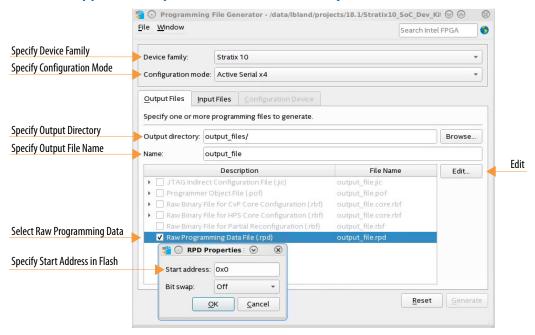

| 5.5. Generating Remote System Update Image Files Using the Programming File Generator                 | 164 |

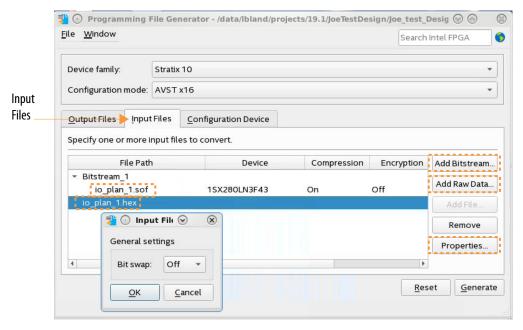

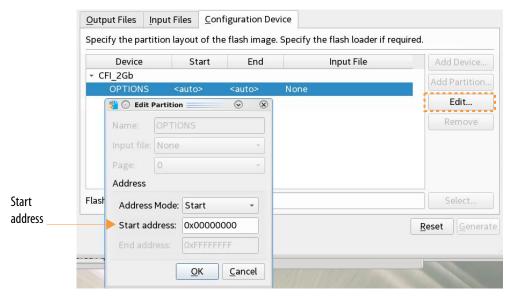

| 5.5.1. Generating the Initial RSU Image                                                               |     |

| 5.5.2. Generating an Application Image                                                                | 167 |

| 5.5.3. Generating a Factory Update Image                                                              | 169 |

| 5.5.4. Command Sequence To Perform Quad SPI Operations                                                | 173 |

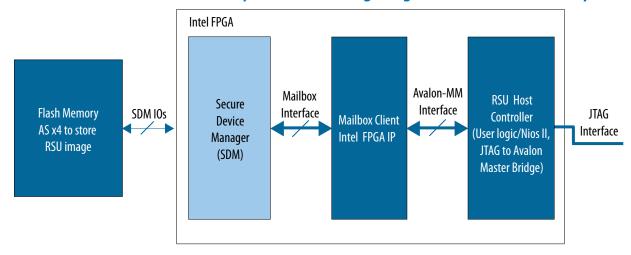

| 5.6. Remote System Update from FPGA Core Example                                                      | 173 |

| 5.6.1. Prerequisites                                                                                  | 174 |

| 5.6.2. Creating Initial Flash Image Containing Bitstreams for Factory Image and One Application Image | 175 |

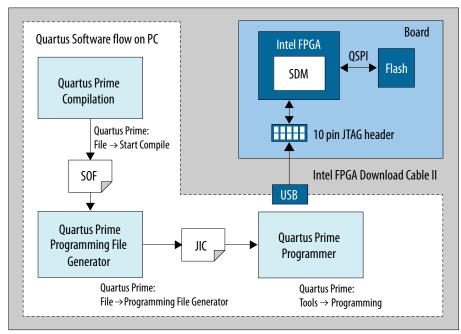

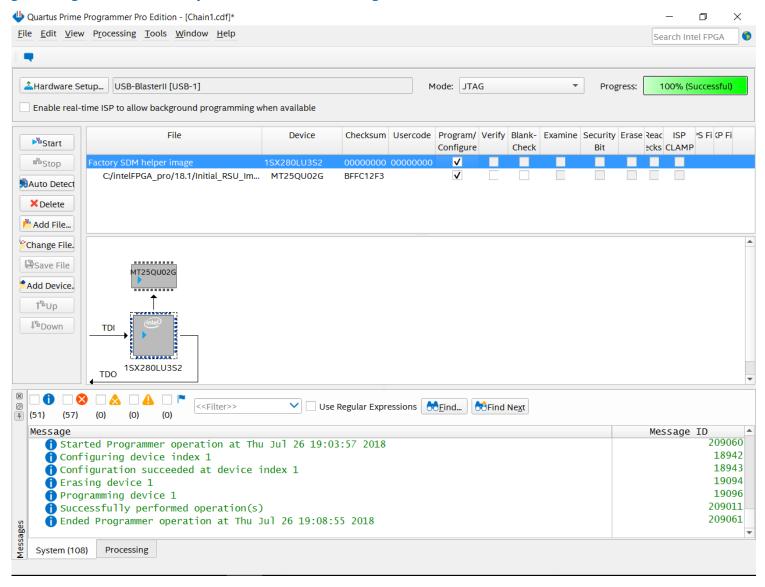

| 5.6.3. Programming Flash Memory with the Initial Remote System Update Image                           | 179 |

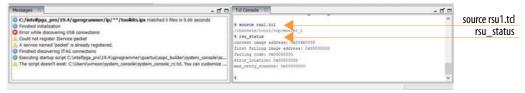

| 5.6.4. Reconfiguring the Device with an Application or Factory Image                                  | 181 |

| 5.6.5. Adding an Application Image                                                                    | 182 |

| 5.6.6. Removing an Application Image                                                                  | 186 |

| 6. Intel Stratix 10 Configuration Features                                                            | 100 |

|                                                                                                       |     |

| 6.1. Device Security                                                                                  |     |

| 6.2. Configuration via Protocol                                                                       |     |

| 6.3. Partial Reconfiguration                                                                          |     |

| 7. Intel Stratix 10 Debugging Guide                                                                   | 191 |

| 7.1. Configuration Debugging Checklist                                                                |     |

| 7.2. Intel Stratix 10 Configuration Architecture Overview                                             |     |

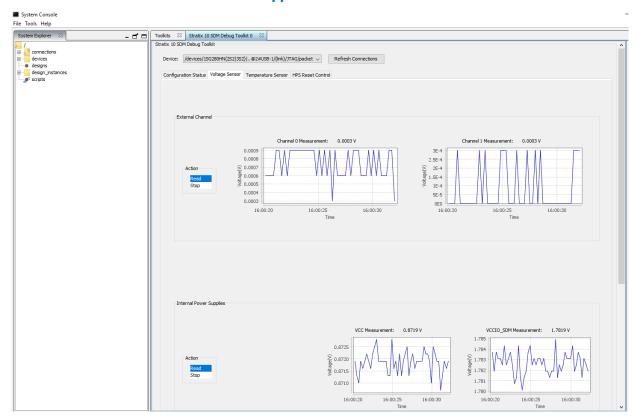

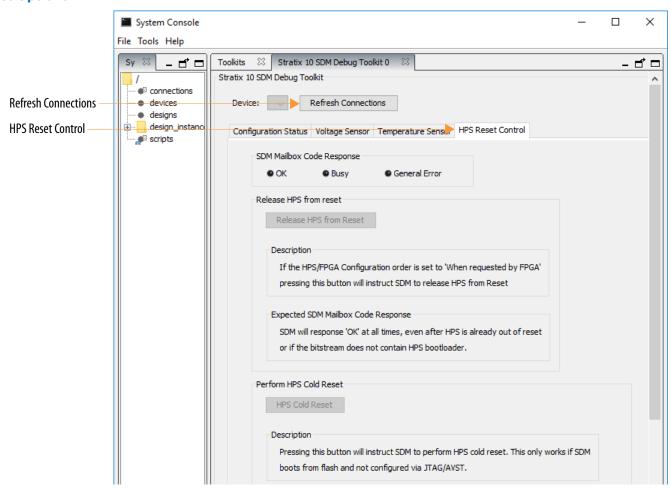

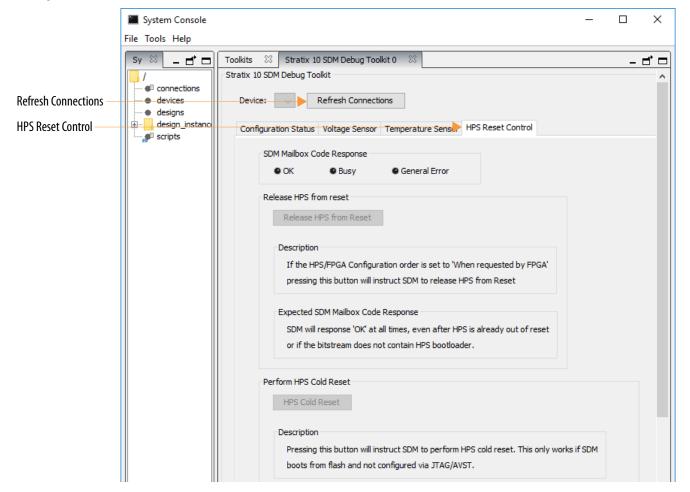

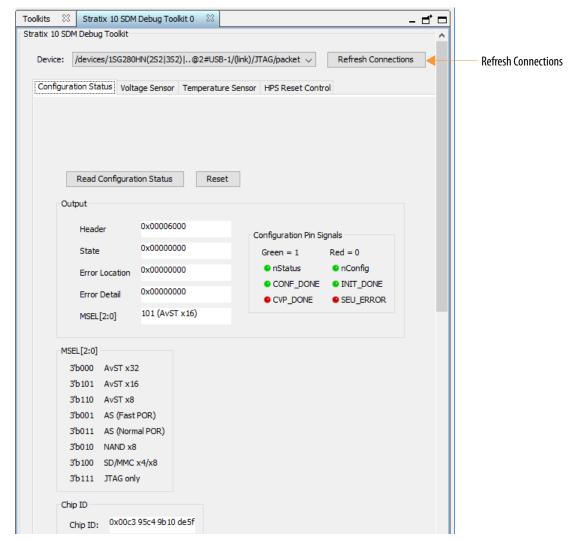

| 7.3. SDM Debug Toolkit Overview                                                                       |     |

| 7.3.1. Using the SDM Debug Toolkit                                                                    |     |

| 7.4. Configuration Pin Differences from Previous Device Families                                      |     |

| 7.5. Configuration File Format Differences                                                            |     |

| · · · · · · · · · · · · · · · · · · ·                                                                 |     |

#### Contents

| Document Revision History for the Intel Stratix 10 Configuration User Guide | 210 |

|-----------------------------------------------------------------------------|-----|

| Intel Stratix 10 Configuration User Guide Archives                          | 209 |

| 7.9.4. SDM_IO Pins                                                          |     |

| 7.9.3. CONF_DONE and INIT_DONE                                              |     |

| 7.9.2. nSTATUS                                                              | 205 |

| 7.9.1. nCONFIG                                                              |     |

| 7.9. Understanding and Troubleshooting Configuration Pin Behavior           |     |

| 7.8. E-Tile Transceivers May Fail To Configure                              |     |

| 7.7. Reading the Unique 64-Bit CHIP ID                                      | 202 |

| 7.6. Understanding SEUs                                                     |     |

# 1. Intel<sup>®</sup> Stratix<sup>®</sup> 10 Configuration User Guide

# 1.1. Intel® Stratix® 10 Configuration Overview

All Intel® Stratix® 10 devices include a Secure Device Manager (SDM) to manage FPGA configuration and security. The SDM provides a failsafe, strongly authenticated, programmable security mode for device configuration. Previous FPGA families include a fixed state machine to manage device configuration.

The Intel Quartus<sup>®</sup> Prime software also provides flexible and robust security features to protect sensitive data, intellectual property, and the device itself under both remote and physical attacks. Configuration bitstream authentication ensures that the firmware and configuration bitstream are from a trusted source. Encryption prevents theft of intellectual property. The Intel Quartus Prime software also compresses FPGA bitstreams, reducing memory utilization.

Intel describes configuration schemes from the point-of-view of the FPGA. Intel Stratix 10 devices support active and passive configuration schemes. In active configuration schemes the FPGA acts as the master and the external memory acts as a slave device. In passive configuration schemes an external host acts as the master and controls configuration. The FPGA acts as the slave device. All Intel Stratix 10 configuration schemes support design security, and partial reconfiguration. All Intel Stratix 10 active configuration schemes support remote system update (RSU) with quad SPI flash memory. To implement RSU in passive configuration schemes, an external controller must store and drive the configuration bitstream.

Intel Stratix 10 devices support the following configuration schemes:

- Avalon<sup>®</sup> Streaming (Avalon-ST)

- JTAG

- Configuration via Protocol (CvP)

- Active Serial (AS) normal and fast modes

- Secure Digital and Multi Media Card (SD/MMC)

Intel Corporation. All rights reserved. Agilex, Altera, Arria, Cyclone, Enpirion, Intel, the Intel logo, MAX, Nios, Quartus and Stratix words and logos are trademarks of Intel Corporation or its subsidiaries in the U.S. and/or other countries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

Table 1. Intel Stratix 10 Configuration Data Width, Clock Rates, and Data Rates

| Configura | ation Scheme                     | Data Width (bits)         | MSEL[2:0] |

|-----------|----------------------------------|---------------------------|-----------|

|           |                                  | 32                        | 000       |

|           | Avalon-ST                        | 16                        | 101       |

| Passive   |                                  | 8                         | 110       |

| -         | JTAG                             | 1                         | 111       |

|           | Configuration via Protocol (CvP) | x1, x2, x4, x8, x16 lanes | 001(1)    |

|           | SD/MMC                           | 4/8                       | 100       |

| Active    | AS - fast mode                   | 4                         | 001       |

|           | AS - normal mode                 | 4                         | 011       |

#### **Avalon-ST**

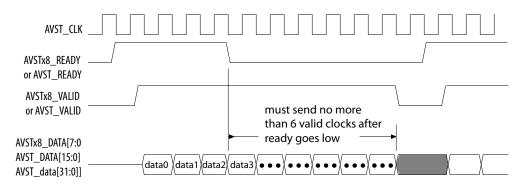

The Avalon-ST configuration scheme is a passive configuration scheme. Avalon-ST is the fastest configuration scheme for Intel Stratix 10 devices. Avalon-ST configuration supports x8, x16, and x32 modes. The x16 and x32 bit modes use general-purpose I/Os (GPIOs) for configuration. The x8 bit mode uses dedicated SDM I/O pins.

#### Note:

The AVST\_data[15:0], AVST\_data[31:0], AVST\_clk, and AVST\_valid use dual-purpose GPIOs. You can use these pins as regular I/Os after the device enters user mode.

Avalon-ST supports backpressure using the AVST\_READY and AVST\_VALID pins. Because the time to decompress the incoming bitstream varies, backpressure support is necessary to transfer data to the Intel Stratix 10 device. For more information about the Avalon-ST refer to the *Avalon Interface Specifications*.

#### **JTAG**

You can configure the Intel Stratix 10 device using the dedicated JTAG pins. The JTAG port provides seamless access to many useful tools and functions. In addition to configuring the Intel Stratix 10, you use the JTAG port for debugging with Signal Tap or the System Console tools.

<sup>(1)</sup> Before you can use CvP you must configure either the periphery image or full image configuration via the AS scheme. Then you can configure the core image using CvP.

The JTAG port has the highest priority and overrides the MSEL pin settings. Consequently, you can configure the Intel Stratix 10 device over JTAG even if the MSEL pins specify a different configuration scheme unless you disabled JTAG for security reasons.

#### **CVP**

CvP uses an external PCIe\* host device as a Root Port to configure the Intel Stratix 10 device over the PCIe link. You can specify up to a x16 PCIe link. Typically, the bitstream compression ratio and the SDM input buffer data rate, not the PCIe link width, limit the configuration data rate. Intel Stratix 10 devices support two CvP modes, CvP init and CvP update.

CvP initialization process includes the following two steps:

- 1. CvP configures the FPGA periphery image which includes I/O and hard IP blocks, including the PCIe IP. CvP uses quad SPI memory in AS x4 mode to configure the FPGA fabric. Because the PCIe IP is in the periphery image, PCIe link training establishes the PCIe link of the CvP PCIe IP before the core fabric configures.

- 2. The host device uses the CvP PCIe link to configure your design in the core fabric.

CvP update mode updates the FPGA core image using the PCIe link already established from a previous full chip configuration or CvP init configuration. After the Intel Stratix 10 enters user mode, you can use the CvP update mode to reconfigure the FPGA fabric. This mode has the following advantages:

- Allows reprogramming of the core to run different algorithms.

- Provides a mechanism for standard updates as a part of a release process.

- Customizes core processing for different components that are part of a complex system.

For both CvP Init and CvP Update modes, the maximum data rate depends on the PCIe generation and number of lanes.

For Intel Stratix 10 SoC devices, CvP is only supported in FPGA configuration first mode.

For more information refer to the Intel Stratix 10 Configuration via Protocol (CVP) Implementation User Guide.

#### **AS Normal Mode**

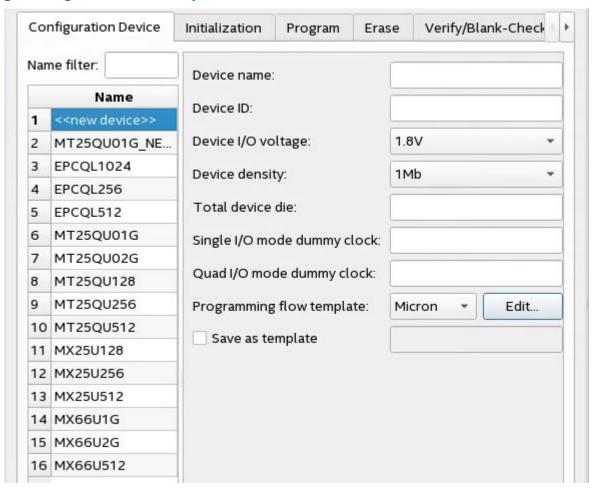

Active Serial x4 or AS x4 or Quad SPI is an active configuration scheme that supports flash memories capable of three- and four-byte addressing. Upon power up, the SDM boots from a boot ROM which uses three-byte addressing to load the configuration firmware from the Quad SPI flash. After the configuration firmware loads, the Quad SPI flash operates using four-byte addressing for the rest of the configuration process. This mode supports Intel's serial flash configuration memory solution for the following third-party flash devices:

- Micron MT25QU128, MT25QU256, MT25QU512, MT25QU01G, MT25QU02G

- Macronix MX25U128, MX25U256, MX25U512, MX66U512, MX66U1G, MX66U2G

Refer to the Supported Flash Devices for Intel Stratix 10 Devices for complete list of supported flash devices.

#### **AS Fast Mode**

The only difference between AS normal mode and fast mode is speed. Use AS fast mode when configuration timing is a concern. This mode does not delay for 10 ms before beginning configuration. Use this mode to meet the 100 ms of power up requirement for PCIe or for other systems with strict timing requirements.

In AS fast mode, the power-on sequence must ensure that the quad SPI flash memory is out of reset before the SDM because the Intel Stratix 10 device accesses flash memory immediately after exiting reset. The power supply must be able to provide an equally fast ramp up for the Intel Stratix 10 device and the external AS x4 flash devices. Failing to meet this requirement causes the SDM to report that the memory is missing. Consequently, configuration fails.

Refer to the Intel Stratix 10 Device Family Pin Connection Guidelines and AN692: Power Sequencing Considerations for Intel Cyclone<sup>®</sup> 10 GX, Intel Arria<sup>®</sup> 10, and Intel Stratix 10 Devices for additional details.

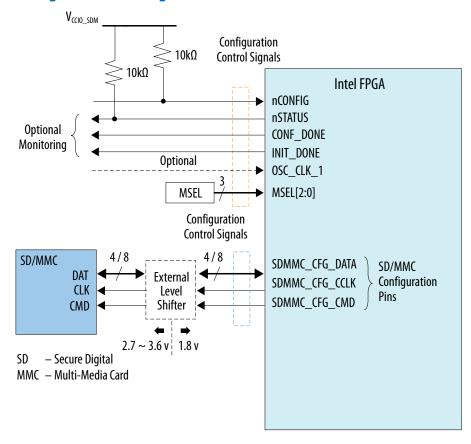

#### SD/MMC

SD/MMC is an active configuration scheme. The Intel Stratix 10 SDM can initiate configuration from SD, Secure Digital High Capacity (SDHC\*), Secure Digital Extended Capacity (SDXC\*), MMC cards, and eMMC devices. The advantages of this mode are cost, capacity, availability, portability, and compatibility. Because the SDM I/O configuration pins in Intel Stratix 10 devices operate at 1.8 volt an intermediate voltage level shifter may be required to interface with the higher voltage I/Os in SD/MMC devices.

*Note:* The SD/MMC configuration scheme is not supported in the current release.

#### **Related Information**

Avalon Interface Specifications

- Device Configuration Support Center

- Intel Stratix 10 Configuration via Protocol (CvP) Implementation User Guide

- Intel Stratix 10 Device Datasheet (Core and HPS)

- Supported Flash Devices for Intel Stratix 10 Devices

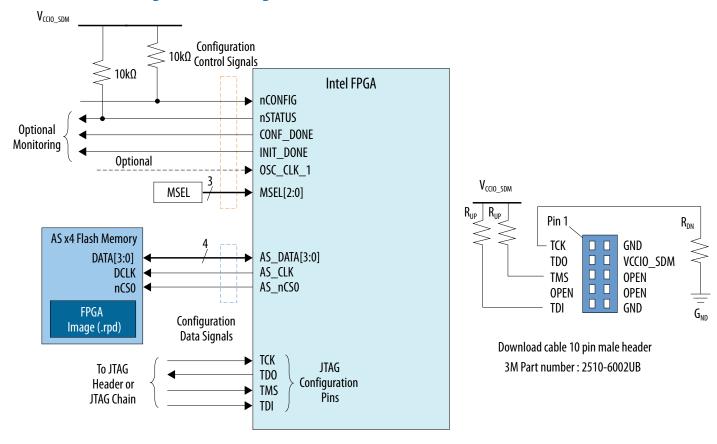

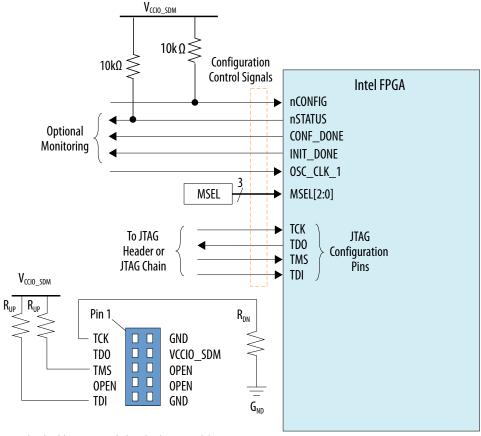

# 1.1.1. Configuration and Related Signals

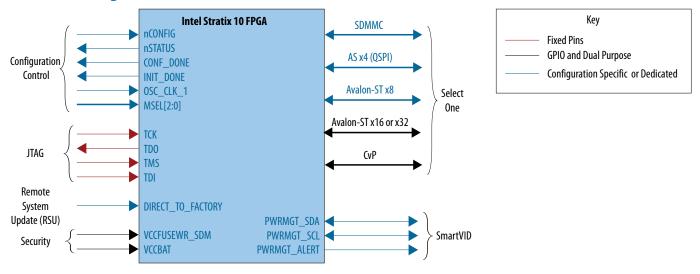

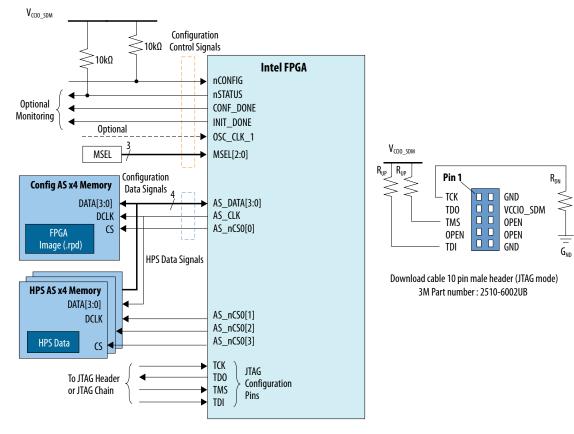

The following figure shows the configuration interfaces and configuration-related device functions. Pins shown in dark blue use dedicated SDM I/Os. Pins shown in black use general purpose I/Os (GPIOs). Pins shown in red are dedicated JTAG I/Os.

You specify SDM I/O pin functions using the **Device ➤ Configuration ➤ Device and Pin Options** dialog box in the Intel Quartus Prime software.

Figure 1. Intel Stratix 10 Configuration Interfaces

This user guide discusses most of the interfaces shown in the figure. Refer to the separate *Intel Stratix 10 Configuration via Protocol (CvP) Implementation User Guide* and *Intel Stratix 10 Power Management User Guide* for more information about those features.

#### **Related Information**

- SDM Pin Mapping on page 26

- Intel Stratix 10 Configuration via Protocol (CvP) Implementation User Guide

- Intel Stratix 10 Power Management User Guide

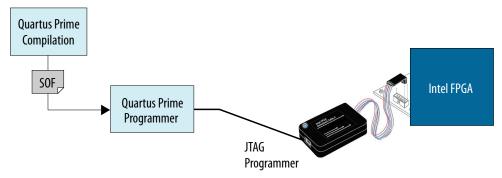

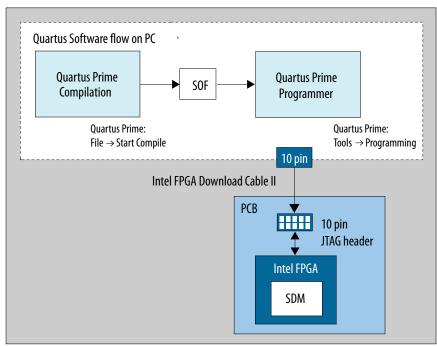

# 1.1.2. Intel Download Cables Supporting Configuration in Intel Stratix 10 Devices

Intel provides the following cables to download your design to the Intel Stratix 10 device on the PCB. Download cables support prototyping activity by providing detailed debug messages via Intel Quartus Prime Programmer. You must use Intel download cables for advanced debugging using the Signal Tap logic analyzer or the System Console tools.

Table 2. Intel Stratix 10-Supported Download Cable Capabilities

| Download Cable                                               | Protocol Support Intel Stratix 10 Device | Cable Connection to PCB                           |

|--------------------------------------------------------------|------------------------------------------|---------------------------------------------------|

| Intel FPGA Download Cable II (formerly the USB-Blaster II)   | JTAG, AS                                 | 10-pin female plug<br>3M Part number: 2510-6002UB |

| Intel FPGA Ethernet Cable (formerly the Ethernet Blaster II) | JTAG, AS                                 | 10-pin female plug                                |

The Intel FPGAs and Programmable Devices / Download Cables provides more information about the download cables and includes links to the user guides for all cables listed in the table above.

# 1.2. Intel Stratix 10 Configuration Architecture

The Secure Device Manager (SDM) is a triple-redundant processor-based module that manages configuration and the security features of Intel Stratix 10 devices. The SDM is available on all Intel Stratix 10 FPGAs and SoC devices.

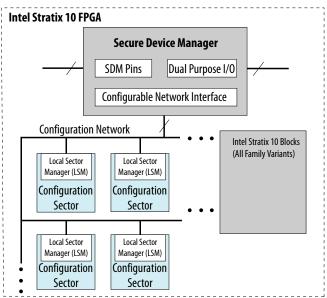

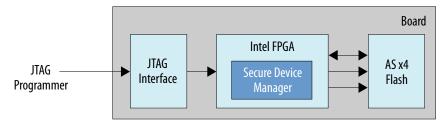

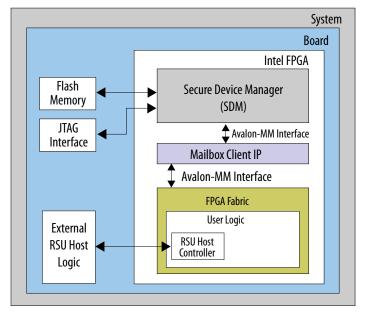

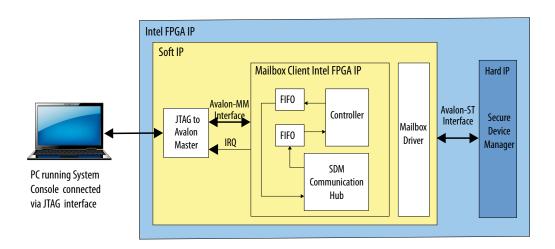

The block diagram below provides an overview of the Intel Stratix 10 configuration architecture which includes the following blocks:

- SDM: More information about the SDM is contained in later sections.

- Configuration network: The SDM uses this dedicated, parallel configuration network to distribute the configuration bitstream to Local Sector Managers (LSMs). You cannot access this network.

- LSMs: The LSM is a microprocessor. Each configuration sector includes an LSM. The LSM parses configuration bitstream and configures the logic elements for its sector. After configuration, the LSM performs the following functions:

- Monitors for single event upsets at the sector level

- Processes responses to single event upsets (SEUs)

- Performs hashing or integrity checks in real time

- Specific blocks for Intel Stratix 10 variants:

- SX devices include the hard processor system (HPS) in addition to FPGA logic.

- MX devices include a High Bandwidth Memory (HBM2) in addition to FPGA logic.

- GX devices include FPGA logic and L- and H-Tile transceivers.

- TX devices include FPGA logic and E- and H-Tile transceivers.

Figure 2. Intel Stratix 10 Configuration Architecture Block Diagram

# 1.2.1. Secure Device Manager

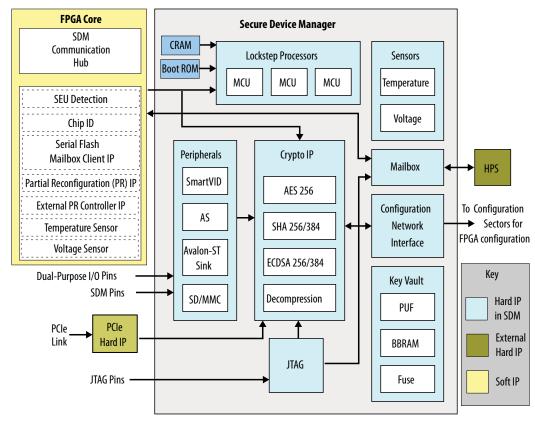

The SDM comprises peripherals, cryptographic IP and sensors, boot ROM, triple-redundant lockstep processors, and other blocks shown the block diagram below. The SDM performs and manages the following security functions:

- Configuration bitstream authentication: After power-on during startup, the SDM triple-redundant lockstep processors run code from the boot ROM. The boot ROM code authenticates the Intel-generated configuration firmware and configuration bitstream, ensuring that configuration bitstream is from a trusted source. All Intel Stratix 10 support authentication.

- Encryption: Encryption protects the configuration bitstream or confidential data from unauthorized third-party access.

- Side channel attack protection: Side channel attack protection guards AES Key and confidential data under non-intrusive attacks.

- Integrity checking: Integrity checking verifies that an accidental event has not corrupted the configuration bitstream. This function is active, even if you do not enable authentication.

These security features are available in Intel Stratix 10 devices that support advanced security. The following table lists the security features that Intel Stratix 10 devices support.

| Intel Stratix 10 | Authentication | Advanced Security  |

|------------------|----------------|--------------------|

| GX               | Yes            | -AS suffix devices |

| SX               | Yes            | -AS suffix devices |

| MX               | Yes            | -AS suffix devices |

| TX               | Yes            | -AS suffix devices |

| DX               | Yes            | Yes                |

Figure 3. SDM Block Diagram

Here is an overview of the additional functions the SDM controls:

- The Power Management block consists of a voltage and temperature sensor which enables the SmartVID feature via an external PMBus voltage regulator when you select -V devices.

- The AES/SHA and other Crypto Accelerator blocks implement secure configuration and boot.

- The Key Vault provides volatile and non-volatile cryptographic key storage. To mitigate potential side-channel attacks, crypto functions that use keys require a special hardware storage mechanism.

- The AS and SD/MMC configuration flash controllers enable active configuration schemes via dedicated SDM pins.

- The x8 Avalon-ST configuration scheme uses SDM I/O pins. The x16 and x32 Avalon-ST configuration schemes use dedicated SDM I/O pins and dual-purpose I/O pins. Refer to the SDM Pin Mapping for more information.

- To reduce configuration file size and support smaller memory sizes, and enable faster configuration, the Intel Quartus Prime software compresses the configuration data. All Intel Stratix 10 devices compress the configuration bitstream. You cannot disable this feature. If specify an encrypted configuration bitstream, the Intel Quartus Prime Pro Edition software compresses the configuration bitstream before encryption.

- A specific PCIe block included in the Intel Stratix 10 device supports CvP.

#### **Related Information**

- SDM Pin Mapping on page 26

- Intel Stratix 10 Device Feature Status Description

For information about security features that are currently supported and security features that are planned to be supported in the future.

### 1.2.1.1. Updating the SDM Firmware

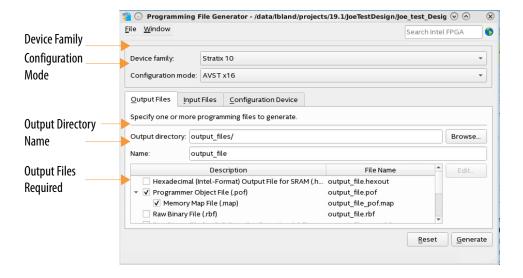

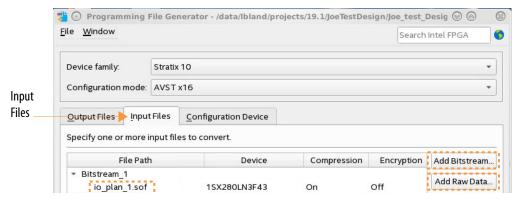

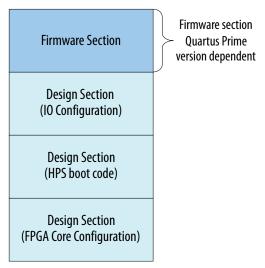

When you generate a configuration bitstream using the **File** ➤ **Programming File Generator** menu item, the bitstream assembler adds all firmware (including the SDM firmware) that matches the Intel Quartus Prime Pro Edition Release to the .sof.

Depending on the configuration scheme you specify the resulting file can be in any of the following formats:

- Raw Binary File, .rbf

- Programmer Object File, .pof

- JTAG Indirect Configuration, .jic

- Raw Programming Data, .rpd

- Jam\*Standard Test and Programming Language (STAPL) STAPL, . jam

- Jam Byte Code, . jbc

Newer versions of the Intel Quartus Prime software typically include new or updated SDM features implemented in firmware. When regenerating your configuration bitstream, Intel recommends using the latest version of the Intel Quartus Prime Pro Edition Software which includes the latest firmware. You do not need to recompile your .sof to use the firmware from a newer version of the Intel Quartus Prime Pro Edition Software. You can simply regenerate your configuration bitstream with the new version of the **Programming File Generator**.

### 1.2.1.2. Specifying Boot Order for Intel Stratix 10 SoC Devices

For Intel Stratix 10 SoC devices you can specify the configuration order, choosing either the FPGA First or the Hard Processor System (HPS) First options. When you select the FPGA First option, the SDM fully configures the FPGA, then configures the HPS SDRAM pins, loads the HPS first stage boot loader (FSBL) and takes the HPS out of reset. In this mode the fabric begins functioning just before the HPS exits reset. This use guide defines a state when the FPGA is functional. Configuration and initialization are complete.

When you select the HPS First option, the SDM first configures the HPS SDRAM pins, loads the HPS FSBL and takes the HPS out of reset. Then the HPS configures the FPGA I/O and FPGA fabric at a later time. The HPS First option has the following advantages:

- Minimizes the amount of SDM flash memory required.

- Minimizes the amount of time it takes for the HPS software to be up and running.

- Supports FPGA reconfiguration while the HPS is running.

For more information about specifying configuration order refer to the FPGA Configuration First Mode and HPS Boot First Mode chapters in the Intel Stratix 10 SoC FPGA Boot User Guide.

#### **Related Information**

- FPGA Configuration First Mode

- HPS Boot First Mode

# 2. Intel Stratix 10 Configuration Details

# 2.1. Intel Stratix 10 Configuration Timing Diagram

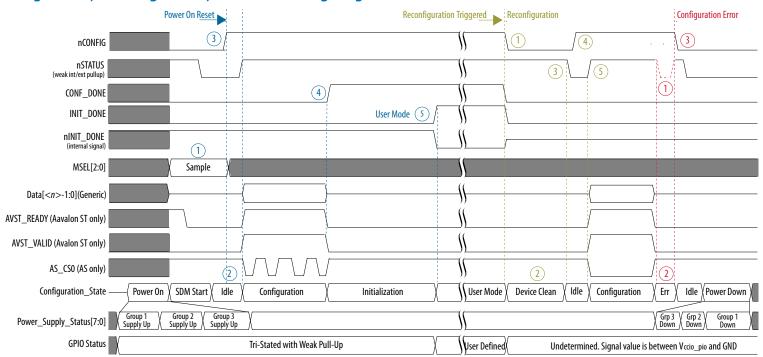

Figure 4. Configuration, Reconfiguration, and Error Timing Diagram

Intel Corporation. All rights reserved. Agilex, Altera, Arria, Cyclone, Enpirion, Intel, the Intel logo, MAX, Nios, Quartus and Stratix words and logos are trademarks of Intel Corporation or its subsidiaries in the U.S. and/or other countries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

The SDM drives Intel Stratix 10 device configuration.

### **Initial Configuration Timing**

The first section of the figure shows the expected timing for initial configuration after a normal power-on reset . Initially, the application logic drives the nCONFIG signal low (POR). Under normal conditions nSTATUS follows nCONFIG because nSTATUS reflects the current configuration state. nCONFIG must only change when it has the same value as nSTATUS.

When an error occurs, nSTATUS pulses low for approximately 1 ms and asserts high when the device is ready to accept reconfiguration.

The numbers in the *Initial Configuration* part of the timing diagram mark the following events:

- 1. The SDM boots up and samples the MSEL signals to determine the specified FPGA configuration scheme. The SDM does not sample the MSEL pins again until the next power cycle.

- 2. With the nCONFIG signal low, the SDM enters Idle mode after booting.

- 3. When the external host drives nCONFIG signal high, the SDM initiates configuration. The SDM drives the nSTATUS signal high, signaling the beginning of FPGA configuration. The SDM receives the configuration bitstream on the interface that the MSEL bus specified in Step 1 The diagram shows AVST\_READY and AVST\_VALID continuously high. It is possible for AVST\_READY to deassert which would require AVST\_VALID to deassert within six cycles.

- 4. The SDM drives the CONF DONE signal high, indicating the SDM received the bitstream successfully.

- 5. When the Intel Stratix 10 device asserts INIT\_DONE to indicate the FPGA has entered user mode. GPIO pins exit the high impedance state. The time between the assertion of CONF\_DONE and INIT\_DONE is variable. For FPGA First configuration, INIT\_DONE asserts after initialization of the FPGA fabric, including registers and state machines. For HPS first configuration, the HPS application controls the time between CONF\_DONE and INIT\_DONE. INIT\_DONE does not assert until after the software running on the HPS such as U-Boot or the operating system (OS) initiates the configuration, the FPGA configures and enters user mode..

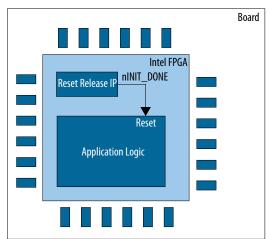

The entire device does not enter user mode simultaneously. Intel requires you to include the Including the Reset Release Intel FPGA IP in Your Design on page 122 in your design. Use the nINIT\_DONE output of the Reset Release Intel FPGA IP to hold your application logic in the reset state until the entire FPGA fabric is in user mode. Failure to include this IP in your design may result in intermittent application logic failures.

### **Reconfiguration Timing**

The second event the timing diagram illustrates the Intel Stratix 10 device reconfiguration. If you change the MSEL setting after power-on, you must power-cycle the Intel Stratix 10. Power cycling forces the SDM to sample the MSEL pins before reconfiguring the device.

The numbers in the *Reconfiguration* part of the timing diagram mark the following events:

- 1. The external host drives nCONFIG signal low.

- 2. The SDM initiates device cleaning.

- 3. The SDM drives the nSTATUS signal low when device cleaning is complete.

- 4. The external host drives the nCONFIG signal high to initiate reconfiguration.

- 5. The SDM drives the nSTATUS signal high signaling the device is ready for reconfiguration and starts to reconfigure.

#### **Configuration Error**

The numbers in the Configuration Error part of the timing diagram mark the following events:

- 1. The SDM drives nSTATUS signal low for 1 ms -0.5 ms/+9.5 ms to indicate a configuration error. The Intel Stratix 10 device does not assert CONF DONE indicating that configuration did not complete successfully.

- 2. The SDM enters the error state. During the error state, nCONFIG should be in the high state. The application must drive nCONFIG from high to low and then from low to high to restart configuration.

- 3. The SDM enters the idle state. The external host deasserts nCONFIG. The device is ready for reconfiguration by driving a low to high transition on nCONFIG. You can also power cycle the device by following the device power down sequence.

Note: The nCONFIG signal can only change levels when it has the same value as nSTATUS. This restriction means that when nSTATUS = 1, nCONFIG can transition from 1 to 0. When nSTATUS = 0, nCONFIG can transition from 0 to 1.

Apart from error reporting, nSTATUS only changes to follow nCONFIG.

### **Power Supply Status**

The power-on reset (POR) holds the Intel Stratix 10 device in the reset state until the power supply outputs are within the recommended operating range.  $t_{RAMP}$  defines the maximum power supply ramp time. If POR does not meet the  $t_{RAMP}$  time, the Intel Stratix 10 device I/O pins and programming registers remain tri-stated.

For more information about POR refer to the *Intel Stratix 10 Power Management User Guide*. For more information about  $t_{RAMP}$  refer to the *Intel Stratix 10 datasheet*.

#### **Related Information**

- Quad SPI Flash Layout on page 155

For information about storing firmware, configuration, and application data in flash devices.

- Intel Intel Stratix 10 Device Datasheet

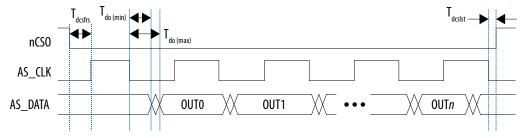

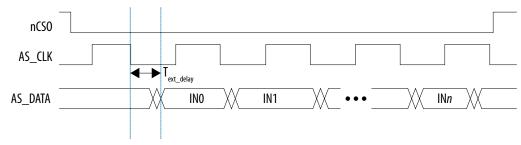

For the following timing diagrams that define set-up, hold, and propagation delay timing parameters: AS Configuration

Serial Output Timing Diagram, AS Configuration Serial Input Timing Diagram, and Avalon ST Configuration Timing

Diagram.

- Intel Intel Stratix 10 Power Management User Guide

- Should clocks and resets in user logic be gated until the configuration process is completed in Intel Stratix 10?

# 2.2. Configuration Flow Diagram

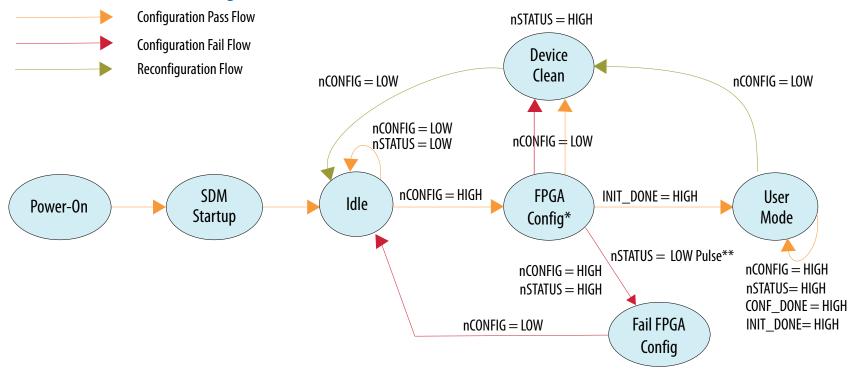

This topic describes the configuration flow for Intel Stratix 10 devices.

Figure 5. Intel Stratix 10 FPGA Configuration Flow

<sup>\*</sup>FPGA first mode, fabric configuration begins immediately. HPS first mode, HPS configures the fabric.

<sup>\*\*</sup>minimum = 0.5 ms, maximum = 10.0 ms

### **Power Up**

- The Intel Stratix 10 power supplies power following the guidelines in the *Power-Up Sequence Requirements for Intel Stratix 10 Devices* section of the *Intel Stratix 10 Power Management User Guide*.

- A device-wide power-on reset (POR) asserts after the power supplies reach the correct operating voltages. The external power supply ramp must not be slower than the minimum ramping rate until the supplies reach the operating voltage.

- During configuration, internal circuitry pulls the SDM\_IO0, SDM\_IO8, and SDM\_IO16 low internally. Internal circuitry pulls the remaining SDM\_IO pins to a weak high.

- After POR, internal circuitry also pulls all GPIO pins to a weak high until the device enters user mode.

### **SDM Startup**

- The SDM samples the MSEL pins during power-on.

- If MSEL is set to JTAG, the SDM remains in the Startup state.

- The SDM runs firmware stored in the on-chip boot ROM and enters the Idle state until the host drives nCONFIG high. The host should not drive nCONFIG high before all clocks are stable.

#### Idle

• The SDM remains in IDLE state until the external host initiates configuration by driving the nCONFIG pin from low to high. Alternatively, the SDM enters the idle state after it exits the error state.

#### **Configuration Start**

- After the SDM receives a configuration initiation request (nCONFIG = HIGH), the SDM signals the beginning of configuration by driving the nSTATUS pin high.

- Upon receiving configuration data, the SDM performs authentication, decryption and decompression.

- The nCONFIG pin remains high during configuration and in user mode. The host monitors the nSTATUS pin continuously for configuration errors.

#### **Configuration Pass**

- The SDM drives the CONF DONE pin high after successfully receiving full bitstream.

- The CONF DONE pin signals an external host that bitstream transfer is successful.

### **Configuration Error**

- A low pulse on the nSTATUS pin indicates a configuration error.

- Errors require reconfiguration.

- After a low pulse indicating an error, configuration stops. The nSTATUS pin remains high.

- Following an error, the SDM drives nSTATUS low after the external host drives nCONFIG low.

- The device enters Idle state after the nSTATUS pin recovers to initial pre-configuration low state.

#### **User Mode**

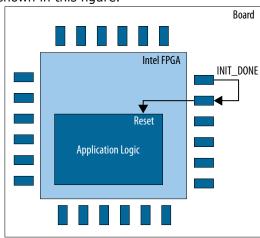

- The SDM drives the INIT\_DONE pin high after initializing internal registers and releases GPIO pins from the high impedance state. The device enters user mode. The entire device does not enter user mode simultaneously. Intel requires you to include the *Reset Release* in your design. Use the nINIT\_DONE output of the Reset Release Intel FPGA IP to hold your application logic in the reset state until the entire FPGA fabric is in user mode. Failure to include this IP in your design may result in intermittent application logic failures.

- The nCONFIG pin should remain high in user mode.

- You may re-configure the device by driving nCONFIG pin from low to high.

#### **Device Clean**

- In the Device Clean state the design stops functioning.

- Device cleaning zeros out all configuration data.

- The Intel Stratix 10 device drives CONF\_DONE and INIT\_DONE low.

- The SDM drives the nSTATUS pin low when device cleaning completes.

#### **JTAG Configuration**

Note:

You can perform JTAG configuration anytime from any state except the power-on and SDM startup state. The Intel Stratix 10 device cancels the previous configuration and accepts the reconfiguration data from the JTAG interface. The nconfiguration must be held in a stable state during JTAG configuration. A falling edge on the nconfiguration cancels the JTAG configuration.

Note:

The SDM only samples the MSEL pins at power-on. The SDM drives nCONFIG high to initiate bitstream configuration using the configuration scheme you specified at power-on.

#### **Related Information**

Booting and Configuration in the Intel Stratix 10 Hard Processor System Technical Reference Manual

# 2.3. Additional Clock Requirements for HPS, PCIe, eSRAM, and HBM2

The Intel Stratix 10 device has additional clock requirements for PCIe, HPS EMIF, eSRAM, and the High Bandwidth Memory (HBM2) IP.

To avoid configuration failures, the Intel Stratix 10 device requires additional clocks for the PCIe, HPS EMIF, eSRAM, the HBM2 IP, and all E-tile variants. You must provide a free-running, stable reference clock to these blocks before configuration begins. This reference clock is in addition to the configuration clock requirements for an internal or external oscillator described in OSC\_CLK\_1 Requirements on page 38. These blocks and their specific clock names are as listed below.

HBM2: pll\_ref\_clk and ext\_core\_clk

eSRAM: CLK\_ESRAM\_[0,1]p and CLK\_ESRAM\_[0,1]n

HPS EMIF: pll\_ref\_clk

• L- and H-tile PCIe channels: REFCLK GXB

E-tile: REFCLK\_GXE

Note:

The transceiver power supplies must be a nominal levels for successful configuration. You can use the  $V_{CC}$  and  $V_{CCP}$  power supplies for limited transceiver channel testing. Designs that include many transceivers require an auxiliary power supply to operate reliably.

# 2.4. Intel Stratix 10 Configuration Pins

The Intel Stratix 10 device uses SDM\_IO pins for device configuration. Control of SDM I/O pins passes from internal FPGA circuitry, to the Boot ROM, and finally to the value your application logic specifies.

- 1. After power-on, SDM I/O pins 0, 8, and 16 have weak pull-downs. All other SDM I/O pins have weak pull-ups. (These initial voltage levels ensure correct operation during initialization. For example, for Avalon-ST configuration SDM\_IO8 is the Avalon-ST ready signal which should not be asserted until the device reaches the FPGA Configuration state.)

- 2. The Boot ROM samples MSEL to determine the configuration scheme you specified and drives pins required for that configuration scheme. SDM I/O pins not required for the your configuration scheme remain weakly pulled up.

- 3. In approximately 10 ms the SDM I/O pins take on the state that your design specifies.

- 4. After device cleaning, the SDM reads pin information from firmware and restores the pin states that your design specifies. If you reconfigure the device, the SDM uses the updated pin information when initializing the device.

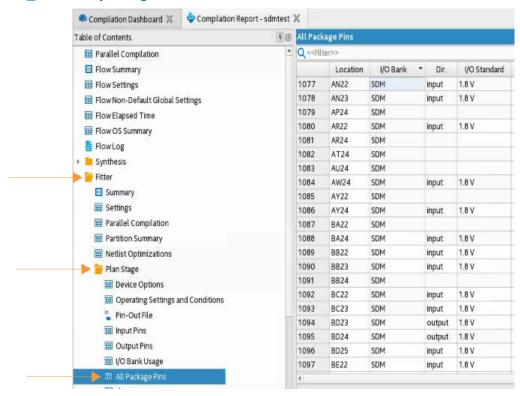

# 2.4.1. SDM Pin Mapping

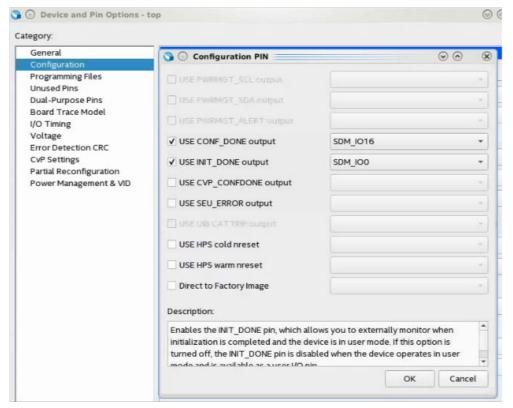

You can use SDM I/O pins for configuration and other functions such as power management and SEU detection. You specify SDM I/O pin functions using the **Device ➤ Configuration ➤ Device and Pin Options** dialog box in the Intel Quartus Prime software. All SDM input signals include Schmitt triggers. All SDM outputs are open collector.

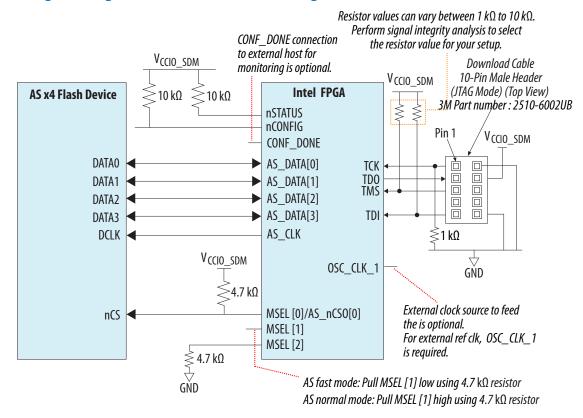

### Fixed SDM I/O Pin Assignments for Avalon-ST x8 and AS x4

The Avalon-ST x8 and AS x4 configuration schemes use the dedicated SDM I/O pin assignments listed in in the table below. Use the assignments in this table for MSEL and AVSTx8\_DATA0 to AVSTx8\_DATA8 and AS x4.

Table 3. SDM Pin Mapping for Avalon-ST x8 and AS x4

| SDM Pins | MSEL Function | Configuration Source Function |          |  |  |

|----------|---------------|-------------------------------|----------|--|--|

|          |               | Avalon-ST x8                  | AS x4    |  |  |

| SDM_IO0  | _             | _                             | _        |  |  |

| SDM_IO1  | _             | AVSTx8_DATA2                  | AS_DATA1 |  |  |

| SDM_IO2  | _             | AVSTx8_DATA0                  | AS_CLK   |  |  |

| SDM_IO3  | _             | AVSTx8_DATA3                  | AS_DATA2 |  |  |

| SDM_IO4  | _             | AVSTx8_DATA1                  | AS_DATA0 |  |  |

| SDM_IO5  | MSEL0         | _                             | AS_nCSO  |  |  |

| SDM_IO6  | _             | AVSTx8_DATA4                  | AS_DATA3 |  |  |

| SDM_IO7  | MSEL1         | _                             | AS_nCS2  |  |  |

|          | continued     |                               |          |  |  |

| SDM Pins | MSEL Function | Configuration Source Function |         |

|----------|---------------|-------------------------------|---------|

|          |               | Avalon-ST x8                  | AS x4   |

| SDM_IO8  | _             | AVST_READY                    | AS_nCS3 |

| SDM_IO9  | MSEL2         | _                             | AS_nCS1 |

| SDM_IO10 | _             | AVSTx8_DATA7                  | _       |

| SDM_IO11 | _             | AVSTx8_VALID                  | _       |

| SDM_IO12 | _             | _                             | _       |

| SDM_IO13 | _             | AVSTx8_DATA5 —                |         |

| SDM_IO14 | _             | AVSTx8_CLK —                  |         |

| SDM_IO15 | _             | AVSTx8_DATA6 —                |         |

| SDM_IO16 | _             |                               |         |

### **Related Information**

- Intel Stratix 10 Device Pinouts

- Intel Stratix 10 Device Family Pin Connection Guidelines

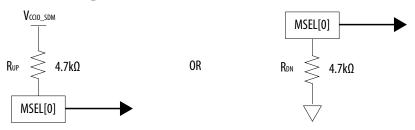

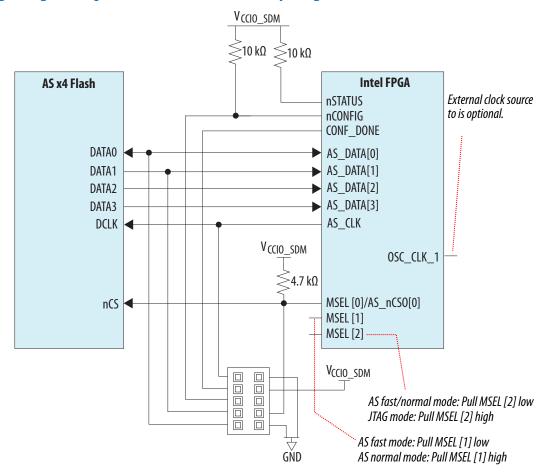

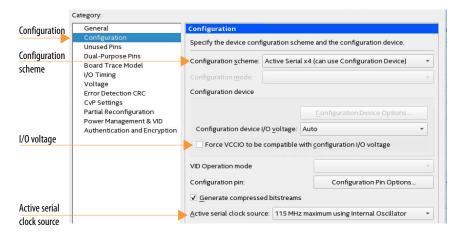

# 2.4.2. MSEL Settings

After power-on MSEL[2:0] pins specify the configuration scheme for Intel Stratix 10 devices. Use 4.7-k $\Omega$  resistors to pull the MSEL[2:0] pins up to  $V_{\texttt{CCIO\_SDM}}$  or down to ground as required by the MSEL[2:0] setting for your configuration scheme.

Figure 6. MSEL Pull-Up and Pull-Down Circuit Diagram

### Table 4. MSEL Settings for Each Configuration Scheme of Intel Stratix 10 Devices

| Configuration Scheme                    | MSEL[2:0] |

|-----------------------------------------|-----------|

| Avalon-ST (x32)                         | 000       |

| Avalon-ST (x16)                         | 101       |

| Avalon-ST (x8)                          | 110       |

| AS (Fast mode – for CvP) <sup>(2)</sup> | 001       |

| AS (Normal mode)                        | 011       |

| SD/MMC x4/x8                            | 100       |

| JTAG only <sup>(3)</sup>                | 111       |

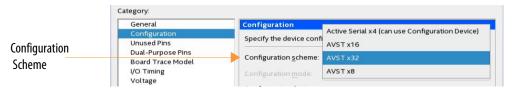

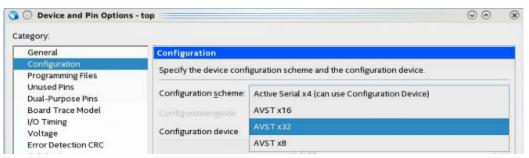

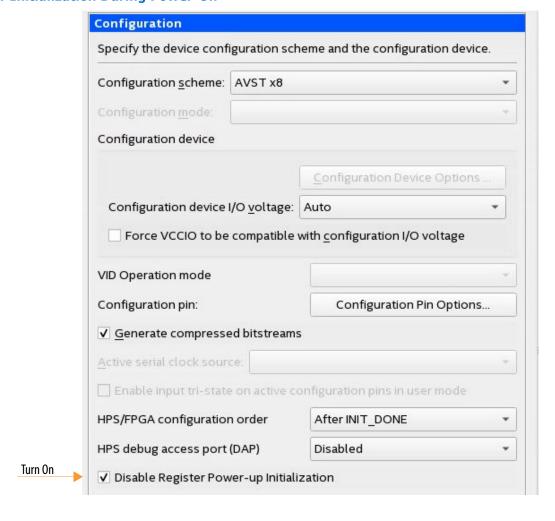

You must also specify the configuration scheme on the **Configuration** page of the **Device and Pin Options** dialog box in the Intel Quartus Prime Software.

Figure 7. Specify Configuration Scheme to Specify MSEL Value

# 2.4.3. Device Configuration Pins for Optional Configuration Signals

All configuration schemes use the same dedicated pins for the standard control signals shown in the *Intel Stratix 10 Configuration Timing Diagram*. Many other optional configuration signals do not have dedicated pin assignments.

# **Device Configuration Pins without Fixed Assignments**

<sup>(2)</sup> If you use AS Fast mode and are not concerned about 100 ms PCIe linkup, you must still ramp the  $V_{\text{CCIO\_SDM}}$  supply within 18 ms. This ramp-up requirement ensures that the AS x4 device is within its operating voltage range when the Intel Stratix 10 device begins to access it.

<sup>(3)</sup> JTAG configuration works with any valid MSEL settings, unless disabled for security.

Note:

Although the CONF\_DONE and INIT\_DONE configuration signals are not required, Intel recommends that you use these signals as an indicator to ensure that configuration is successful. The SDM drives the CONF\_DONE signal high after successfully receiving full bitstream. The SDM drives the INIT\_DONE signal high to indicate the device is fully in user mode. These signals are important when debugging configuration.

Table 5. Available SDM I/O Pin Assignments for Configuration Signals that Do Not Use Dedicated SDM I/O Pins

| Configuration Scheme                       |                                                                                                                                                  |                                                                                                                                                |                                                                        |

|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|

| Signal Names Avalon-ST                     | Avalon-ST                                                                                                                                        |                                                                                                                                                | AS x4                                                                  |

| x8                                         | x16                                                                                                                                              | x32                                                                                                                                            |                                                                        |

| SDM_IO0                                    | SDM_IO0<br>SDM_IO14                                                                                                                              | SDM_IO0<br>SDM_IO14                                                                                                                            | SDM_IO0<br>SDM_IO14                                                    |

| SDM_IO12<br>SDM_IO16                       | SDM_IO11<br>SDM_IO12<br>SDM_IO16                                                                                                                 | SDM_IO11<br>SDM_IO12<br>SDM_IO16                                                                                                               | SDM_IO11<br>SDM_IO12<br>SDM_IO16                                       |

| SDM_IO0<br>SDM_IO9<br>SDM_IO12             | SDM_IO0<br>SDM_IO9<br>SDM_IO12                                                                                                                   | SDM_IO0<br>SDM_IO12                                                                                                                            | SDM_IO0<br>SDM_IO12                                                    |

| SDM_IO0<br>SDM_IO5<br>SDM_IO12<br>SDM_IO16 | SDM_IO0 SDM_IO1 SDM_IO2 SDM_IO3 SDM_IO4 SDM_IO5 SDM_IO6 SDM_IO7 SDM_IO10 SDM_IO11 SDM_IO11 SDM_IO12 SDM_IO13 SDM_IO14 SDM_IO15 SDM_IO15 SDM_IO15 | SDM_IO0 SDM_IO1 SDM_IO1 SDM_IO2 SDM_IO3 SDM_IO4 SDM_IO5 SDM_IO6 SDM_IO7 SDM_IO9 SDM_IO10 SDM_IO11 SDM_IO11 SDM_IO12 SDM_IO13 SDM_IO14 SDM_IO15 | SDM_IO0 SDM_IO10 SDM_IO11 SDM_IO12 SDM_IO13 SDM_IO14 SDM_IO15 SDM_IO16 |

|                                            | SDM_IO0  SDM_IO12 SDM_IO16  SDM_IO0 SDM_IO9 SDM_IO12  SDM_IO0 SDM_IO5 SDM_IO5 SDM_IO12                                                           | X8   X16                                                                                                                                       | X8   X16   X32                                                         |

**Configuration Scheme Signal Names Avalon-ST** AS x4 **x8 x16 x32** INIT\_DONE SDM\_IO0 SDM\_IO0 SDM\_IO0 SDM\_IO0 SDM\_IO5 SDM\_IO1 SDM\_IO10 SDM\_IO1 SDM\_IO12 SDM\_IO2 SDM\_IO2 SDM\_IO11 SDM\_IO16 SDM\_IO3 SDM\_IO3 SDM\_IO12 SDM\_IO4 SDM\_IO4 SDM\_IO13 SDM\_IO5 SDM\_IO5 SDM\_IO14 SDM\_IO6 SDM\_IO6 SDM\_IO15 SDM\_IO7 SDM\_IO7 SDM\_IO16 SDM\_IO9 SDM\_IO9 SDM\_IO10 SDM\_IO10 SDM\_IO11 SDM\_IO11 SDM\_IO12 SDM\_IO12 SDM\_IO13 SDM\_IO13 SDM\_IO14 SDM\_IO14 SDM\_IO15 SDM\_IO15 SDM\_IO16 SDM\_IO16 Not supported Not supported CVP\_CONFDONE Not supported SDM\_IO0 SDM\_IO10 SDM\_IO11 SDM\_IO12 SDM\_IO13 SDM\_IO14 SDM\_IO15 SDM\_IO16 SEU\_ERROR SDM\_IO0 SDM\_IO0 SDM\_IO0 SDM\_IO0 SDM\_IO5 SDM\_IO1 SDM\_IO1 SDM\_IO10 SDM\_IO2 SDM\_IO2 SDM\_IO7 SDM\_IO11 SDM\_IO9 SDM\_IO3 SDM\_IO3 SDM\_IO12 SDM\_IO12 SDM\_IO4 SDM\_IO4 SDM\_IO13 SDM\_IO16 SDM\_IO5 SDM\_IO5 SDM\_IO14 SDM\_IO6 SDM\_IO6 SDM\_IO15 continued...

### 2. Intel Stratix 10 Configuration Details

#### UG-S10CONFIG | 2020.03.06

|                         | Configuration Scheme |                |                |          |

|-------------------------|----------------------|----------------|----------------|----------|

| Signal Names            | Avalon-ST            |                |                | AS x4    |

|                         | х8                   | x16            | x32            |          |

|                         |                      | SDM_IO7        | SDM_IO7        | SDM_IO16 |

|                         |                      | SDM_IO9        | SDM_IO9        |          |

|                         |                      | SDM_IO10       | SDM_IO10       |          |

|                         |                      | SDM_IO11       | SDM_IO11       |          |

|                         |                      | SDM_IO12       | SDM_IO12       |          |

|                         |                      | SDM_IO13       | SDM_IO13       |          |

|                         |                      | SDM_IO14       | SDM_IO14       |          |

|                         |                      | SDM_IO15       | SDM_IO15       |          |

|                         |                      | SDM_IO16       | SDM_IO16       |          |

| HPS_COLD_nRESET         | SDM_IO0              | SDM_IO0        | SDM_IO0        | SDM_IO0  |

|                         | SDM_IO5              | SDM_IO1        | SDM_IO1        | SDM_IO10 |

|                         | SDM_IO7              | SDM_IO2        | SDM_IO2        | SDM_IO11 |

|                         | SDM_IO9              | SDM_IO3        | SDM_IO3        | SDM_IO12 |

|                         | SDM_IO12             | SDM_IO4        | SDM_IO4        | SDM_IO13 |

|                         | SDM_IO16             | SDM_IO5        | SDM_IO5        | SDM_IO14 |

|                         |                      | SDM_IO6        | SDM_I06        | SDM_IO15 |

|                         |                      | SDM_IO7        | SDM_IO7        | SDM_IO16 |

|                         |                      | SDM_IO9        | SDM_I09        |          |

|                         |                      | SDM_IO10       | SDM_IO10       |          |

|                         |                      | SDM_IO11       | SDM_IO11       |          |

|                         |                      | SDM_IO12       | SDM_IO12       |          |

|                         |                      | SDM_IO13       | SDM_IO13       |          |

|                         |                      | SDM_IO14       | SDM_IO14       |          |

|                         |                      | SDM_IO15       | SDM_IO15       |          |

|                         |                      | SDM_IO16       | SDM_IO16       |          |

| Direct to Factory Image | Not applicable       | Not applicable | Not applicable | SDM_IO0  |

|                         |                      |                |                | SDM_IO10 |

|                         |                      |                |                | SDM_IO11 |

|                         |                      |                |                | SDM_IO12 |

|                         |                      |                |                | SDM_IO13 |

|                         |                      |                |                | SDM_IO14 |

|                         | continued            |                |                |          |

| Signal Names | Configuration Scheme |          |          |                      |  |

|--------------|----------------------|----------|----------|----------------------|--|

|              | Avalon-ST            |          |          | AS x4                |  |

|              | x8                   | x16      | x32      |                      |  |

|              |                      |          |          | SDM_IO15<br>SDM_IO16 |  |

| DATA UNLOCK  | SDM_IO0              | SDM_IO0  | SDM_IO0  | SDM_IO0              |  |

|              | SDM_IO5              | SDM_IO1  | SDM_IO1  | SDM_IO10             |  |

|              | SDM_IO7              | SDM_IO2  | SDM_IO2  | SDM_IO11             |  |

|              | SDM_IO9              | SDM_IO3  | SDM_IO3  | SDM_IO12             |  |

|              | SDM_I012             | SDM_IO4  | SDM_IO4  | SDM_IO13             |  |

|              | SDM_IO16             | SDM_IO5  | SDM_IO5  | SDM_IO14             |  |

|              |                      | SDM_IO6  | SDM_IO6  | SDM_IO15             |  |

|              |                      | SDM_IO7  | SDM_IO7  | SDM_IO16             |  |

|              |                      | SDM_IO9  | SDM_IO9  |                      |  |

|              |                      | SDM_IO10 | SDM_I010 |                      |  |

|              |                      | SDM_IO11 | SDM_I011 |                      |  |

|              |                      | SDM_IO12 | SDM_I012 |                      |  |

|              |                      | SDM_IO13 | SDM_IO13 |                      |  |

|              |                      | SDM_IO14 | SDM_IO14 |                      |  |

|              |                      | SDM_IO15 | SDM_IO15 |                      |  |

|              |                      | SDM_IO16 | SDM_IO16 |                      |  |

Note:

Intel recommends that you assign the CONF\_DONE and INIT\_DONE pins to SDM I/O pins 0 or 16. These pins have weak internal pull-downs resistors. If you cannot use these pins, Intel recommends that you include external 4.7-k $\Omega$  pull-down resistors to avoid false signaling.

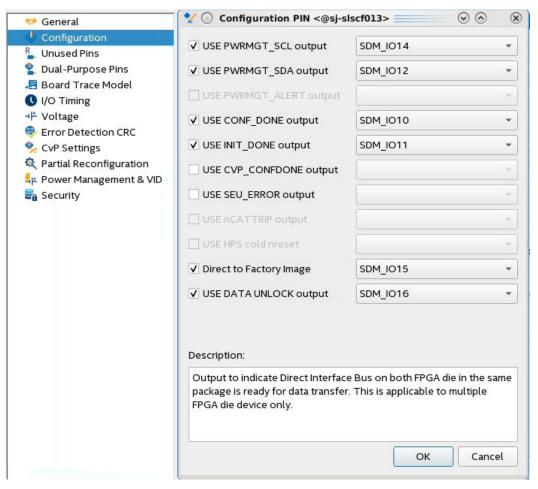

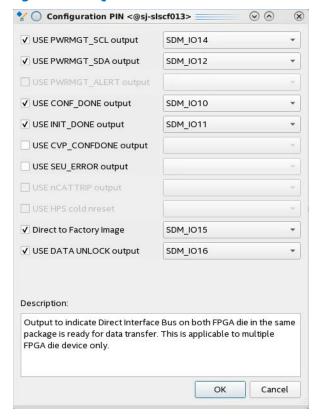

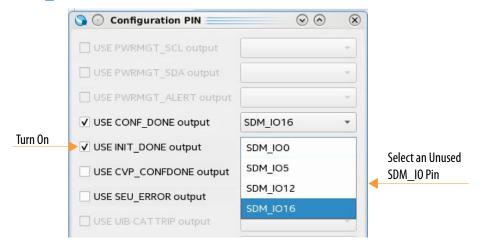

# 2.4.3.1. Specifying Optional Configuration Pins

You enable and assign the SDM I/O pins using the Intel Quartus Prime software.

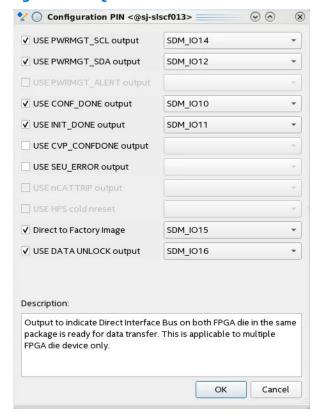

Complete the following steps to assign these additional configuration pins:

- 1. On the **Assignments** menu, click **Device**.

- 2. In the **Device and Pin Options** dialog box, select the **Configuration** category and click **Configuration Pins Options**.

- 3. In the **Configuration Pin** window, enable and assign the configuration pin that you want to include in your design.

4. Click **OK** to confirm and close the **Configuration Pin** dialog box.

# 2.4.3.2. Enabling Dual-Purpose Pins

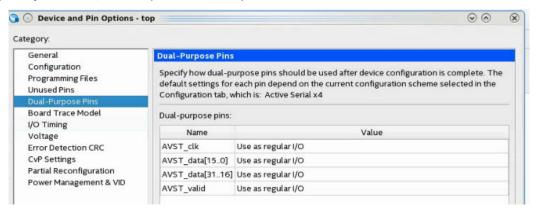

AVST\_CLK, AVST\_DATA[15:0], AVST\_DATA[31:16], and AVST\_VALID are dual-purpose pins. Once the device enters user mode these pins can function either as GPIOs or as tri-state inputs.

If you use these pins as GPIOs, make the following assignments:

- Set V<sub>CCIO</sub> of the I/O bank at 1.8 V

- Assign the 1.8 V I/O standard to these pins

Complete the following steps to assign these settings to the dual-purpose pins:

- 1. On the **Assignments** menu, click **Device**.

- 2. In the **Device and Pin Options** dialog box, select the **Dual-Purpose Pins** category.

- 3. In the **Dual-purpose pins** table, set the pin functionality in the **Value** column.

4. Click **OK** to confirm and close the **Device and Pin Options**

**Attention:** When you use the Avalon ST configuration scheme the dual-purpose Avalon ST pins have the following restrictions:

- You cannot use the Avalon-ST interface for partial reconfiguration (PR).

- You cannot use the Avalon-ST pins in user mode in designs that include the HPS. This restriction means that you

cannot use the Avalon-ST as dual-purpose I/Os in designs that include the HPS.

# 2.4.3.3. Configuration Pins I/O Standard, Drive Strength, and IBIS Model

### Table 6. Intel Stratix 10 Configuration Pins I/O Standard, Drive Strength, and IBIS Model

| Configuration Pin Function               | Direction | I/O Standard                         | Drive Strength (mA) | IBIS Model                                    |

|------------------------------------------|-----------|--------------------------------------|---------------------|-----------------------------------------------|

| TDO                                      | Output    | 1.8V LVCMOS                          | 8                   | 18_io_d8s1_sdm_lv                             |

| TMS                                      | Input     | Schmitt Trigger Input                | _                   | 18_in_sdm_lv                                  |

| TCK                                      | Input     | Schmitt Trigger Input                | _                   | 18_in_sdm_lv                                  |

| TDI                                      | Input     | Schmitt Trigger Input                | _                   | 18_in_sdm_lv                                  |

| nSTATUS                                  | Output    | 1.8V LVCMOS                          | 8                   | 18_io_d8s1_sdm_lv                             |

| OSC_CLK_1                                | Input     | Schmitt Trigger Input                | _                   | 18_in_sdm_lv                                  |

| nCONFIG                                  | Input     | Schmitt Trigger Input                | _                   | 18_in_sdm_lv                                  |

| SDM_IO[16:0]                             | I/O       | Schmitt Trigger Input or 1.8V LVCMOS | 8                   | Input: 18_in_sdm_lv Output: 18_io_d8s1_sdm_lv |

| AVST_DATA[31:0], AVST_CLK,<br>AVST_VALID | I/O       | Schmitt Trigger Input or 1.8V LVCMOS | 8                   | Input: 18_in_sdm_lv Output: 18_io_d8s1_sdm_lv |

You can download the IBIS models from the *IBIS Models for Intel Devices* web page. The Intel Quartus Prime software does not support IBIS model generation for configuration pins in the current release.

#### **Unused SDM Pins**

You can specify other functions on unused SDM pins in the Intel Quartus Prime software.

#### **Related Information**

IBIS Models for Intel Devices

# 2.4.3.4. SDM I/O Pins for Power Management and SmartVID

SDM pins are also available for the SmartVID power management feature for -V devices.

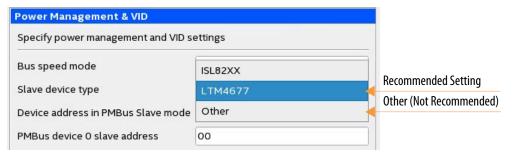

Intel recommends that you use the Analog Devices LTM4677 Dual 18A or Single 36A µModule Regulator with Digital Power System Management to regulate the PMBus. The LTM4677 device is the default setting for the **Device** ➤ **Device and Pin Options** ➤ **Power Management & VID** ➤ **Slave device type** parameter. If you are using a different PMBus regular change the default setting from **LTM4677** to **Other**.

## Figure 8. Specifying the Slave Device Type for Power Management and VID

Refer to the *Intel Stratix 10 Power Management User Guide* for more information about the pin assignments and PMBus setting.

#### **Related Information**

Intel Stratix 10 Power Management User Guide

# 2.4.3.5. Specifying Pins for Partial Reconfiguration (PR)

The partial reconfiguration signals use GPIO pins.

The following signals control partial reconfiguration in Intel Stratix 10 devices:

- PR\_REQUEST

- PR READY

- PR ERROR

- PR DONE

Connect these partial reconfiguration signals to the Partial Reconfiguration External Configuration Controller Intel FPGA IP.

#### **Related Information**

Creating a Partial Reconfiguration Design

# 2.5. Configuration Clocks

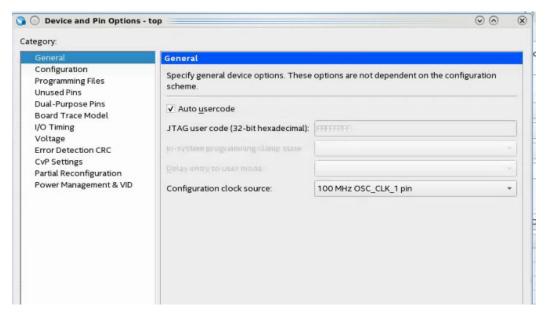

# 2.5.1. Setting Configuration Clock Source

You must specify the configuration clock source by selecting either the internal oscillator or OSC\_CLK\_1 with the supported frequency. By default, the SDM uses the internal oscillator for device configuration. Specify an OSC\_CLK\_1 clock source for the fastest configuration time.

Complete the following steps to select the configuration clock source:

- 1. To specify OSC\_CLK\_1 as the clock source, on the **Assignments** menu, click **Device**.

- 2. In the **Device and Pin Options** dialog box, select the **General** category.

- 3. Specify the configuration clock source from the **Configuration clock source** drop down menu.

4. Click **OK** to confirm and close the **Device and Pin Options**.

#### **Related Information**

OSC\_CLK\_1 Clock Input on page 38

# 2.5.2. OSC\_CLK\_1 Clock Input

## OSC\_CLK\_1 Requirements

When you drive the OSC\_CLK\_1 input clock with an external clock source and enable OSC\_CLK\_1 in the Intel Quartus Prime software, the device loads the majority of the configuration bitstream at 250 MHz. Intel Stratix 10 devices include an internal oscillator in addition to OSC\_CLK\_1 which runs the configuration process at a frequency between 170-230 MHz. Intel Stratix 10 devices always use this internal oscillator to load the first section of the bitstream, approximately 200 kilobyte (KB). The SDM can use either clock source for the remainder of device configuration. If you use the internal oscillator, you can leave the OSC\_CLK\_1 unconnected.

UG-S10CONFIG | 2020.03.06

Note:

Device configuration may fail under the following conditions when you select the OSC\_CLK\_1 as the clock source for configuration:

- You fail to drive the OSC CLK 1 pin.

- You drive the OSC\_CLK\_1 pin at an incorrect frequency. Select one of the following input reference clock frequencies to

drive the OSC\_CLK\_1 pin:

- 25 MHz

- 100 MHz

- 125 MHz

The Intel Stratix 10 device multiplies the OSC\_CLK\_1 source clock frequency to generate a 250 MHz clock for configuration. Using an OSC\_CLK\_1 source enables the fastest possible configuration. Refer to Setting Configuration Clock Source for instructions setting this frequency using the Intel Quartus Prime Software.

You can also specify this frequency by editing your .gsf file. Here are the possible assignments:

```

# EXTERNAL OSCILLATOR CLOCK VIA OSC_CLK_1 PIN

set_global_assignment -name DEVICE_INITIALIZATION_CLOCK OSC_CLK_1_25MHZ

set_global_assignment -name DEVICE_INITIALIZATION_CLOCK OSC_CLK_1_100MHZ

set_global_assignment -name DEVICE_INITIALIZATION_CLOCK OSC_CLK_1_125MHZ

```

## Configuration Clock Requirements for Reconfiguration Without Power Cycling the Device

When you specify OSC\_CLK\_1 for configuration and reconfigure without powering down the Intel Stratix 10 device, the device can only reconfigure with OSC\_CLK\_1. In this scenario, OSC\_CLK\_1 must be a free-running clock.

# Configuration Clock Requirements for Configuration After Powering Cycling the Device

After a power-down, when you specify OSC\_CLK\_1 for configuration, the Intel Stratix 10 device uses the internal oscillator to load the first section of the bitstream and OSC\_CLK\_1 for the remainder.

#### **Related Information**

- Intel Stratix 10 L- and H-Tile Transceiver PHY User Guide

- Intel Stratix 10 E-Tile Transceiver PHY User Guide

- Intel Stratix 10 External Memory Interfaces IP User Guide

- Setting Configuration Clock Source on page 37

# 3. Intel Stratix 10 Configuration Schemes

# 3.1. Avalon-ST Configuration

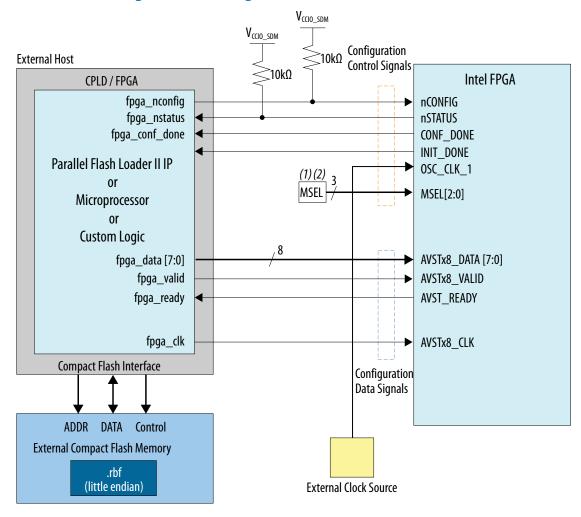

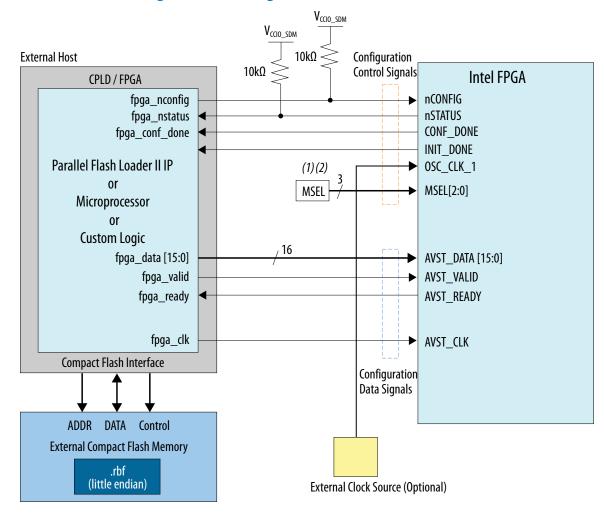

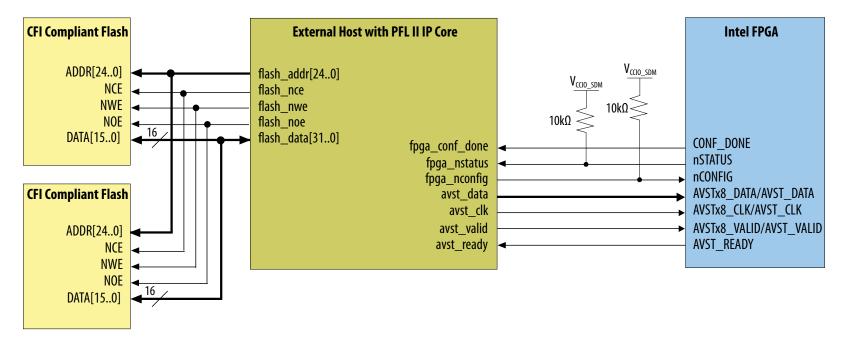

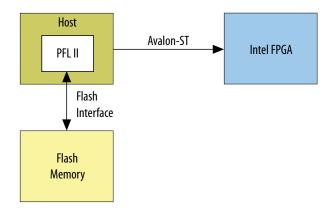

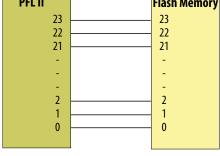

The Avalon-ST configuration scheme replaces the FPP mode available in earlier device families. Avalon-ST is the fastest configuration scheme for Intel Stratix 10 devices. This scheme uses an external host, such as a microprocessor, MAX<sup>®</sup> II, MAX V, or Intel MAX 10 device to drive configuration. The external host controls the transfer of configuration data from external storage such as flash memory to the FPGA. The logic that controls the configuration process resides in the external host. You can use the PFL II IP with a MAX II, MAX V, or Intel MAX 10 device as the host to read configuration data from the flash memory device and configure the Intel Stratix 10 device. The Avalon-ST configuration scheme is called passive because the external host, not the Intel Stratix 10 device, controls configuration.

## Table 7. Avalon-ST Configuration Data Width, Clock Rates, and Data Rates

Mb is an abbreviation for Megabits per second.

| Protocol  | Data Width (bits) | Max Clock Rate | Max Data Rate | MSEL[2:0] |

|-----------|-------------------|----------------|---------------|-----------|

|           | 32                | 125 MHz        | 4000 Mb       | 000       |

| Avalon-ST | 16                | 125 MHz        | 2000 Mb       | 101       |

|           | 8                 | 125 MHz        | 1000 Mb       | 110       |

# Table 8. Required Configuration Signals for the Avalon-ST Configuration Scheme

You can use an 8-, 16-, or 32-bit Avalon-ST configuration data bus. You specify SDM I/O pin functions using the **Device ➤ Configuration ➤ Device and Pin Options** dialog box in the Intel Quartus Prime software. For the Avalon-ST x16 and x32 configuration, you can reassign the GPIO, dual-purpose configuration pins for other functions in user mode using the **Device ➤ Configuration ➤ Device and Pin Options ➤ Dual-Purpose Pins** dialog box.

| Signal Name | Pin Type | Direction | Powered by            |

|-------------|----------|-----------|-----------------------|

| nSTATUS     | SDM I/O  | Output    | V <sub>CCIO_SDM</sub> |

| nCONFIG     | SDM I/O  | Input     | V <sub>CCIO_SDM</sub> |

|             |          |           | continued             |

Intel Corporation. All rights reserved. Agilex, Altera, Arria, Cyclone, Enpirion, Intel, the Intel logo, MAX, Nios, Quartus and Stratix words and logos are trademarks of Intel Corporation or its subsidiaries in the U.S. and/or other countries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

ISO 9001:2015 Registered

<sup>\*</sup>Other names and brands may be claimed as the property of others.

| Signal Name              | Pin Type              | Direction | Powered by            |

|--------------------------|-----------------------|-----------|-----------------------|

| MSEL[2:0]                | SDM I/O, Dual-Purpose | Input     | V <sub>CCIO_SDM</sub> |

| CONF_DONE <sup>(4)</sup> | SDM I/O               | Output    | V <sub>CCIO_SDM</sub> |

| AVST_READY               | SDM I/O               | Output    | V <sub>CCIO_SDM</sub> |

| AVSTx8_DATA[7:0]         | SDM I/O               | Input     | V <sub>CCIO_SDM</sub> |

| AVSTx8_VALID             | SDM I/O               | Input     | V <sub>CCIO_SDM</sub> |

| AVSTx8_CLK               | SDM I/O               | Input     | V <sub>CCIO_SDM</sub> |

| AVST_DATA[31:0]          | GPIO, Dual-Purpose    | Input     | V <sub>CCIO</sub>     |

| AVST_VALID               | GPIO, Dual-Purpose    | Input     | V <sub>CCIO</sub>     |

| AVST_CLK                 | GPIO, Dual-Purpose    | Input     | V <sub>CCIO</sub>     |

Refer to the *Intel Stratix 10 Data Sheet* for configuration timing estimates.

Note:

Although the INIT\_DONE configuration signal is not required for configuration, Intel recommends that you use this signals. The SDM drives the INIT\_DONE signal high to indicate the device is fully in user mode. This signal is important when debugging configuration.

Note:

If you create custom logic instead of using the PFL II IP to drive configuration, refer to the *Avalon Streaming Interfaces* in the *Avalon Interface Specifications* for protocol details.

#### **Related Information**

- Device Configuration Pins for Optional Configuration Signals on page 28

- SDM Pin Mapping on page 26

- Avalon Interface Specifications

- Intel Stratix 10 Device Data Sheet

- Intel Stratix 10 Device Features

For a list of device features that are planned for future releases.

<sup>(4)</sup> CONF\_DONE is required if you are using the Intel FPGA Parallel Flash Loader II IP as the configuration host.

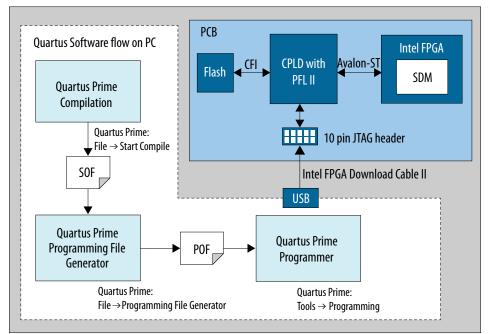

# 3.1.1. Avalon-ST Configuration Scheme Hardware Components and File Types

You can use the following components to implement the Avalon-ST configuration scheme:

- A CPLD with PFL II IP and common flash interface (CFI) flash or Quad SPI flash memory

- A custom host, typically a microprocessor, with any external memory

- The Intel FPGA Download Cable II to connect the Intel Quartus Prime Programmer to the PCB.

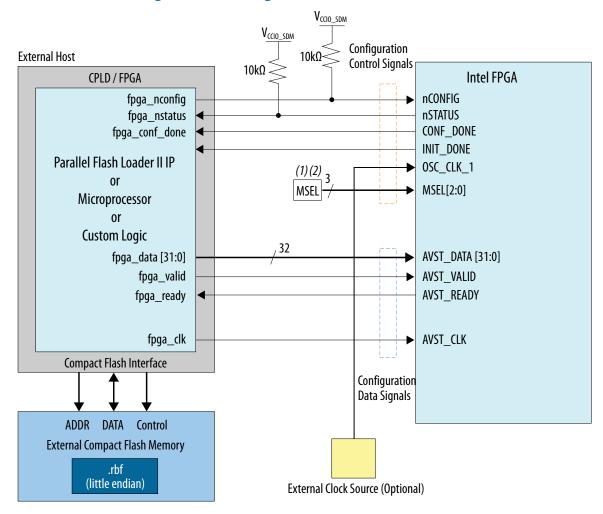

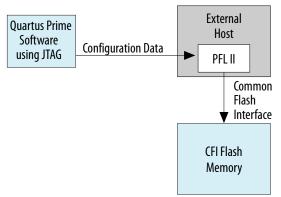

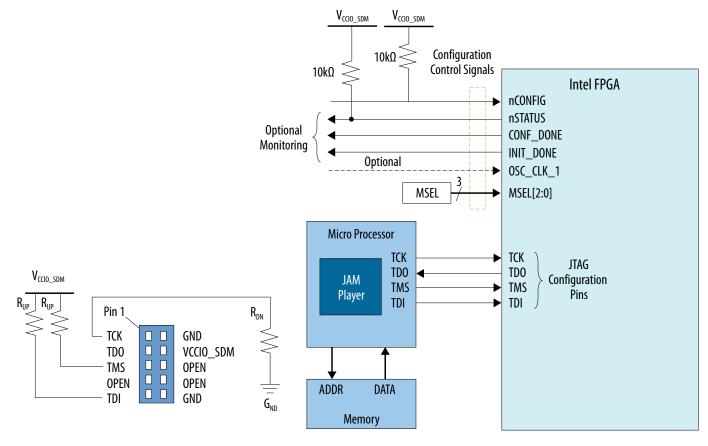

The following block diagram illustrates the components and design flow using the Avalon-ST configuration scheme.

Figure 9. Components and Design Flow for .pof Programming

**Table 9.** Output File Types

| Programming File Type  | Extension | Description                                                                                                                                                                                                                              |

|------------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Programmer Object File | .pof      | The .pof is a proprietary Intel FPGA file type. Use the PFL II IP core via a JTAG header to write the .pof to an external CFI flash or serial flash device.                                                                              |

| Raw Binary File        | .rbf      | You can also use the .rbf with the Avalon-ST configuration scheme and an external host such as a CPU or microcontroller.                                                                                                                 |

|                        |           | You can program the configuration bitstreams or data in the <code>.rbf</code> file directly into flash via a third-party programmer. Then, you can use an external host to configure the device with the Avalon-ST configuration scheme. |

If you choose a third-party microprocessor for Avalon-ST configuration, refer to the *Avalon Streaming Interfaces* in the *Avalon Interface Specifications* for protocol details.

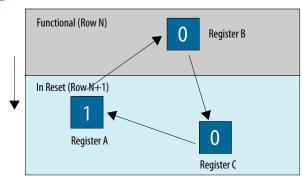

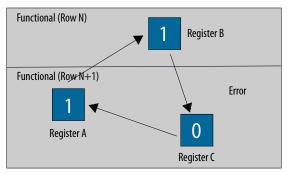

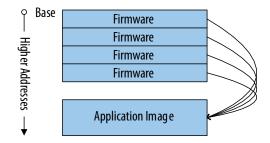

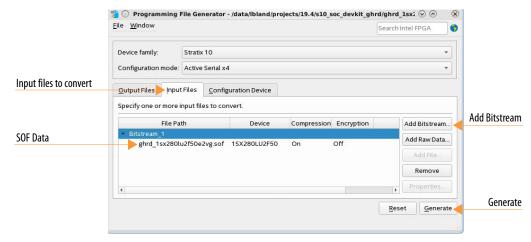

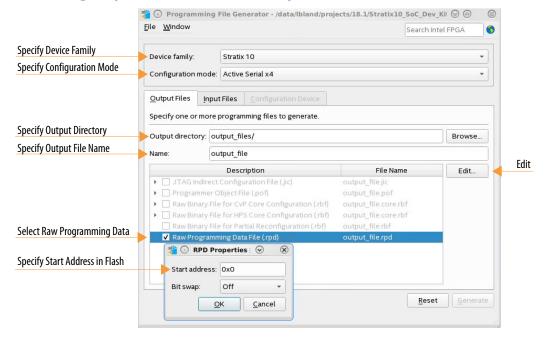

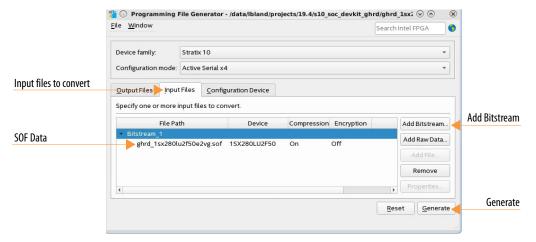

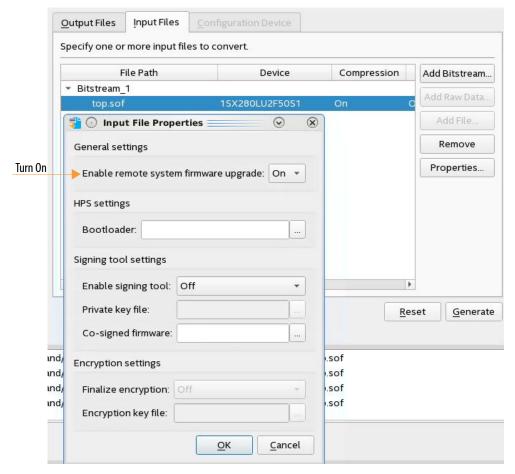

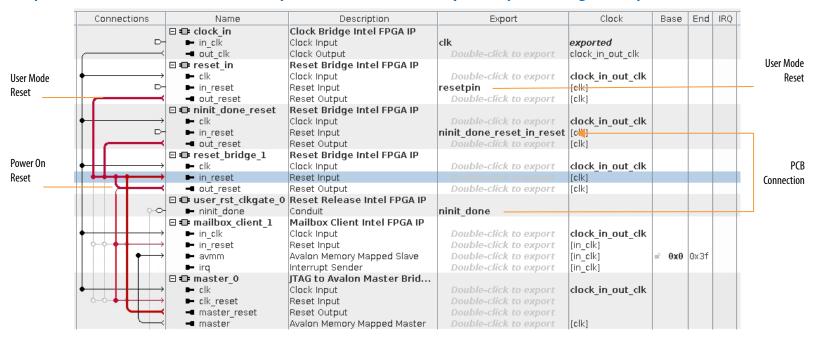

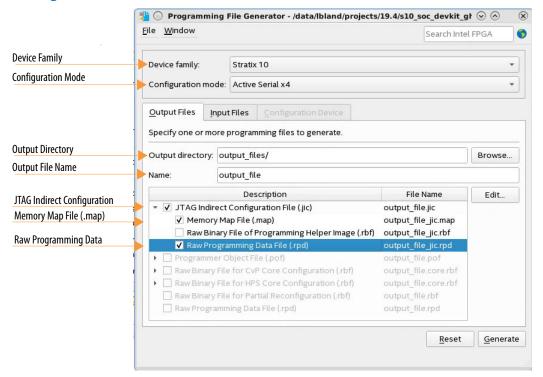

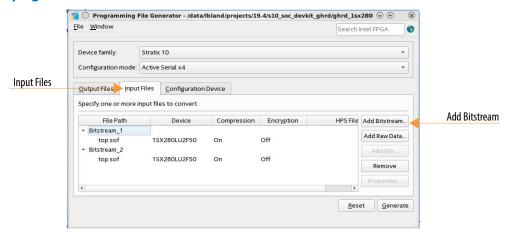

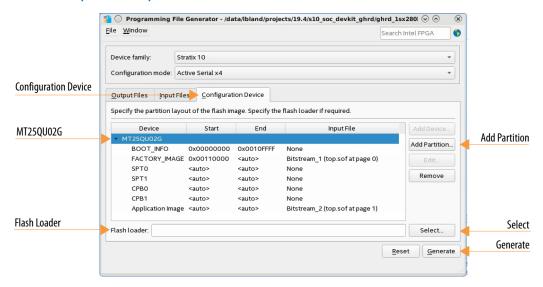

# 3.1.2. Enabling Avalon-ST Device Configuration