# Accelerator Functional Unit Developer's Guide for Intel<sup>®</sup> FPGA Programmable Acceleration Card

Updated for Intel<sup>®</sup> Acceleration Stack for Intel<sup>®</sup> Xeon<sup>®</sup> CPU with FPGAs: **1.2 and 2.0.1**

## **Contents**

| 1. About this Document                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.1. Intended Audience.31.2. Conventions.31.3. Acronym List for Accelerator Functional Unit Developer's Guide.31.4. Acceleration Glossary.51.5. Related Documentation.5                                                                                                                                                                                                                                                                                                         |

| 2. Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 2.1. Getting Started with AFU Development                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 3. Getting Started with Platform Configuration8                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 4. The Accelerator Functional Unit (AFU)                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 5. Developing AFUs with the OPAE SDK 12                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| <ul> <li>5.1. Overview of the OPAE SDK</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 6. AFU In-System Debug                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 6.1. Remote Signal Tap Setup and Use.       35         6.1.1. Instrumenting the AFU Design for Signal Tap.       35         6.1.2. Enable Remote Debug and Signal Tap.       36         6.1.3. Generate the Remote Debug Enabled AF.       36         6.1.4. Prepare the Remote Debug Host.       36         6.1.5. Running a Remote Debug Session.       37         6.1.6. Remote Debug Guidelines.       39         6.1.7. Troubleshooting Remote Debug Connections.       40 |

| 7. Accelerator Functional Unit Developer's Guide for Intel FPGA Programmable<br>Acceleration Card Archives                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 8. Document Revision History for Accelerator Functional Unit Developer's Guide for<br>Intel FPGA Programmable Acceleration Card                                                                                                                                                                                                                                                                                                                                                 |

## **1. About this Document**

This document serves as a hardware developers guide for developing Accelerator Functional Units (AFUs) for the Intel Acceleration Stack for Intel Xeon<sup>®</sup> CPU with FPGAs product, hereafter referred to as the Acceleration Stack.

## **1.1. Intended Audience**

The intended audience consists of FPGA RTL designers developing AFUs for the Acceleration Stack on the Intel FPGA Programmable Acceleration Card (Intel FPGA PAC) and the hardware platforms (referred to as Intel FPGA PAC throughout this document).

## **1.2.** Conventions

#### Table 1.Document Conventions

| Convention                      | Description                                                                                                                                                                                                                         |

|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| #                               | Precedes a command that indicates the command is to be entered as root.                                                                                                                                                             |

| \$                              | Indicates a command is to be entered as a user.                                                                                                                                                                                     |

| This font                       | Filenames, commands, and keywords are printed in this<br>font. Long command lines are printed in this font. Although<br>long command lines may wrap to the next line, the return is<br>not part of the command; do not press enter. |

| <variable_name></variable_name> | Indicates the placeholder text that appears between the angle brackets must be replaced with an appropriate value. Do not enter the angle brackets.                                                                                 |

## **1.3. Acronym List for Accelerator Functional Unit Developer's Guide**

#### Table 2. Acronyms

| Acronyms | Expansion                   | Description                                                                                                                                                                                       |

|----------|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AFU      | Accelerator Functional Unit | Hardware Accelerator implemented in<br>FPGA logic which offloads a<br>computational operation for an<br>application from the CPU to improve<br>performance.                                       |

| AF       | Accelerator Function        | Compiled Hardware Accelerator image<br>implemented in FPGA logic that<br>accelerates an application. An AFU and<br>associated AFs may also be referred to<br>as GBS (Green-Bits, Green BitStream) |

|          |                             | continued                                                                                                                                                                                         |

Intel Corporation. All rights reserved. Agilex, Altera, Arria, Cyclone, Enpirion, Intel, the Intel logo, MAX, Nios, Quartus and Stratix words and logos are trademarks of Intel Corporation or its subsidiaries in the U.S. and/or other countries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services. \*Other names and brands may be claimed as the property of others.

| Acronyms | Expansion                                | Description                                                                                                                                                                                                                                                                                                                                                         |

|----------|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          |                                          | in the Acceleration Stack installation directory tree and in source code comments.                                                                                                                                                                                                                                                                                  |

| API      | Application Programming Interface        | A set of subroutine definitions,<br>protocols, and tools for building<br>software applications.                                                                                                                                                                                                                                                                     |

| ASE      | AFU Simulation Environment               | Co-simulation environment that allows<br>you to use the same host application<br>and AF in a simulation environment.<br>ASE is part of the Intel Acceleration<br>Stack for FPGAs.                                                                                                                                                                                   |

| CCI-P    | Core Cache Interface                     | CCI-P is the standard interface AFUs use to communicate with the host.                                                                                                                                                                                                                                                                                              |

| FIU      | FPGA Interface Unit                      | FIU is a platform interface layer that<br>acts as a bridge between platform<br>interfaces like PCIe*, UPI and AFU-side<br>interfaces such as CCI-P.                                                                                                                                                                                                                 |

| FIM      | FPGA Interface Manager                   | The FPGA hardware containing the<br>FPGA Interface Unit (FIU) and external<br>interfaces for memory, networking,<br>etc.<br>The FIM may also be referred to as<br>BBS (Blue-Bits, Blue BitStream) in the<br>Acceleration Stack installation directory<br>tree and in source code comments.<br>The Accelerator Function (AF)<br>interfaces with the FIM at run time. |

| NLB      | Native Loopback                          | The NLB performs reads and writes to the CCI-P link to test connectivity and throughput.                                                                                                                                                                                                                                                                            |

| OPAE     | Open Programmable Acceleration<br>Engine | The OPAE is a software framework for managing and accessing AFs.                                                                                                                                                                                                                                                                                                    |

| PR       | Partial Reconfiguration                  | The ability to dynamically reconfigure a portion of an FPGA while the remaining FPGA design continues to function.                                                                                                                                                                                                                                                  |

| ТСР      | Transmission Control Protocol            | TCP is a standard Internet protocol<br>that defines how to establish and<br>maintain a network conversation<br>through which application programs<br>can exchange data.                                                                                                                                                                                             |

| PIM      | Platform Interface Manager               | An abstraction layer for managing top-<br>level device ports and system-provided<br>clock crossing.                                                                                                                                                                                                                                                                 |

| HSSI     | High Speed Serial Interface              | Reference to the multi-gigabit serial transceiver I/O in the FIM and the corresponding interface to the AFU.                                                                                                                                                                                                                                                        |

## **1.4. Acceleration Glossary**

### Table 3. Acceleration Stack for Intel Xeon CPU with FPGAs Glossary

| Term                                                          | Abbreviation       | Description                                                                                                                                                   |

|---------------------------------------------------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Intel Acceleration Stack for Intel Xeon<br>CPU with FPGAs     | Acceleration Stack | A collection of software, firmware and<br>tools that provides performance-<br>optimized connectivity between an<br>Intel FPGA and an Intel Xeon<br>processor. |

| Intel FPGA Programmable Acceleration<br>Card (Intel FPGA PAC) | Intel FPGA PAC     | PCIe FPGA accelerator card.<br>Contains an FPGA Interface Manager<br>(FIM) that pairs with an Intel Xeon<br>processor over the PCIe bus.                      |

## **1.5. Related Documentation**

#### Table 4.Item Description

| Item                                                                                                                                   | Description                                                                                                                                                                                            |

|----------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Intel Acceleration Stack Quick Start Guide for<br>Intel Programmable Acceleration Card with Intel<br>Arria 10 GX FPGA                  | This document describes the Acceleration Stack and provides instructions for hardware and software installation and setup required for development with the stack.                                     |

| Intel Acceleration Stack Quick Start Guide for<br>Intel FPGA Programmable Acceleration Card<br>D5005                                   | This document describes the Acceleration Stack and provides<br>instructions for hardware and software installation and setup required<br>for development with the stack.                               |

| Acceleration Stack for Intel Xeon CPU with<br>FPGAs Core Cache Interface (CCI-P) Reference<br>Manual                                   | This document describes the CCI-P protocol and requirements placed on AFUs.                                                                                                                            |

| Networking Interface for Open Programmable<br>Acceleration Engine: Intel Programmable<br>Acceleration Card with Intel Arria 10 GX FPGA | This document describes the HSSI device interface offered by the Intel PAC with Intel Arria 10 GX FPGA hardware platform and the OPAE tools and driver features that support the network port feature. |

| Networking Interface for Open Programmable<br>Acceleration Engine: Intel FPGA Programmable<br>Acceleration Card D5005                  | This document describes the HSSI device interface offered by the Intel FPGA PAC D5005 platform and the OPAE tools and driver features that support the network port feature.                           |

| Intel Accelerator Functional Unit (AFU)<br>Simulation Environment (ASE) User Guide                                                     | This document provides instructions on how to use the Intel Accelerator Functional Unit (AFU) Simulation Environment (ASE).                                                                            |

| Open Programmable Acceleration Engine (OPAE)<br>Tools Guide                                                                            | This user guide documents the utilities provided in the Open<br>Programmable Acceleration Engine (OPAE) software component of the<br>Acceleration Stack.                                               |

#### Send Feedback

## **2. Introduction**

## 2.1. Getting Started with AFU Development

Depending on which Intel FPGA PAC you are using, please refer to one of the following Quick Start Guides:

- If you are using Intel PAC with Intel Arria<sup>®</sup> 10 GX FPGA, refer to the *Intel* Acceleration Stack Quick Start Guide for Intel Programmable Acceleration Card with Intel Arria 10 GX FPGA.

- If you are using Intel FPGA PAC D5005, refer to the *Intel Acceleration Stack Quick Start Guide for Intel FPGA Programmable Acceleration Card D5005*.

The *Quick Start Guide* provides an overview of the Acceleration Stack and provides instruction for installation and setup of hardware and software components of the stack, including the OPAE SDK used to develop AFUs and generate loadable AF images. It is essential to familiarize yourself with the concepts developed for the Acceleration Stack and to complete the installation and setup procedures covered in the *Quick Start Guide*.

This guide for AFU development builds on the concepts and environment setup established in the *Quick Start Guide*.

#### **Related Information**

- Intel Acceleration Stack Quick Start Guide for Intel Programmable Acceleration Card with Intel Arria 10 GX FPGA

- Intel Acceleration Stack Quick Start Guide for Intel FPGA Programmable Acceleration Card D5005

#### 2.1.1. Development Environment References

The OPAE\_PLATFORM\_ROOT environment variable points to the OPAE SDK installation as detailed in the *Quick Start Guide*.

### 2.1.2. FPGA Tools and IP Requirements

You need to download the Intel Acceleration Stack for Development to generate the Accelerator Functions (AFs).

The Intel Acceleration Stack for Development installer includes licenses for the following software and IPs required for the generation of the AFs:

Intel Corporation. All rights reserved. Agilex, Altera, Arria, Cyclone, Enpirion, Intel, the Intel logo, MAX, Nios, Quartus and Stratix words and logos are trademarks of Intel Corporation or its subsidiaries in the U.S. and/or other countries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services. \*Other names and brands may be claimed as the property of others.

ISO 9001:2015 Registered

Intel Quartus<sup>®</sup> Prime Pro Edition software

*Note:* For information on compatible version of the software for each platform, refer to the platform specific *Release Notes*.

- Intel FPGA PCI Express SR-IOV Block IP license

- Network IP license

You do not need to purchase the license separately for these IPs.

For requirements when using the ASE for AFU functional verification, refer to the *Intel Accelerator Functional Unit (AFU) Simulation Environment (ASE) User Guide*.

#### **Related Information**

- Intel Accelerator Functional Unit (AFU) Simulation Environment (ASE) User Guide

- Intel Acceleration Stack for Intel Xeon CPU with FPGAs Version 1.2 Release Notes

- Intel Acceleration Stack for Intel Xeon CPU with FPGAs Version 2.0 Release Notes: For the Intel FPGA Programmable Acceleration Card D5005

- Installing the Intel Acceleration Stack Development Package on the Host Machine

### 2.2. Base Knowledge and Skills Prerequisites

The Acceleration Stack is a framework and toolset to leverage FPGA technology Most of the platform-level complexity has been abstracted away for the AFU developer by the FPGA Interface Manager (FIM) in the FPGA static region. This guide assumes the following FPGA logic design-related knowledge and skills:

Familiarity with PR compilation flows, including the Intel Quartus Prime Pro Edition PR flow, concepts of physical and logical partitioning in the FPGA, module boundary best practices, and resource restrictions.

The hardware compilation flow automates management of the partial reconfiguration region.

- Knowledge and skills in static timing closure, including familiarity and skill with the Timing Analyzer tool in Intel Quartus Prime Pro Edition, applying timing constraints, Synopsys\* Design Constraints (.sdc) language and Tcl scripting, and design methods to close timing on critical paths.

- Knowledge and skills with industry standard RTL simulation tools supported by the Acceleration Stack. For more information, refer to the *Intel Accelerator Functional Unit (AFU) Simulation Environment (ASE) User Guide*.

#### **Related Information**

Intel Accelerator Functional Unit (AFU) Simulation Environment (ASE) User Guide

## **3. Getting Started with Platform Configuration**

This chapter guides you through the process to generate an AF for the hello\_afu sample AFU provided in the Acceleration Stack installation. Successful completion of the steps in this chapter quickly verifies your AFU development environment using a known-good design.

Build the  $hello_afu$  sample AFU by invoking the run.sh script from a terminal window as shown in Example 1.

Ensure that you declare the <code>\$OPAE\_PLATFORM\_ROOT</code> variable before you compile the sample AFU. If it is not declared, you can source <code>init\_env.sh</code> located in the Acceleration Stack directory. For more details, refer to the *Intel Acceleration Stack Quick Start Guide*.

*Note:* This step takes about 30 minutes to complete.

#### Example 1. Compile hello\_afu Sample AFU

```

cd $OPAE_PLATFORM_ROOT/hw/samples/hello_afu

afu_synth_setup --source hw/rtl/filelist.txt build_synth

cd build_synth

run.sh

```

When the shell script completes, it indicates successful generation of the AF:

\$OPAE\_PLATFORM\_ROOT/hw/samples/hello\_afu/build\_synth/hello\_afu.gbs

You can optionally use the helper script clean.sh, to remove the following build output from the Intel Quartus Prime PR compilation invoked by run.sh:

- ./build/\*.qdb

- ./build/qdb

- ./build/output\_files/

- ./build/\*qarlog

- ./build/\*.qdf

#### Example 2. Clean up from the PR Compilation (Optional)

cd \$0PAE\_PLATFORM\_ROOT/hw/samples/hello\_afu/build\_synth

clean.sh

Successfully compiling the hello\_afu sample AFU verifies that your environment is setup and ready to begin developing your own custom AFUs.

Intel Corporation. All rights reserved. Agilex, Altera, Arria, Cyclone, Enpirion, Intel, the Intel logo, MAX, Nios, Quartus and Stratix words and logos are trademarks of Intel Corporation or its subsidiaries in the U.S. and/or other countries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services. \*Other names and brands may be claimed as the property of others.

## 4. The Accelerator Functional Unit (AFU)

The AFU is a function or set of functions that can be accelerated on an OPAE hardware platform. The AFU is described in RTL and then compiled with the OPAE SDK to generate an Accelerated Function (AF) image for the target hardware platform. An AF is a compiled hardware accelerator image implemented in FPGA logic that accelerates an application. The AF image is used by OPAE to load the AFU to the PR region.

An AFU has two main communication paths between the host:

- FPGA to host transactions: The FPGA accesses host memory (256 terabyte address space) using a 512 bit data path. This data path has separate channels for read and write traffic allowing for simultaneous read and write to occur. The read and write channels support bursts of 1, 2, and 4 cache lines.

- Host to FPGA (MMIO) transactions: The host can access a 256 KB address space within the FPGA. This address space contains Device Feature Header (DFHs) and the control and status registers of the AFU hardware. DFHs are small ROMs that hold metadata about the hardware that are enumerated by the OPAE SDK.

The AFU can access host memory on a cache line basis (64 bytes) through the CCI-P interface. OPAE defines up to 256 KB of memory mapped I/O (MMIO) space for AFUs that the host can access using the OPAE driver and APIs. At the bottom of the MMIO space, the AFU must implement the following OPAE requirements:

- AFU DFH a 64-bit header at MMIO address offset 0x0

- AFU ID a 128-bit UUID at MMIO address offset 0x2 (CCI-P D-word address)

The following sections of the *CCI-P Reference Manual* document the CCI-P protocol and all OPAE requirements for an AFU design, including the DFH and AFU ID format:

- CCI-P Interface

- AFU Requirements

- Device Feature List

#### **Related Information**

Acceleration Stack for Intel Xeon CPU with FPGAs Core Cache Interface (CCI-P) Reference Manual

## 4.1. AFU Design Components

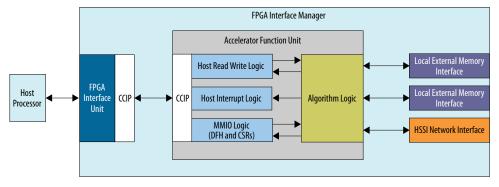

#### Figure 1. **AFU High Level Block Diagram**

A typical AFU design includes the following components:

- RTL description of the algorithm or function being accelerated

- RTL description to implement the base requirements placed on AFUs by OPAE • (e.g., DFH, AFU ID in MMIO space). See the CCI-P Reference Manual for more details on the RTL description.

- Supportive infrastructure ٠

- Logic to map AFU CSRs into MMIO space

- Memory mastering logic

- FPGA to host memory access •

- Local FPGA memory access

- Debug and Performance monitoring

- Signal Tap with the Remote Debug feature

- Performance monitoring and counters within the scope of the AFU

The interfaces provided by OPAE for host and local memory access are basic, slave access interfaces. The host only has access to the AFU's 256KB MMIO space. The AFU must implement a DMA to move large workload data to and from host memory. The dma afu sample AFU in the OPAE platform installation provides an example for moving data between the host and local memory.

The FIM supports notification for illegal accesses made on the CCI-P interface and performance monitoring capabilities accessible by the host through the FME in the FIU. Any error handling and performance monitoring must be implemented in the AFU by developer.

The FIM provides for AFU remote debug through the FME connected to an OPAE tool that hosts the debug connection over TCP. The AFU designer must instrument the AFU with debug instances and nodes using tools such as Signal Tap. The nlb mode 0 stp sample AFU in the OPAE platform installation provides an example for enabling an AFU for remote debug with Signal Tap over a TCP connection.

4. The Accelerator Functional Unit (AFU) UG-20169 | 2020.03.02

## 4.2. Basic Building Blocks

Intel FPGA Basic Building Blocks (BBBs) are reference designs of common functions that can be used in AFU designs to implement supportive infrastructure such as CCI-P memory access property transformations and DMA. These references are provided asis. They are not validated by Intel. The available BBBs, including documentation, are maintained at the GitHub site.

#### **Related Information**

Basic Building Blocks (BBB) for OPAE-managed Intel FPGAs

## **5. Developing AFUs with the OPAE SDK**

## **5.1. Overview of the OPAE SDK**

The OPAE SDK is a development environment that supports synthesizing AFs targeted for a specific OPAE-compliant hardware platform from an OPAE-compliant AFU.

The OPAE SDK consists of two hardware development components:

- The database, tools, scripts and ancillary files required to target AF generation for a specific hardware platform.

- The OPAE version supported by the hardware platform used to configure a build environment for AFU simulation and compilation on the target hardware platform.

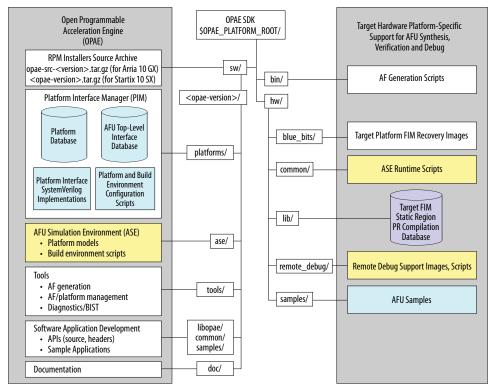

#### Figure 2. Overview of the OPAE SDK

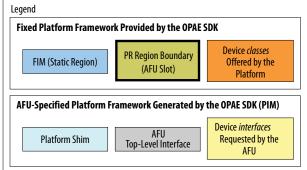

OPAE's Platform Interface Manager (PIM) defines a non-hardware specific OPAE Platform that provides generic classes of device interfaces. The OPAE platform is an abstraction of a hardware platform for which AFUs are designed. This level of abstraction enables generating AFs from AFUs designed for the generic OPAE Platform for any OPAE-compliant hardware platform that offers the device interfaces required

Intel Corporation. All rights reserved. Agilex, Altera, Arria, Cyclone, Enpirion, Intel, the Intel logo, MAX, Nios, Quartus and Stratix words and logos are trademarks of Intel Corporation or its subsidiaries in the U.S. and/or other countries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

by the AFU. The PIM generates a platform shim based upon device interfaces and properties requested by the AFU. The platform shim is inserted between the hardware platform's PR region boundary and the AFU and provides the top-level module interface for the AFU.

See the Overview of the OPAE Platform for AFUs on page 13 for more details on the OPAE.

See the OPAE SDK Design Flow for AFU Development on page 17 for the process used by AFUs to request top-level interfaces and configure simulation and synthesis build environments.

### 5.2. Overview of the OPAE Platform for AFUs

The PIM defines a generic OPAE Platform for which AFU top-levels should be designed to ensure provisioning on multiple hardware platforms.

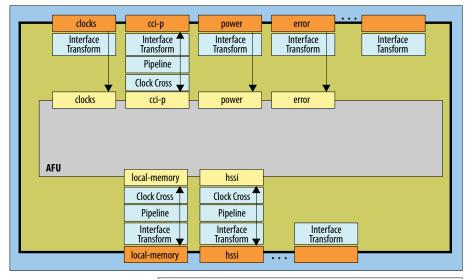

The figure below shows how the platform shim generated by the PIM enables AFU integration on a specific target hardware platform.

#### Figure 3. OPAE Platform Block Diagram

AFUs are designed to use generic top-level interfaces to a set of generic device classes such as a host device (cci-p), local memory, network port I/O, clocks, and power and error management. The AFU requests the device interfaces and properties it needs from the PIM using a platform configuration file specification.

### 5.2.1. Platform Device Classes

The OPAE Platform provides for AFU integration into the stack through several device classes. Each device class offers one or more port interfaces, each of which have properties of their own. AFUs request a specific device interface and properties from the PIM. The PIM implements the requested interfaces and properties in a platform shim that translates hardware platform-specific device interfaces to the OPAE Platform's generic device interfaces used by the AFU.

The Intel FPGA PAC offers the following device classes:

- The clocks Device Class on page 14

- The cci-p Device Class on page 14

- The power Device Class on page 15

- The error Device Class on page 15

- The hssi Device Class on page 15

- The local-memory Device Class on page 16

#### 5.2.1.1. The clocks Device Class

The Intel FPGA PAC platform offers the clocks device class with the pClk3\_usr2 interface, which consists of a list of port signals documented in the CCI-P Reference Manual.

#### 5.2.1.2. The cci-p Device Class

The Intel FPGA PAC platform offers the cci-p device class with the struct interface. The structures defined in the following package in the OPAE SDK:

```

$OPAE_PLATFORM_ROOT/sw/<opae-version>/platforms/platform_if/rtl/device_if/

ccip_if_pkg.sv

```

To use the structures defined in ccip\_if\_pkg.sv include platform\_if.vh in your AFU source files. For example, `include "platform\_if.vh".

The CCI-P interface is used by the AFU to access host memory and to respond to MMIO requests from the host. It is composed of three command/response channels:

- Channel 0 It is used by the AFU for host memory read requests and responses. Channel 0's response port is also used for receiving MMIO read and write requests from the host.

- Channel 1 It is used by the AFU for host memory write requests and responses. • It is also used for issuing write fences and interrupts.

- Channel 2 It is used by the AFU for MMIO read responses back to the host.

The CCI-P interface and protocol are documented in the CCI-P Reference Manual.

#### **Related Information**

Acceleration Stack for Intel Xeon CPU with FPGAs Core Cache Interface (CCI-P) Reference Manual

#### 5.2.1.3. The power Device Class

The Intel FPGA PAC platform offers the power device class with a 2-bit interface. This interface drives the signal that represents the power state requests documented in the *Additional Control Signals* section of the *CCI-P Reference Manual*.

#### **Related Information**

Additional Control Signals

#### **5.2.1.4. The error Device Class**

The Intel FPGA PAC platform offers the error device class with a 1-bit interface. This interface drives the signal that represents the CCI-P protocol error documented in the *Additional Control Signals* section of the *CCI-P Reference Manual*.

#### **Related Information**

Additional Control Signals

#### 5.2.1.5. The hssi Device Class

The Intel FPGA PAC platform offers the hssi device class with the raw\_pr interface, which consists of a SystemVerilog interface defined in the following Verilog header in the OPAE SDK:

\$OPAE\_PLATFORM\_ROOT/hw/lib/build/platform/pr\_hssi\_if.vh

The HSSI interface is used by the AFU to access the network port on the Intel FPGA PAC platforms. It is composed of the Native PHY Transceiver interface with a generic parallel interface to support multiple configurations by the HSSI PHY in the FIM.

The HSSI interface is an optional interface that AFUs can request from the Intel FPGA PAC platform. The Intel FPGA PAC platforms with HSSI interface contain sample AFUs in the directories starting with eth\_e2e\_e<data\_rate> or hssi\_prbs

#### **Related Information**

- Intel Arria 10 Transceiver PHY User Guide

- Intel Stratix 10 L- and H-Tile Transceiver PHY User Guide

- Intel Stratix 10 E-Tile Transceiver PHY User Guide

- Networking Interface for Open Programmable Acceleration Engine: Intel Programmable Acceleration Card with Intel Arria 10 GX FPGA

- 10 Gbps Ethernet Accelerator Functional Unit (AFU) Design Example User Guide: Intel Programmable Acceleration Card with Intel Arria 10 GX FPGA

- 40 Gbps Ethernet Accelerator Functional Unit (AFU) Design Example User Guide: Intel Programmable Acceleration Card with Intel Arria 10 GX FPGA

- Networking Interface for Open Programmable Acceleration Engine User Guide: Intel FPGA Programmable Acceleration Card D5005

#### 5.2.1.6. The local-memory Device Class

The Intel FPGA PAC platform offers the local-memory device class with the following choice of interfaces:

• avalon\_mm - a SystemVerilog interface defined in the following header file in the OPAE SDK:

\$OPAE\_PLATFORM\_ROOT/sw/<opae-version>/platforms/

platform\_if/rtl/device\_if/avalon\_mem\_if.vh

- **avalon\_mm\_legacy\_wires\_2bank** a fixed port list of signal wires specific to the Intel FPGA PAC platform. This interface is for legacy support of AFUs developed with earlier versions of the OPAE SDK. For portability to future platforms, consider porting existing AFUs designed with the legacy interface to the avalon\_mm interface.

- *Note:* The new AFU design uses the avalon\_mm interface. Intel recommends to use avalon\_mm interface for your new AFU designs and avoid using legacy interface.

The AFU accesses local memory on the Intel FPGA PAC through the Avalon<sup>®</sup> Memory-Mapped (Avalon-MM) slave interfaces provided by the FIM. The Intel FPGA PAC platforms typically provide one or more bank of local memory. For detailed information on bank of local memory, refer to the *FIM Data Sheet*. Each bank interface is synchronous to its own clock source provided by the interface.

The local memory interface is an optional interface that AFUs can request from the Intel FPGA PAC platform. See the following two sample AFUs for examples of using the local memory interface:

- \$OPAE\_PLATFORM\_ROOT/hw/samples/hello\_mem\_afu

- \$OPAE\_PLATFORM\_ROOT/hw/samples/dma\_afu

Intel recommends using avalom\_mm interface for all the new designs and not use the legacy interface.

### 5.2.2. The Platform Interface Manager (PIM)

The PIM contains a collection of shims. The PIM abstracts the details of the target hardware platform from the AFU to support AFU portability to multiple platforms without modifying the AFU. The PIM performs the following functions based upon the AFU's platform configuration described in its .json file:

- Validates that an OPAE device interface requested by the AFU is provided by the target platform.

- Properly terminates any OPAE device class offered by the platform but not requested by the AFU.

- Enables an AFU to optionally request an OPAE device interface from the target platform and adjust the build-out of its implementation based on whether the requested interface is available. For example, the AFU can optionally request local memory and build-out to use it if available from the target platform, otherwise it builds-out to function without local memory. See the nlb\_mode\_0 sample AFU for an example.

- Provides register pipeline stages on requested OPAE device interfaces to aid static timing closure during AF generation.

- Provides asynchronous clock crossing from an OPAE device interface's native clock to a target clock requested by the AFU. For example, the AFU can request that all requested OPAE device interfaces be retimed to the uClk\_usr clock source provided by the clocks interface. See the hello\_mem\_afu sample AFU for an example.

#### 5.2.2.1. Interface Transforms

The PIM transforms a device class offered by the platform into the specific device interface requested by the AFU. Any device classes on the platform not requested by the AFU are properly terminated to support AF generation. The transformation is typically a simple, direct connection between the platform and AFU consisting of device interface ports or structures or a bundling of the ports into an interface vector. For example, the PIM directly connects the platform's cci-p interface structures and clocks, power , and error ports to the AFU. In the case of local-memory, the PIM abstracts the hardware platform details from the AFU by packing the platform's interface into a SystemVerilog interface vector.

#### 5.2.2.2. Pipelining

The PIM inserts register pipeline stages on device interfaces as requested by the AFU.

#### 5.2.2.3. Clock Crossing

The PIM inserts asynchronous clock crossing on device interfaces to cross from the interface's native clock to a clock specified by the AFU. For example, the AFU can request that all device interfaces be synchronized to  $uClk\_usr$  from the clocks interface.

### 5.3. OPAE SDK Design Flow for AFU Development

#### 5.3.1. Overview of the Design Flow

This section provides a summary overview of the OPAE SDK design flow for AFU development. Refer to the Design Flow Details on page 21 for a detailed description of each step included in the flow.

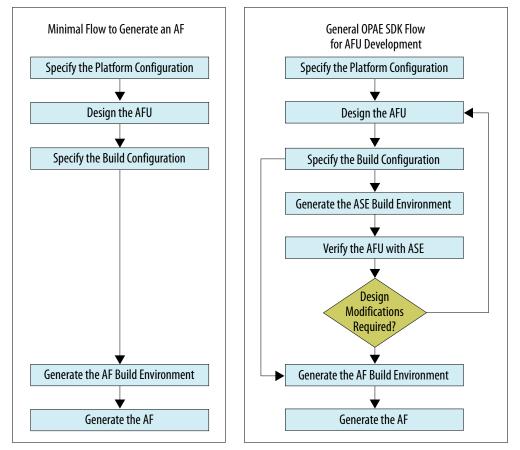

The figure below shows the design flow when using the OPAE SDK to verify and synthesize AFs for a target hardware platform.

The minimal flow depicted in the figure shows the minimum flow steps to generate an AF from an AFU design, while the depiction of the general flow shows where AFU verification with ASE fits in the overall flow.

- Specify the Platform Configuration for the AFU in a platform configuration file

json) by requesting a top-level AFU interface along with any required interface

properties. The top-level interface requested by the AFU defines its SystemVerilog

top-level module port definition.

- *Design the AFU* within this top-level module port definition.

- With the AFU design file set established, *Specify the Build Configuration* for both AFU simulation and AF synthesis with a single build configuration file (filelist.txt), which lists the AFU's design source (e.g., RTL, IP, Platform Designer subsystems, constraints) along with any required macro definitions and include files.

- Using the PIM, *Generate the AF/ASE Build Environment* based upon the AFU's platform and build configuration file specifications and the target hardware platform. At this point in the flow, you can use ASE to run OPAE software applications on a simulation target instantiated from the AFU's RTL source and the hardware platform model provided by OPAE.

- Finally, Generate the AF using the AF generation scripts provided by the SDK.

#### 5.3.1.1. Minimal Flow Example

The following example shows the minimal flow necessary to generate an AF. It uses the hello\_afu sample AFU included in the OPAE SDK. The hello\_afu sample can be used as template for AFU designs that require only a host device interface and no local memory or network port I/O.

The following is a synopsis of the minimal set of OPAE SDK commands required to generate an AF from the hello\_afu sample AFU:

cd \$OPAE\_PLATFORM\_ROOT/hw/samples/hello\_afu

afu\_synth\_setup --source hw/rtl/filelist.txt build\_synth

cd build\_synth

\$OPAE PLATFORM ROOT/bin/run.sh

The execution of these commands generates an AF (.gbs) image in the <code>build\_synth</code> sub-directory. The rest of this section elaborates on the minimal flow steps.

#### 5.3.1.1.1. Specify the Platform Configuration

The hello\_afu sample specifies its platform configuration in the following .json file:

\$OPAE\_PLATFORM\_ROOT/hw/samples/hello\_afu/hw/rtl/hello\_afu.json

The platform configuration file provides an example of the following:

- The AFU requests the ccip\_std\_afu top-level interface, which includes the ccip, clocks, power and error device interfaces. If the target hardware platform offers local-memory or hssi device classes, then the platform shim generated by the PIM terminates those interfaces.

- Uses top-level interface default properties (i.e., no pipelining or clock crossing).

- Specifies the AFU's UUID

#### 5.3.1.1.2. Design the AFU

The AFU's top-level interface request in its platform configuration file defines its top-level module. The hello\_afu sample's top-level module definition is located here:

\$OPAE\_PLATFORM\_ROOT/hw/samples/hello\_afu/hw/rtl/ccip\_std\_afu.sv

The hello\_afu sample implements the minimal requirements for an AFU specified in the *CCI-P Reference Manual* in the AFU submodule instanced by the ccip\_std\_afu top-level module and is described in the following SystemVerilog source:

\$OPAE\_PLATFORM\_ROOT/hw/samples/hello\_afu/hw/rtl/afu.sv

The afu.sv source file includes the afu\_json\_info.vh Verilog header file generated by the PIM and uses the AFU\_ACCEL\_UUID macro defined by afu\_json\_info.vh to set the UUID value as required by the *CCI-P Reference Manual*.

Each of the above SystemVerilog source files includes the platform\_if.vh Verilog header file generated by the PIM, which makes available all the interface definitions used by the AFU.

#### 5.3.1.1.3. Specify the Build Configuration

The hello\_afu sample specifies its build configuration in the following text file:

\$OPAE\_PLATFORM\_ROOT/hw/samples/hello\_afu/hw/rtl/filelist.txt

It lists all source files, including its platform configuration file (.json). The file references are relative to the build configuration file's directory location.

#### 5.3.1.1.4. Generate the AF Build Environment

To generate an AF build environment, open a terminal and enter the following command sequence:

cd \$OPAE\_PLATFORM\_ROOT/hw/samples/hello\_afu

afu\_synth\_setup --source hw/rtl/filelist.txt build\_synth

The afu\_synth\_setup parses the build configuration file (filelist.txt) and generates a Intel Quartus Prime project in the specified directory (build\_synth).

#### 5.3.1.1.5. Generate the AF

To generate an AF, enter the following commands:

cd build\_synth

\$OPAE\_PLATFORM\_ROOT/bin/run.sh

Completion of shell script indicates successful generation of the AF at the following location:

\$OPAE\_PLATFORM\_ROOT/hw/samples/hello\_afu/build\_synth/hello\_afu.gbs

#### 5.3.1.2. General Flow Example

The OPAE SDK supports AFU verification with ASE which can be used at any time in the flow once you have an initial AFU design and have specified platform and build configurations. This section extends the minimal flow example by showing how to generate an ASE build environment and use ASE to run an OPAE host application against a combined RTL model of the AFU on the target hardware platform. This can be done using the hello\_afu sample AFU.

#### 5.3.1.2.1. Generate the ASE Build Environment

Open a terminal window and enter the following commands to generate the ASE build environment:

```

cd $OPAE_PLATFORM_ROOT/hw/samples/hello_afu

afu_sim_setup --source hw/rtl/filelist.txt build_sim

```

The afu\_sim\_setup parses the filelist.txt file and generates a simulation project in the build\_sim directory.

#### 5.3.1.2.2. Verify the AFU with ASE

Type the following commands to compile the AFU and platform simulation models and start the simulation server process:

cd build\_sim make make sim

After the commands complete, ASE indicates that the server is ready for simulation. Note the instructions for setting the ASE\_WORKDIR environment variable in the ASE client window.

Open a second terminal window and enter the following commands to start the ASE client process:

<Set ASE\_WORKDIR as directed by the simulator in the server window.>

cd \$OPAE\_PLATFORM\_ROOT/hw/samples/hello\_afu/sw

make clean

make USE\_ASE=1

./hello\_afu

The OPAE host application runs on the host in the ASE client window process and the ASE server window process shows the AFU model responding to host MMIO accesses, host memory accesses initiated by the AFU, and interrupt vector information signaled by the AFU.

#### **Related Information**

Intel Accelerator Functional Unit (AFU) Simulation Environment (ASE) User Guide

#### 5.3.2. Design Flow Details

This section describes each step of the OPAE SDK design flow in detail.

#### 5.3.2.1. Specify the Platform Configuration

An OPAE compliant AFU configures the OPAE Platform using a platform configuration file to specify the following to the PIM:

- Specify the AFU's UUID

- Request a top-level interface

- Extend a top-level interface with additional device interfaces

- Request pipelining on device interfaces

- Request clock crossing on device interfaces

- Specify a requested device interface as optional

- Specify AFU user clock timing

The platform configuration file uses the JSON format to specify the above tasks with key:value pairs.

#### 5.3.2.1.1. Specify the AFU's UUID

The single place to specify the AFU's UUID required by the OPAE Platform is in its platform configuration file. The PIM and OPAE runtime tools extract the AFU UUID from the platform configuration file for consumption by the AFU RTL implementation, and OPAE host applications and tools.

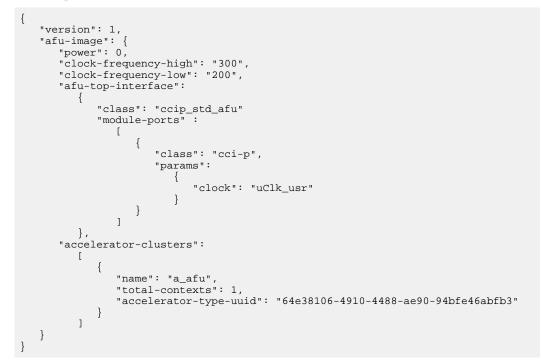

Specify the AFU UUID with the afu-image:acceleratorclusters:accelerator-type-uuid key as shown in the json file located at the following location:

\$OPAE\_PLATFORM\_ROOT/hw/samples/hello\_afu/hw/rtl/hello\_afu.json

You can generate a 128-bit UUID using different ways, for example, you can use the following command:

uuidgen

#### 5.3.2.1.2. Request a Top-level Interface

The PIM defines the following two basic top-level AFU interfaces that consist of multiple device interfaces: ccip\_std\_afu and ccip\_std\_afu\_avalon\_mm. AFUs specify their top-level interface with the afu-image:afu-top-interface:name key in the platform configuration file.

The SystemVerilog interface definitions for the device interfaces listed below are documented in the following README:

\$OPAE\_PLATFORM\_ROOT/sw/<opae-version>/platforms/afu\_top\_ifc\_db/ README.md

#### 1. ccip\_std\_afu

This top-level interface consists of the cci-p, clocks, power and error device interfaces.

The top-level AFU module name remains ccip\_std\_afu. It includes the following device interfaces (device-class:interface):

- cci-p:struct

- clocks:pClk3\_usr2

- power:2bit

- error:1bit

See the hello\_afu sample json file for an example of an AFU requesting the ccip\_std\_afu top-level AFU interface at the following location:

\$OPAE\_PLATFORM\_ROOT/hw/samples/hello\_afu/hw/rtl/hello\_afu.json

#### 2.ccip\_std\_afu\_avalon\_mm

This top-level interface consists of the device interfaces included with the ccip\_std\_afu top-level plus a local memory interface.

The top-level AFU module name remains ccip\_std\_afu. It includes the following device interfaces (device-class:interfaces):

- All device interfaces of the ccip\_std\_afu top-level AFU module interface

- local-memory:avalon\_mm

See the hello\_mem\_afu sample JSON file for an example of an AFU requesting the ccip\_std\_afu\_avalon\_mm top-level AFU interface:

\$OPAE\_PLATFORM\_ROOT/hw/samples/hello\_mem\_afu/hw/rtl/ hello\_mem\_afu.json

The PIM also defines a top-level AFU interface with a deprecated local memory device interface used by existing AFUs designed for earlier versions of the OPAE Platform. New AFU designs with local memory interfaces should be designed for the ccip\_std\_afu\_avalon\_mm top-level AFU interface.

#### 5.3.2.1.3. Extend a Top-level Interface

Additional device interfaces are accommodated by extending one of the predefined basic top-level AFU interfaces.

For example, the eth\_e2e\_e10, eth\_e2e\_e40, and hssi\_prbs sample AFUs request an hssi device interface by extending the ccip\_std\_afu top-level AFU interface using the afu-image:afu-top-interface:module-ports:[class] interface] keys:

\$OPAE\_PLATFORM\_ROOT/hw/samples/eth\_e2e\_e10/hw/rtl/ eth\_e2e\_e10.json

\$OPAE\_PLATFORM\_ROOT/hw/samples/eth\_e2e\_e40/hw/rtl/ eth\_e2e\_e40.json

\$OPAE\_PLATFORM\_ROOT/hw/samples/eth\_e2e\_e40/hw/rtl/ eth\_e2e\_e40.json

#### 5.3.2.1.4. Request Device Interface Pipelining

The AFU can request the PIM to insert pipeline stages between the target hardware platform's PR region boundary and its top-level module device interfaces on the following device classes:

- cci-p

- local-memory

Use the following key:value pair on the class key you want pipeline stages inserted:

```

afu-image:afu-top-interface:module-ports:params:add-extra-timing-reg-

stages:<integer-num>

```

For example, specify adding two pipeline stages on the local-memory device interfaces as follows:

```

'class': 'local-memory',

'params':

```

'add-extra-timing-reg-stages': 2

#### 5.3.2.1.5. Request Device Interface Clock-crossing

The AFU requests the PIM to insert a clock crossing bridge to synchronize the following device class interfaces to a clock of the AFU's choosing:

- cci-p

- local-memory

Use the following key:value pair on the device class key you want synchronized to a clock chosen by the AFU:

afu-image:afu-top-interface:module-ports:params:clock:"<clock-name>"

For example, the hello mem afu sample AFU requests that the cci-p and localmemory device interfaces be synchronized to uClk usr from the clocks interface:

\$OPAE\_PLATFORM\_ROOT/hw/samples/hello\_mem\_afu/hw/rtl/ hello mem afu.json

#### 5.3.2.1.6. Specify a Requested Device as Optional

By default, the PIM does not generate a platform shim for a target hardware platform that does not offer a device interface requested by the AFU. However, AFU's can specify a requested device interface as optional. For optionally requested device interfaces, the PIM generates a platform shim and build environments as long as the device interface is defined as optional by both the OPAE Platform and the target hardware platform. If the target hardware platform offers the device interface, the PIM transforms the interface with the properties requested by the AFU's platform configuration file, otherwise the PIM continues configuring the platform without any action on the unavailable device interface. In either case, the PIM defines a Verilog macro indicating whether the optionally requested interface is offered by the target hardware platform. AFU implementations must elaborate based on the macro definition.

Use the following key: value pair on the device class key you want to specify as optional (the default value is false):

afu-image:afu-top-interface:module-ports:optional:true

For example, the nlb mode 0 sample AFU optionally requests a local-memory interface and instantiates a memory tester module based on the related Verilog macro definition:

\$OPAE\_PLATFORM\_ROOT/hw/samples/nlb\_mode\_0/hw/rtl/nlb\_mode\_0.json

The cci-p and clocks device interfaces are mandatory for AFUs.

#### 5.3.2.1.7. Specify AFU User Clock Timing

The clocks provided to the AFU by the clocks device interface are fixed in frequency except for the following user clocks:

- uClk usr

- uClk\_usrDiv2

The AFU specifies the frequency for uClk\_usr in its platform configuration file using the following key:value pairs:

```

afu-image:clock-frequency-high:[<float-value>| "auto" | "auto-<float-value>" ]

afu-image:clock-frequency-low:[<float-value>| "auto" | "auto-<float-value>" ]

```

The above key:value pairs drive timing closure on the user clocks during AF compilation and are used to bound the frequency value configured in the PLL circuits of the target hardware platform that provides the user clocks through the clocks interface. The chosen frequency may vary in each compilation.

Setting the value field to a float number (e.g., 200.0 to specify 200 MHz) drives the AF generation process to close timing within the bounds set by the low and high keys and set in the AF's JSON metadata to specify the user clock PLL circuit frequency values.

Below is an example of .json file that sets the AFU uClk frequency to 300 MHz and uClk\_div2 to 200 MHz. It also operates the CCI-P interface on uClk instead of the default pClk clock domain.

Below is an example of .json file that sets the AFU uClk frequency to 300 MHz or above and uClk\_div2 to 150 MHz or below. The auto setting allows the build flow to make adjustments to the frequency in the event that timing cannot be met. It also operates the CCI-P interface on pClk and the local SDRAM on the uClk clock domain instead of the default SDRAM domain.

```

"version": 1,

"afu-image": {

"power": 0,

"clock-frequency-high": "300-auto",

```

```

"clock-frequency-low": "auto-150",

"afu-top-interface":

ł

"class": "ccip_std_afu_avalon_mm"

"module-ports" :

[

{

"class": "cci-p",

"params":

{

"clock": "pClk"

"class": "local-memory",

"params":

{

"clock": "uClk usr"

}

1

},

"accelerator-clusters":

[

"name": "b_afu",

"total-contexts": 1,

"accelerator-type-uuid": "233254b9-7db4-42a2-91db-1f1c53d12a76"

}

1

}

}

```

- Warning: AFU developers must ensure the hardware design meets timing by analyzing the static timing reports in Timing Analyzer. AFU developers must inform software developers of the maximum operating frequency (Fmax) of the user clocks so that the maximum frequency never exceeds. Exceeding the Fmax of any clock leads to indeterministic behavior of the accelerator and potentially the overall system.

- Note: AFUs that use uClk or uClk\_div2 may not have accurate timing analysis results shown in the Intel Quartus Prime timing summary. This is a result of PLL tuning post compilation that occurs to determine if your AFU meets timing. You must either load the compiled design in Timing Analyzer or view the results of the /build/output \_files/timing\_report directory. Each of these methods accounts for the uClk and uClk\_div2 frequencies being adjusted. To determine if there are any failing paths in your design, you can inspect the file /build/output\_files/ timing report/clocks.sta.fail.summary. If this file is empty then there are no timing failures in the design.

- Note: There are two clock sources provided for the user clock. Clk 1x and Clk 2x. The high setting controls the Clk\_2x and low setting controls the Clk\_1x. There is a fixed relationship between these two clocks, except when low clock exceeds 300 MHz, then the high clock frequency matches the low clock frequency.

The "auto" setting enables the auto-timing closure mode during AF generation. The AF generation build process automatically converge on a maximum frequency of operation on the user clocks and generate AF JSON metadata to specify the autotiming closure frequency achieved to OPAE tools.

5. Developing AFUs with the OPAE SDK UG-20169 | 2020.03.02

You can combine the "auto" mode with an upper and lower bound specification using the "auto-<float-value>" format (e.g., "auto-300" to specify auto-timing closure bounded to 300MHz).

For example, the  $hello\_mem\_afu$  sample AFU synchronizes all interfaces to  $uClk\_usr$  and uses auto-timing closure mode:

\$OPAE\_PLATFORM\_ROOT/hw/samples/hello\_mem\_afu/hw/rtl/ hello\_mem\_afu.json

#### 5.3.2.2. Design the AFU

#### 5.3.2.2.1. Start with a Top-level Module Template

The top-level AFU interface requested in the platform configuration file defines the AFU's top-level RTL module port definition. Use the top-level module templates from OPAE or a corresponding AFU sample's top-level module as a reference for your AFU's top-level module port definition according to the top-level AFU interface requested in the platform configuration file.

OPAE top-level AFU RTL module templates are in the following location in the OPAE SDK: \$OPAE\_PLATFORM\_ROOT/sw/<opae-version>/platforms/

afu\_top\_ifc\_db/

You can find the AFU samples at the following location in the OPAE SDK:SDK:SDK:SDK:

#### Table 5. Associated Interface with Top-Level Module Template

| Requested Top-Level Interface | Top-Level AFU RTL Module Templates                                                                                           |

|-------------------------------|------------------------------------------------------------------------------------------------------------------------------|

| ccip_std_afu                  | Blank OPAE template: ccip_std_afu.sv.template<br>Sample AFU reference: hello_afu/hw/rtl/<br>ccip_std_afu.sv                  |

| ccip_std_afu_avalon_mm        | Blank OPAE template:<br>ccip_std_afu_avalon_mm.sv.template<br>Sample AFU reference: hello_mem_afu/hw/rtl/<br>ccip_std_afu.sv |

If you extend one of the above basic top-level AFU interfaces to add additional device interfaces (e.g., hssi), manually add the module ports for the added device interfaces. For example, the Ethernet sample AFUs extend the ccip\_std\_afu top-level AFU interface by adding an hssi device interface as shown in the following sample AFU top-level module RTL source files:

\$OPAE\_PLATFORM\_ROOT/hw/samples/eth\_e2e\_e10/hw/rtl/ccip\_std\_afu.sv

\$OPAE\_PLATFORM\_ROOT/hw/samples/eth\_e2e\_e40/hw/rtl/ccip\_std\_afu.sv

\$OPAE\_PLATFORM\_ROOT/hw/samples/hssi\_prbs/hw/rtl/ccip\_std\_afu.sv

#### 5.3.2.2.2. Including the Platform Device Interface Definitions

All RTL source in the AFU's implementation that references device interfaces defined by the OPAE Platform (e.g., cci-p, local-memory) must include the following Verilog header: `include "platform\_if.vh"

The top-level AFU RTL module templates in OPAE and the sample AFUs all include platform\_if.vh.

#### 5.3.2.2.3. Using the AFU UUID Header File

The AFU UUID should be specified in one place: the platform configuration file. The AFU implementation should extract the UUID from the following header file emitted by the PIM: afu\_json\_info.vh

The AFU should use the AFU\_ACCEL\_UUID macro defined within afu\_json\_info.vh to set the AFU's UUID in its implementation. For example, the hello\_afu sample AFU includes the afu json info.vh and sets the AFU UUID using the afu json info.vh macro in the following SystemVerilog source file:

\$OPAE PLATFORM ROOT/hw/samples/hello afu/hw/rtl/afu.sv

#### 5.3.2.2.4. Clock Abstraction for the cci-p Device Interface

The PIM abstracts the clock and reset for the cci-p device interface passed to the AFU with the following Verilog macros:

- PLATFORM PARAM CCI P CLOCK •

- PLATFORM\_PARAM\_CCI\_P\_RESET

The following RTL code snippet shows how to utilize the above macros to set the clock and reset signals in the AFU implementation for the cci-p interface:

```

`include "platform_if.vh"

logic clk;

assign clk = `PLATFORM_PARAM_CCI_P_CLOCK;

logic reset;

assign reset = `PLATFORM_PARAM_CCI_P_RESET;

```

This clock and reset abstraction enables compatibility for an AFU design's clock and reset connectivity on the cci-p device interface regardless of any clock-crossing requested in the platform configuration file.

The hello mem afu sample AFU provides an example for using the macro abstractions:

\$OPAE\_PLATFORM\_ROOT/hw/samples/hello\_mem\_afu/hw/rtl/ ccip std afu.sv

#### 5.3.2.2.5. Generating an AF Build Environment for Source Development

The OPAE SDK design flows for AFU development shown in this guide apply exactly as shown if the AFU design description is all RTL. However, if you want to design all or a portion of your AFU with Platform Designer subsystems or IP variants or want to add in-system debug components to the AFU design, it is helpful to generate an AF build environment for use in developing the AFU design description.

First, configure the build environment with a build configuration file as specified in the section Generate the AF Build Environment. The build configuration file is a text file that, at a minimum, consists of a single line that references the AFU's platform configuration file (. json). The file reference can be absolute or relative to the directory where the build configuration file resides.

Then, generate an AF build environment with the following command from an open terminal window:

afu\_synth\_setup --source \ <path-to-build-configuration-file>/<build-configuration-filename> build\_synth cd build\_synth/build quartus dcp.qpf

Once the Intel Quartus Prime Pro Edition GUI opens, open the dcp.qpf project file and use the revisions feature to create a new revision based on the afu\_synth revision and give it a unique name (e.g., afu\_dev). Use the newly created revision as a workspace to develop the AFU's design description with tools such as Platform Designer or to add debug instances with tools such as Signal Tap. This method enables AFU design description development with high level, GUI-based tools in Quartus Prime Pro without corrupting the PR compilation revisions provided by the OPAE SDK for generating an AF.

#### **5.3.2.3. AFU Design Guidelines**

Follow these guidelines when designing a custom AFU:

#### 5.3.2.3.1. General Guidelines

- The OPAE SDK supports the following RTL language standards:

- SystemVerilog 2005

- VHDL 1993

- Reset and initialize all output registers to OPAE device interfaces.

#### **Related Information**

Intel Quartus Prime Pro Edition Handbook Volume 1 Design and Compilation

#### 5.3.2.3.2. Utilizing Clock Resources

The FIM provides several clock resources for use by AFUs. One set of clock resources is the user clock group, which includes uClk\_usr and uClk\_usrDiv2. Unlike pClk and its derivatives whose frequencies are fixed by the *CCI-P Specification*, the user clocks can be programmed for a range of frequencies supported by the AFU.

User clocks get provisioned by OPAE when an AF is loaded by the fpgaconf utility. When the fpgaconf utility loads an AF, it configures the PLL in the FIM that sources the user clocks with the frequency specified by a key:value pair found in the AF metadata generated by the packager utility. The desired user clock frequency key:value pair can be specified in a .json file or can be specified with a command line option (overrides entry in the .json file) to the packager utility. You can use the packager to generate AFs with unique metadata user clock frequency values for a single AFU PR bitstream.

The FIM reset resource, pck\_cp2af\_softReset, is not released until all clock

resources are stable and locked, including the user clocks.

The AFU design must close timing on the user clocks at the maximum frequency to be supported by the AFU. Place associated clock timing constraints in a .sdc file and refer to the .sdc file in the AFU's build configuration file.

For usage information on the **Packager** utility and . json file metadata format, supported keyword parameters, and minimum metadata requirements, refer to the packager tab in the Open Programmable Acceleration Engine (OPAE) Tools User Guide.

#### **Related Information**

Open Programmable Acceleration Engine (OPAE) Tools Guide

#### 5.3.2.3.3. Interfacing with the FPGA Interface Manager (FIM)

The Intel Acceleration Stack for Intel Xeon CPU with FPGAs Core Cache interface (CCI-P) Reference Manual documents all the requirements for an AFU interfacing with the FIM using the CCI-P protocol. An AFU design must meet all the requirements specified in the following sections of the CCI-P reference manual:

- CCI-P Interface

- AFU Requirements

- Device Feature List

The above sections in the CCI-P reference manual include requirements unique to the Intel Xeon Processor with Integrated FPGA (referred to as Integrated FPGA Platform throughout this document) hardware platform, but most of the information applies to the Intel FPGA PAC. The notable differences between the two platforms are that the Intel FPGA PACs do not have a UPI channel or second PCIe link and no accelerator cache is implemented in the FIM.

The hello\_afu example AFU included with the Acceleration Stack provides an example implementation of a simple Device Feature List that meets the requirements for an AFU as specified by the CCI-P reference manual. The nlb mode 0 and dma afu example AFUs provide example implementations of more featured Device Feature Lists.

#### 5.3.2.4. Partial Reconfiguration Design Guidelines

- You must generate the AF bitstream using the <code>\$OPAE\_PLATFORM\_ROOT/bin/</code> run.sh script.

- Partial reconfiguration switches the PR region from one AFU to another AFU. Any software application exercising an AFU in the PR region should be terminated before initiating PR with OPAE to switch in a new AFU. This includes the remote debug feature.

- After PR, the default initial state of the registers and the contents of the MLABs and M20Ks in the PR region are indeterminate. To establish, a known initial condition for synchronous elements in the AFU, follow the guidelines below:

- Design registers with reset logic sensitive to the FIU's pck cp2af softReset output. Do not rely on RTL initial value assignments or initial blocks.

- Initialize MLAB and M20K contents using .mif files or RTL encoded values. Please refer to the Intel Quartus Prime Pro Edition Handbook Volume 1 Design and Compilation document for inferring or instantiating memory with initialized contents.

- The PR region must contain only core resources such as LABs, RAMs and DSPs. PLLs and Clock control blocks cannot be instantiated in the PR region.

- The placement and routing of a given AFU can vary between OPAE SDK releases and different OPAE hardware platform targets. Use seed sweeps for large resources or routing-intensive designs.

- If PR compilation results in timing violations in the FIM static region, retry PR compilation with a different fitter seed value.

#### **Related Information**

Intel Quartus Prime Pro Edition Handbook Volume 1 Design and Compilation

#### 5.3.2.5. Specify the Build Configuration

The AFU configures the build environments generated by the PIM for simulation with ASE and AF generation with a build configuration file. The build configuration file is a text file created by the AFU designer to specify the following to the PIM:

- The AFU's platform configuration file (.json)

- List of simulation and synthesis source files:

- RTL source (.v, .sv, .vhd)

- Platform Designer subsystems (.qsys)

- IP variants (.ip)

- List of additional source and constraints used during AF generation:

- Signal Tap files (.stp)

- Intel Quartus Prime Pro Edition settings (.qsf)

- Timing constraints (.sdc)

- List of search paths at simulation or AF generation time

- List of include files at PIM build environment generation time

- Reusable submodule (e.g., BBBs) build configuration files

- Verilog macro definitions

The build configuration file has the following format:

- Prefixes specify whether a reference is to a simulation or synthesis design file, include file or macro definition.

- File references can be absolute or relative to the directory containing the build configuration file.

For a full description of the build configuration file format and semantics, check the rtl\_src\_config command help:

\$ rtl\_src\_config -h

See the following AFU samples located at  $OPAE_PLATFORM_ROOT/hw/samples$  for examples of build configuration files:

- Simple examples:

- hello\_afu/hw/rtl/filelist.txt

- hello\_mem\_afu/hw/rtl/filelist.txt

- hello intr afu/hw/rtl/filelist.txt

- Examples with IP references and macro definitions:

- dma\_afu/hw/rtl/filelist.txt

- eth e2e e10/hw/rtl/filelist.txt

- eth\_e2e\_e40/hw/rtl/filelist.txt

- Examples with IP references, macro definitions and include references:

- nlb\_mode\_0/hw/rtl/filelist\_mode\_0.txt

- nlb\_mode\_0\_stp/hw/rtl/filelist\_mode\_0\_stp

The afu\_sim\_setup and afu\_synth\_setup use rtl\_src\_config internally to generate the appropriate fileset. Intel recommends that you use afu\_sim\_setup and afu synth setup instead of rtl src config directly.

#### 5.3.2.6. Generate the ASE Build Environment

To generate a simulation build environment to verify your AFU with ASE, use the afu sim setup command:

```

afu_sim_setup --source \

<path-to-build-configuration-file>/<build-configuration-filename> <build-dir-</pre>

name>

```

For example, the following command sequence generates a simulation build environment for the hello afu sample AFU in the build sim directory:

cd \$OPAE\_PLATFORM\_ROOT/hw/samples/hello\_afu

afu\_sim\_setup --source hw/rtl/filelist.txt build\_sim

As you iterate on the verification flow, you need to regenerate the simulation build environment with the afu\_sim\_setup command if either of the platform configuration or build configuration files have been modified according to design modifications. You can overwrite an existing simulation build directory by invoking the afu sim setup command with the -f command line option, or you can create a separate build environment by specifying a new target directory.

For a description of the full set of command line options and semantics, see the afu\_sim\_setup command help:

afu\_sim\_setup -h

The afu\_sim\_setup command calls the rtl\_src\_config command as part of the synthesis build environment generation process.

#### 5.3.2.7. Verify the AFU with ASE

The ASE supports functional verification of AFU RTL code using host application C code developed for the OPAE API without the need for accelerator hardware. The ASE virtualizes the AFU's physical link with the host, models certain aspects of the OPAE

host memory model, and supports communication between the OPAE host application and supported RTL simulation tools used to emulate the AFU running on an actual OPAE-compliant accelerator hardware target.