Consent Manager Tag v2.0 (for TCF 2.0) -->

Farnell PDF

Surge arrester, EF800X - Farnell

Surge arrester, EF800X - Farnell

Surge arrester, EF800X - Farnell

- Revenir à l'accueil

Farnell Element 14 :

See the trailer for the next exciting episode of The Ben Heck show. Check back on Friday to be among the first to see the exclusive full show on element…

Connect your Raspberry Pi to a breadboard, download some code and create a push-button audio play project.

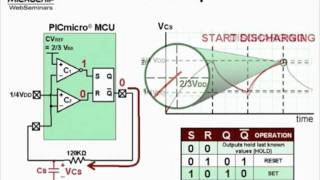

Puce électronique / Microchip :

Sans fil - Wireless :

Texas instrument :

Ordinateurs :

Logiciels :

Tutoriels :

Autres documentations :

Crucial-Ballistix-El..> 20-Dec-2014 17:06 8.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Crucial-Data-Transfe..> 20-Dec-2014 17:05 8.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Crucial-Guide-pour-l..> 20-Dec-2014 17:02 8.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Crucial-Guide-pratiq..> 20-Dec-2014 17:00 8.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Crucial-Guide-pratiq..> 20-Dec-2014 17:08 8.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Crucial-Technologie-..> 20-Dec-2014 17:10 8.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Crucial-The-power-de..> 20-Dec-2014 17:03 8.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Crucial-View-our-DDR..> 20-Dec-2014 17:09 8.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Surge-arrest..> 20-Dec-2014 17:17 8.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Atmel-OLED1-..> 20-Dec-2014 16:59 5.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PIC18FXX2-Da..> 20-Dec-2014 16:58 6.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Atmel-AT42QT..> 20-Dec-2014 16:57 5.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PIC18F2420-2..> 20-Dec-2014 16:55 6.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ATtiny25-V-A..> 20-Dec-2014 16:55 6.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PIC18F1220-1..> 20-Dec-2014 16:53 7.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Crucial-DDR4..> 20-Dec-2014 16:53 7.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-uPSD33xx-Tur..> 20-Dec-2014 16:50 8.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ESMT-M52D323..> 20-Dec-2014 16:50 7.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Crucial-Ball..> 20-Dec-2014 16:48 8.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Fluke-Ti400-..> 20-Dec-2014 16:48 8.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Crucial-Technologie-..> 20-Dec-2014 16:45 8.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Crucial-View-our-DDR..> 20-Dec-2014 16:45 8.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Crucial-Guide-pratiq..> 20-Dec-2014 16:42 8.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Crucial-Ballistix-El..> 20-Dec-2014 16:42 8.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Crucial-Data-Transfe..> 20-Dec-2014 16:39 8.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Crucial-The-power-de..> 20-Dec-2014 16:39 8.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Crucial-Guide-pratiq..> 20-Dec-2014 16:37 8.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Crucial-Guide-pour-l..> 20-Dec-2014 16:37 8.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ATtiny1634-d..> 20-Dec-2014 11:44 5.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-AT42QT1040-M..> 20-Dec-2014 11:44 4.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-AT42QT1010-D..> 20-Dec-2014 11:43 4.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ATTINY4-5-9-..> 20-Dec-2014 11:42 2.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ATmega8-L-da..> 20-Dec-2014 11:41 2.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Atmel-AVR192..> 20-Dec-2014 11:41 2.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-STK600-Expan..> 20-Dec-2014 11:41 3.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ATmega8A-dat..> 20-Dec-2014 11:41 3.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Atmel-SAM4S-..> 20-Dec-2014 11:39 3.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ATxmega128A1..> 20-Dec-2014 11:39 3.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ATtiny24A-44..> 20-Dec-2014 11:38 3.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Atmel-Xplain..> 20-Dec-2014 11:38 3.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ATtiny2313A-..> 20-Dec-2014 11:37 4.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ATmega329-32..> 20-Dec-2014 11:37 4.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-8-bit-Atmel-..> 20-Dec-2014 11:01 2.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Atmel-ICE-US..> 20-Dec-2014 11:00 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Atmel-ATtiny..> 20-Dec-2014 11:00 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Atmel-QTouch..> 20-Dec-2014 11:00 2.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-AT90USB64-12..> 20-Dec-2014 10:59 4.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ATmega48-88-..> 20-Dec-2014 10:59 3.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LPC81xM-NXP-..> 20-Dec-2014 10:26 1.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-CLRC632-NXP-..> 20-Dec-2014 10:22 2.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-7491181012-O..> 20-Dec-2014 10:22 2.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LPC4350-30-2..> 20-Dec-2014 10:21 1.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LPC178x-7x-N..> 20-Dec-2014 10:21 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Data-Sheet-J..> 20-Dec-2014 10:21 1.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Data-Sheet-J..> 20-Dec-2014 10:20 1.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-SL3S1003_101..> 20-Dec-2014 10:06 2.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-NT3H1101-NT3..> 20-Dec-2014 10:06 2.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LPC1769-68-6..> 20-Dec-2014 10:06 2.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-SL3S1203_121..> 20-Dec-2014 10:01 2.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PN512-NXP-Se..> 20-Dec-2014 10:01 1.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MMBZxVCL-MMB..> 20-Dec-2014 09:53 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Datasheet-NX..> 20-Dec-2014 09:52 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-IP4251_52_53..> 20-Dec-2014 09:51 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-BC846DS2-NXP..> 20-Dec-2014 09:48 1.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-BAT54J-Schot..> 20-Dec-2014 09:47 1.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PMEG3010EP-N..> 20-Dec-2014 09:47 1.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-AVR172-Senso..> 20-Dec-2014 09:47 1.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PBSS5320X-NX..> 20-Dec-2014 09:47 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ATtiny2313-A..> 20-Dec-2014 09:47 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-SG2525A-SG35..> 20-Dec-2014 09:39 1.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PMBT3906-PNP..> 20-Dec-2014 09:39 1.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PDTB123TT-NX..> 20-Dec-2014 09:39 1.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PIC12F529T39..> 20-Dec-2014 09:39 1.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PSMN011-80YS..> 20-Dec-2014 09:39 1.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PESD5V0F1BL-..> 20-Dec-2014 09:39 1.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MB85RS128B-F..> 20-Dec-2014 09:38 1.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-CLRC632-NXP-..> 20-Dec-2014 10:22 2.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-7491181012-O..> 20-Dec-2014 10:22 2.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LPC4350-30-2..> 20-Dec-2014 10:21 1.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LPC178x-7x-N..> 20-Dec-2014 10:21 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Data-Sheet-J..> 20-Dec-2014 10:21 1.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LPC81xM-NXP-..> 20-Dec-2014 10:20 1.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Data-Sheet-J..> 20-Dec-2014 10:20 1.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-SL3S1003_101..> 20-Dec-2014 10:06 2.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-NT3H1101-NT3..> 20-Dec-2014 10:06 2.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LPC1769-68-6..> 20-Dec-2014 10:06 2.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-SL3S1203_121..> 20-Dec-2014 10:01 2.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PN512-NXP-Se..> 20-Dec-2014 10:01 1.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MMBZxVCL-MMB..> 20-Dec-2014 09:53 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Datasheet-NX..> 20-Dec-2014 09:52 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-IP4251_52_53..> 20-Dec-2014 09:51 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-BC846DS2-NXP..> 20-Dec-2014 09:48 1.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-BAT54J-Schot..> 20-Dec-2014 09:47 1.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PMEG3010EP-N..> 20-Dec-2014 09:47 1.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-AVR172-Senso..> 20-Dec-2014 09:47 1.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PBSS5320X-NX..> 20-Dec-2014 09:47 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ATtiny2313-A..> 20-Dec-2014 09:47 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-SG2525A-SG35..> 20-Dec-2014 09:39 1.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PMBT3906-PNP..> 20-Dec-2014 09:39 1.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PDTB123TT-NX..> 20-Dec-2014 09:39 1.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PIC12F529T39..> 20-Dec-2014 09:39 1.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PSMN011-80YS..> 20-Dec-2014 09:39 1.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PESD5V0F1BL-..> 20-Dec-2014 09:39 1.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MB85RS128B-F..> 20-Dec-2014 09:38 1.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-SMAJ-STMicro..> 13-Oct-2014 07:07 734K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-L6562-STMicr..> 13-Oct-2014 07:07 754K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LM139-LM239-..> 13-Oct-2014 07:07 771K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-L4978-STMicr..> 13-Oct-2014 07:07 783K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ST1S10PHR-ST..> 13-Oct-2014 07:06 820K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TIP41C-TIP42..> 13-Oct-2014 07:06 829K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MC34063ABD-T..> 13-Oct-2014 07:06 844K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ESM6045DV-ST..> 13-Oct-2014 07:06 850K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TIP102-TIP10..> 13-Oct-2014 07:06 853K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ST3232B-ST32..> 13-Oct-2014 07:06 867K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-STM32F030x4-..> 13-Oct-2014 07:06 1.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-STM32F103x8-..> 13-Oct-2014 07:06 1.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-STM32F405xx-..> 13-Oct-2014 07:05 1.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-STM32F205xx-..> 13-Oct-2014 07:05 1.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-STP16NF06L-n..> 13-Oct-2014 07:05 1.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-STP80NF55L-0..> 13-Oct-2014 07:05 1.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LM217-LM317-..> 13-Oct-2014 07:04 1.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LM2904-LM290..> 13-Oct-2014 07:04 1.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-L78-Positive..> 13-Oct-2014 07:04 1.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-VND920P-E-ST..> 13-Oct-2014 07:04 1.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LM350-STMicr..> 13-Oct-2014 07:03 1.8M

![[ ]](http://www.audentia-gestion.fr/icons/layout.gif)

Smart_street_lightin..> 13-Oct-2014 07:03 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Smart-street..> 13-Oct-2014 07:02 1.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ULN2001-ULN2..> 13-Oct-2014 07:02 1.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ULQ2001-ULQ2..> 13-Oct-2014 07:02 1.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-L6384E-STMic..> 13-Oct-2014 07:02 1.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-AN2794-Appli..> 13-Oct-2014 07:01 1.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-STEVAL-TDR02..> 13-Oct-2014 07:01 960K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TL084-TL084A..> 11-Oct-2014 15:54 1.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TDA7296-STMi..> 11-Oct-2014 15:54 1.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-L78-STMicroe..> 11-Oct-2014 15:49 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LM158-LM258-..> 11-Oct-2014 15:49 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LF351-STMicr..> 11-Oct-2014 15:49 1.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-L293B-STMicr..> 11-Oct-2014 15:49 1.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-NE556-SA556-..> 11-Oct-2014 15:48 1.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-SO967460-PDF..> 11-Oct-2014 12:05 2.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Everything-Y..> 11-Oct-2014 12:05 1.5M

![[ ]](http://www.audentia-gestion.fr/icons/unknown.gif)

cookiechoices.js 27-Sep-2014 12:40 6.0K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ULN2803A-Rev..> 09-Sep-2014 19:26 2.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Analog-Devices-Convo..> 09-Sep-2014 08:26 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Analog-Devices-Convo..> 09-Sep-2014 08:25 2.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Analog-Devices-Convo..> 09-Sep-2014 08:25 2.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Analog-Devices-ADMC4..> 09-Sep-2014 08:23 2.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Analog-Devices-Wi-Fi..> 09-Sep-2014 08:23 2.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Analog-Devices-ADMC2..> 09-Sep-2014 08:21 2.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Analog-Devices-ADC-S..> 09-Sep-2014 08:21 2.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Analog-Devices-Visua..> 09-Sep-2014 08:18 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Analog-Devices-ANF32..> 09-Sep-2014 08:18 2.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Compensating..> 09-Sep-2014 08:16 2.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Compensating..> 09-Sep-2014 08:16 2.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LM7805-Fairc..> 09-Sep-2014 08:13 2.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-AD620-Rev-H-..> 09-Sep-2014 08:13 2.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Datasheet-FT..> 09-Sep-2014 08:10 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MAX4661-MAX4..> 09-Sep-2014 08:10 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-OPA627-Texas..> 09-Sep-2014 08:08 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-REF19x-Serie..> 09-Sep-2014 08:08 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Data-Sheet-M..> 09-Sep-2014 08:05 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Analog-Devices-Digit..> 08-Sep-2014 18:03 2.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Analog-Devices-Digit..> 08-Sep-2014 18:02 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Analog-Devices-Basic..> 08-Sep-2014 17:49 1.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-AD9833-Rev-E..> 08-Sep-2014 17:49 1.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-The-Discrete..> 08-Sep-2014 17:44 1.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Electronique-Basic-o..> 08-Sep-2014 17:43 1.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Analog-Devices-AN300..> 08-Sep-2014 17:42 2.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Analog-Devices-The-C..> 08-Sep-2014 17:41 1.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Analog-Devices-Intro..> 08-Sep-2014 17:39 1.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Analog-Devices-Compl..> 08-Sep-2014 17:38 2.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Analog-Devices-Gloss..> 08-Sep-2014 17:36 2.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ADuM1300-ADu..> 08-Sep-2014 08:11 1.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-AD586BRZ-Ana..> 08-Sep-2014 08:09 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ADuM1200-ADu..> 08-Sep-2014 08:09 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-NA555-NE555-..> 08-Sep-2014 07:51 1.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-AD9834-Rev-D..> 08-Sep-2014 07:32 1.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MSP430F15x-M..> 08-Sep-2014 07:32 1.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-AD736-Rev-I-..> 08-Sep-2014 07:31 1.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-AD8307-Data-..> 08-Sep-2014 07:30 1.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Single-Chip-..> 08-Sep-2014 07:30 1.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Quadruple-2-..> 08-Sep-2014 07:29 1.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ADE7758-Rev-..> 08-Sep-2014 07:28 1.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MAX3221-Rev-..> 08-Sep-2014 07:28 1.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-USB-to-Seria..> 08-Sep-2014 07:27 2.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-AD8313-Analo..> 08-Sep-2014 07:26 2.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-SN54HC164-SN..> 08-Sep-2014 07:25 2.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-AD8310-Analo..> 08-Sep-2014 07:24 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-AD8361-Rev-D..> 08-Sep-2014 07:23 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-2N3906-Fairc..> 08-Sep-2014 07:22 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-AD584-Rev-C-..> 08-Sep-2014 07:20 2.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ADE7753-Rev-..> 08-Sep-2014 07:20 2.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TLV320AIC23B..> 08-Sep-2014 07:18 2.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-STM32F405xxS..> 27-Aug-2014 18:27 1.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-fx-3650P-fx-..> 29-Jul-2014 10:42 1.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MSP430-Hardw..> 29-Jul-2014 10:36 1.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LM324-Texas-..> 29-Jul-2014 10:32 1.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LM386-Low-Vo..> 29-Jul-2014 10:32 1.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-NE5532-Texas..> 29-Jul-2014 10:32 1.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Hex-Inverter..> 29-Jul-2014 10:31 875K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-AT90USBKey-H..> 29-Jul-2014 10:31 902K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-AT89C5131-Ha..> 29-Jul-2014 10:31 1.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MSP-EXP430F5..> 29-Jul-2014 10:31 1.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Explorer-16-..> 29-Jul-2014 10:31 1.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TMP006EVM-Us..> 29-Jul-2014 10:30 1.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Gertboard-Us..> 29-Jul-2014 10:30 1.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LMP91051-Use..> 29-Jul-2014 10:30 1.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Thermometre-..> 29-Jul-2014 10:30 1.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-user-manuel-..> 29-Jul-2014 10:29 1.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TLV320AIC325..> 28-Jul-2014 17:45 2.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-2-GBPS-Diffe..> 28-Jul-2014 17:42 2.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LMT88-2.4V-1..> 28-Jul-2014 17:42 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Octal-Genera..> 28-Jul-2014 17:42 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Dual-MOSFET-..> 28-Jul-2014 17:41 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-SN54LV4053A-..> 28-Jul-2014 17:20 5.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TAS1020B-USB..> 28-Jul-2014 17:19 6.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TPS40060-Wid..> 28-Jul-2014 17:19 6.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TL082-Wide-B..> 28-Jul-2014 17:16 6.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-RF-short-tra..> 28-Jul-2014 17:16 6.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-maxim-integr..> 28-Jul-2014 17:14 6.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TSV6390-TSV6..> 28-Jul-2014 17:14 6.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Fast-Charge-..> 28-Jul-2014 17:12 6.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-NVE-datashee..> 28-Jul-2014 17:12 6.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Excalibur-Hi..> 28-Jul-2014 17:10 2.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Excalibur-Hi..> 28-Jul-2014 17:10 2.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-REF102-10V-P..> 28-Jul-2014 17:09 2.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TMS320F28055..> 28-Jul-2014 17:09 2.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ULINKpro-Deb..> 25-Jul-2014 12:35 5.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-WIRE-WRAP-50..> 25-Jul-2014 12:34 5.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MICROCHIP-PI..> 25-Jul-2014 12:34 6.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-OMRON-INDUST..> 25-Jul-2014 12:32 6.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-OMRON-INDUST..> 25-Jul-2014 12:31 6.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TYCO-ELECTRO..> 25-Jul-2014 12:30 6.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Power-suppli..> 25-Jul-2014 12:29 7.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Schroff-A108..> 25-Jul-2014 12:27 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Schroff-Main..> 25-Jul-2014 12:26 2.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Schroff-mult..> 25-Jul-2014 12:26 2.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Quick-Start-..> 25-Jul-2014 12:25 3.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PiFace-Digit..> 25-Jul-2014 12:25 3.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PicoScope-se..> 25-Jul-2014 12:24 3.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Trust-Digita..> 25-Jul-2014 12:24 3.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Jeu-multi-la..> 25-Jul-2014 12:23 3.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PicoScope-42..> 25-Jul-2014 12:23 3.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LD-WSECO16-P..> 25-Jul-2014 12:22 3.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Circuit-Impr..> 25-Jul-2014 12:22 3.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MULTICOMP-Ra..> 22-Jul-2014 12:57 5.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-RASPBERRY-PI..> 22-Jul-2014 12:35 5.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Dremel-Exper..> 22-Jul-2014 12:34 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-STM32F103x8-..> 22-Jul-2014 12:33 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-BD6xxx-PDF.htm 22-Jul-2014 12:33 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-L78S-STMicro..> 22-Jul-2014 12:32 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-RaspiCam-Doc..> 22-Jul-2014 12:32 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-SB520-SB5100..> 22-Jul-2014 12:32 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-iServer-Micr..> 22-Jul-2014 12:32 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LUMINARY-MIC..> 22-Jul-2014 12:31 3.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TEXAS-INSTRU..> 22-Jul-2014 12:31 2.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TEXAS-INSTRU..> 22-Jul-2014 12:30 4.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-CLASS 1-or-2..> 22-Jul-2014 12:30 4.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TEXAS-INSTRU..> 22-Jul-2014 12:29 4.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Evaluating-t..> 22-Jul-2014 12:28 4.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LM3S6952-Mic..> 22-Jul-2014 12:27 5.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Keyboard-Mou..> 22-Jul-2014 12:27 5.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-0050375063-D..> 18-Jul-2014 17:03 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Mini-Fit-Jr-..> 18-Jul-2014 17:03 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-43031-0002-M..> 18-Jul-2014 17:03 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-0433751001-D..> 18-Jul-2014 17:02 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Cube-3D-Prin..> 18-Jul-2014 17:02 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MTX-Compact-..> 18-Jul-2014 17:01 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MTX-3250-MTX..> 18-Jul-2014 17:01 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ATtiny26-L-A..> 18-Jul-2014 17:00 2.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MCP3421-Micr..> 18-Jul-2014 17:00 1.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LM19-Texas-I..> 18-Jul-2014 17:00 1.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Data-Sheet-S..> 18-Jul-2014 17:00 1.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LMH6518-Texa..> 18-Jul-2014 16:59 1.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-AD7719-Low-V..> 18-Jul-2014 16:59 1.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-DAC8143-Data..> 18-Jul-2014 16:59 1.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-BGA7124-400-..> 18-Jul-2014 16:59 1.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-SICK-OPTIC-E..> 18-Jul-2014 16:58 1.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LT3757-Linea..> 18-Jul-2014 16:58 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LT1961-Linea..> 18-Jul-2014 16:58 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PIC18F2420-2..> 18-Jul-2014 16:57 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-DS3231-DS-PD..> 18-Jul-2014 16:57 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-RDS-80-PDF.htm 18-Jul-2014 16:57 1.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-AD8300-Data-..> 18-Jul-2014 16:56 1.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LT6233-Linea..> 18-Jul-2014 16:56 1.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MAX1365-MAX1..> 18-Jul-2014 16:56 1.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-XPSAF5130-PD..> 18-Jul-2014 16:56 1.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-DP83846A-DsP..> 18-Jul-2014 16:55 1.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-SL3ICS1002-1..> 16-Jul-2014 09:05 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MCOC1-Farnel..> 16-Jul-2014 09:04 1.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-SL3S1203_121..> 16-Jul-2014 09:04 1.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PN512-Full-N..> 16-Jul-2014 09:03 1.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-SL3S4011_402..> 16-Jul-2014 09:03 1.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LPC408x-7x 3..> 16-Jul-2014 09:03 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PCF8574-PCF8..> 16-Jul-2014 09:03 1.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LPC81xM-32-b..> 16-Jul-2014 09:02 2.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LPC1769-68-6..> 16-Jul-2014 09:02 1.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Download-dat..> 16-Jul-2014 09:02 2.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LPC3220-30-4..> 16-Jul-2014 09:02 2.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LPC11U3x-32-..> 16-Jul-2014 09:01 2.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Full-Datashe..> 15-Jul-2014 17:08 951K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-pmbta13_pmbt..> 15-Jul-2014 17:06 959K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-EE-SPX303N-4..> 15-Jul-2014 17:06 969K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Datasheet-NX..> 15-Jul-2014 17:06 1.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Datasheet-Fa..> 15-Jul-2014 17:05 1.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MIDAS-un-tra..> 15-Jul-2014 17:05 1.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-SERIAL-TFT-M..> 15-Jul-2014 17:05 1.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TMR-2-series..> 15-Jul-2014 16:48 787K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-DC-DC-Conver..> 15-Jul-2014 16:48 781K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Full-Datashe..> 15-Jul-2014 16:47 803K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TMLM-Series-..> 15-Jul-2014 16:47 810K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TEL-5-Series..> 15-Jul-2014 16:47 814K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TXL-series-t..> 15-Jul-2014 16:47 829K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TEP-150WI-Se..> 15-Jul-2014 16:47 837K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-AC-DC-Power-..> 15-Jul-2014 16:47 845K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TIS-Instruct..> 15-Jul-2014 16:47 845K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TOS-tracopow..> 15-Jul-2014 16:47 852K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TCL-DC-traco..> 15-Jul-2014 16:46 858K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TIS-series-t..> 15-Jul-2014 16:46 875K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TMR-2-Series..> 15-Jul-2014 16:46 897K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TMR-3-WI-Ser..> 15-Jul-2014 16:46 939K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TEN-8-WI-Ser..> 15-Jul-2014 16:46 939K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-SOURIAU-Cont..> 08-Jul-2014 19:04 3.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-T672-3000-Se..> 08-Jul-2014 18:59 2.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-tesa®pack63..> 08-Jul-2014 18:56 2.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Encodeur-USB..> 08-Jul-2014 18:56 2.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-CC2530ZDK-Us..> 08-Jul-2014 18:55 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-2020-Manuel-..> 08-Jul-2014 18:55 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Synchronous-..> 08-Jul-2014 18:54 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Arithmetic-L..> 08-Jul-2014 18:54 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-NA555-NE555-..> 08-Jul-2014 18:53 2.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-4-Bit-Magnit..> 08-Jul-2014 18:53 2.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LM555-Timer-..> 08-Jul-2014 18:53 2.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-L293d-Texas-..> 08-Jul-2014 18:53 2.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-SN54HC244-SN..> 08-Jul-2014 18:52 2.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MAX232-MAX23..> 08-Jul-2014 18:52 2.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-High-precisi..> 08-Jul-2014 18:51 2.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-SMU-Instrume..> 08-Jul-2014 18:51 2.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-900-Series-B..> 08-Jul-2014 18:50 2.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-BA-Series-Oh..> 08-Jul-2014 18:50 2.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-UTS-Series-S..> 08-Jul-2014 18:49 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-270-Series-O..> 08-Jul-2014 18:49 2.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-UTS-Series-S..> 08-Jul-2014 18:49 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Tiva-C-Serie..> 08-Jul-2014 18:49 2.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-UTO-Souriau-..> 08-Jul-2014 18:48 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Clipper-Seri..> 08-Jul-2014 18:48 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-851-Series-P..> 08-Jul-2014 18:47 3.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-HIP4081A-Int..> 07-Jul-2014 19:47 1.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ISL6251-ISL6..> 07-Jul-2014 19:47 1.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-DG411-DG412-..> 07-Jul-2014 19:47 1.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-3367-ARALDIT..> 07-Jul-2014 19:46 1.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ICM7228-Inte..> 07-Jul-2014 19:46 1.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Data-Sheet-K..> 07-Jul-2014 19:46 1.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Silica-Gel-M..> 07-Jul-2014 19:46 1.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TKC2-Dusters..> 07-Jul-2014 19:46 1.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-CRC-HANDCLEA..> 07-Jul-2014 19:46 1.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-760G-French-..> 07-Jul-2014 19:45 1.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Decapant-KF-..> 07-Jul-2014 19:45 1.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-1734-ARALDIT..> 07-Jul-2014 19:45 1.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Araldite-Fus..> 07-Jul-2014 19:45 1.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-fiche-de-don..> 07-Jul-2014 19:44 1.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-safety-data-..> 07-Jul-2014 19:44 1.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-A-4-Hardener..> 07-Jul-2014 19:44 1.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-CC-Debugger-..> 07-Jul-2014 19:44 1.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-SmartRF06-Ev..> 07-Jul-2014 19:43 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-CC2531-USB-H..> 07-Jul-2014 19:43 1.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Alimentation..> 07-Jul-2014 19:43 1.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-BK889B-PONT-..> 07-Jul-2014 19:42 1.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-User-Guide-M..> 07-Jul-2014 19:41 2.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-SL59830-Inte..> 06-Jul-2014 10:11 1.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ALF1210-PDF.htm 06-Jul-2014 10:06 4.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-AD7171-16-Bi..> 06-Jul-2014 10:06 1.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Low-Noise-24..> 06-Jul-2014 10:05 1.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ESCON-Featur..> 06-Jul-2014 10:05 938K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-74LCX573-Fai..> 06-Jul-2014 10:05 1.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-1N4148WS-Fai..> 06-Jul-2014 10:04 1.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-FAN6756-Fair..> 06-Jul-2014 10:04 850K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Datasheet-Fa..> 06-Jul-2014 10:04 861K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ES1F-ES1J-fi..> 06-Jul-2014 10:04 867K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-QRE1113-Fair..> 06-Jul-2014 10:03 879K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-2N7002DW-Fai..> 06-Jul-2014 10:03 886K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-FDC2512-Fair..> 06-Jul-2014 10:03 886K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-FDV301N-Digi..> 06-Jul-2014 10:03 886K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-S1A-Fairchil..> 06-Jul-2014 10:03 896K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-BAV99-Fairch..> 06-Jul-2014 10:03 896K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-74AC00-74ACT..> 06-Jul-2014 10:03 911K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-NaPiOn-Panas..> 06-Jul-2014 10:02 911K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LQ-RELAYS-AL..> 06-Jul-2014 10:02 924K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ev-relays-ae..> 06-Jul-2014 10:02 926K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ESCON-Featur..> 06-Jul-2014 10:02 931K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Amplifier-In..> 06-Jul-2014 10:02 940K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Serial-File-..> 06-Jul-2014 10:02 941K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Both-the-Del..> 06-Jul-2014 10:01 948K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Videk-PDF.htm 06-Jul-2014 10:01 948K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-EPCOS-173438..> 04-Jul-2014 10:43 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Sensorless-C..> 04-Jul-2014 10:42 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-197.31-KB-Te..> 04-Jul-2014 10:42 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PIC12F609-61..> 04-Jul-2014 10:41 3.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PADO-semi-au..> 04-Jul-2014 10:41 3.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-03-iec-runds..> 04-Jul-2014 10:40 3.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ACC-Silicone..> 04-Jul-2014 10:40 3.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Series-TDS10..> 04-Jul-2014 10:39 4.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Q48-PDF.htm 23-Jun-2014 10:29 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Panasonic-15..> 23-Jun-2014 10:29 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-BZX384-serie..> 23-Jun-2014 10:29 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-AN10361-Phil..> 23-Jun-2014 10:29 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-KSZ8851SNL-S..> 23-Jun-2014 10:28 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-BF545A-BF545..> 23-Jun-2014 10:28 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PIC18F2455-2..> 23-Jun-2014 10:27 3.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PMBT4403-PNP..> 23-Jun-2014 10:27 3.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-24AA024-24LC..> 23-Jun-2014 10:26 3.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Leaded-Trans..> 23-Jun-2014 10:26 3.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-SSC7102-Micr..> 23-Jun-2014 10:25 3.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Fastrack-Sup..> 23-Jun-2014 10:25 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-BC847DS-NXP-..> 23-Jun-2014 10:24 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-HI-70300-Sol..> 14-Jun-2014 18:27 2.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Davum-TMC-PD..> 14-Jun-2014 18:27 2.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Repartiteurs..> 14-Jun-2014 18:26 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Documentatio..> 14-Jun-2014 18:26 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Fiche-de-don..> 14-Jun-2014 18:26 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-SPLC780A1-16..> 14-Jun-2014 18:25 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Construction..> 14-Jun-2014 18:25 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Alimentation..> 14-Jun-2014 18:24 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-C.A-6150-C.A..> 14-Jun-2014 18:24 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Fluke-1730-E..> 14-Jun-2014 18:23 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Ponts-RLC-po..> 14-Jun-2014 18:23 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Serie-Standa..> 14-Jun-2014 18:23 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-FDS-ITW-Spra..> 14-Jun-2014 18:22 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-HFE1600-Data..> 14-Jun-2014 18:22 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TDK-Lambda-H..> 14-Jun-2014 18:21 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-HC49-4H-Crys..> 14-Jun-2014 18:20 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Avvertenze-e..> 14-Jun-2014 18:20 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Ceramic-tran..> 14-Jun-2014 18:19 3.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ADL6507-PDF.htm 14-Jun-2014 18:19 3.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PMEG4002EL-N..> 14-Jun-2014 18:18 3.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Midas-Active..> 14-Jun-2014 18:17 3.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Molex-83421-..> 14-Jun-2014 18:17 3.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Molex-COMMER..> 14-Jun-2014 18:16 3.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-10TPB47M-End..> 14-Jun-2014 18:16 3.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-U2270B-PDF.htm 14-Jun-2014 18:15 3.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-SVPE-series-..> 14-Jun-2014 18:15 2.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-F28069-Picco..> 14-Jun-2014 18:14 2.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Termometros-..> 14-Jun-2014 18:14 2.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Cordless-dri..> 14-Jun-2014 18:13 2.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Battery-GBA-..> 14-Jun-2014 18:13 2.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-CD4536B-Type..> 14-Jun-2014 18:13 2.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-0430300011-D..> 14-Jun-2014 18:13 2.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Mistral-PDF.htm 14-Jun-2014 18:12 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Connectors-N..> 14-Jun-2014 18:12 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-XPS-AC-Octop..> 14-Jun-2014 18:11 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Midas-MCCOG4..> 14-Jun-2014 18:11 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-V4N-PDF.htm 14-Jun-2014 18:11 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Signal-PCB-R..> 14-Jun-2014 18:11 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PIC24FJ256GB..> 14-Jun-2014 09:51 2.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-DC-Fan-type-..> 14-Jun-2014 09:51 1.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-12mm-Size-In..> 14-Jun-2014 09:50 2.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-10BQ060-PDF.htm 14-Jun-2014 09:50 2.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-An-Improved-..> 14-Jun-2014 09:49 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ATmega640-VA..> 14-Jun-2014 09:49 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LME49725-Pow..> 14-Jun-2014 09:49 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Produit-3430..> 14-Jun-2014 09:48 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-USB-Buccanee..> 14-Jun-2014 09:48 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-DC-Fan-type-..> 14-Jun-2014 09:48 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Fiche-de-don..> 14-Jun-2014 09:47 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Nilï¬-sk-E-..> 14-Jun-2014 09:47 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MX670-MX675-..> 14-Jun-2014 09:46 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Tektronix-AC..> 13-Jun-2014 18:44 1.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PMBT3906-PNP..> 13-Jun-2014 18:44 1.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PESD5V0F1BL-..> 13-Jun-2014 18:43 1.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PMEG4010CEH-..> 13-Jun-2014 18:43 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PESD9X5.0L-P..> 13-Jun-2014 18:43 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-BTA204-800C-..> 13-Jun-2014 18:42 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-BYV29F-600-N..> 13-Jun-2014 18:42 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Low-cost-Enc..> 13-Jun-2014 18:42 1.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-BC846DS-NXP-..> 13-Jun-2014 18:42 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-IP4252CZ16-8..> 13-Jun-2014 18:41 1.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-BUJD203AX-NX..> 13-Jun-2014 18:41 1.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Download-dat..> 13-Jun-2014 18:40 1.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-BT151-650R-N..> 13-Jun-2014 18:40 1.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-OXPCIE958-FB..> 13-Jun-2014 18:40 1.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ATtiny26-L-A..> 13-Jun-2014 18:40 1.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Microchip-MC..> 13-Jun-2014 18:27 1.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Pompes-Charg..> 24-Apr-2014 20:23 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Alimentation..> 01-Apr-2014 07:42 3.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-C.A 8332B-C...> 01-Apr-2014 07:40 3.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ALF1225-12-V..> 01-Apr-2014 07:40 3.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-CS5532-34-BS..> 01-Apr-2014 07:39 3.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ALF2412-24-V..> 01-Apr-2014 07:39 3.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Sefram-GUIDE_SIMPLIF..> 29-Mar-2014 11:46 422K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Sefram-CAT_ENREGISTR..> 29-Mar-2014 11:46 461K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Sefram-SP270.pdf-PDF..> 29-Mar-2014 11:46 464K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Sefram-7866HD.pdf-PD..> 29-Mar-2014 11:46 472K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Sefram-GUIDE_SIMPLIF..> 29-Mar-2014 11:46 481K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Sefram-CAT_MESUREURS..> 29-Mar-2014 11:46 435K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Sefram-GUIDE_SIMPLIF..> 29-Mar-2014 11:46 442K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Portable-Ana..> 29-Mar-2014 11:16 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-CC2560-Bluet..> 29-Mar-2014 11:14 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Ferric-Chlor..> 29-Mar-2014 11:14 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MCF532x-7x-E..> 29-Mar-2014 11:14 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-A-True-Syste..> 29-Mar-2014 11:13 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ELMA-PDF.htm 29-Mar-2014 11:13 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-SMBJ-Transil..> 29-Mar-2014 11:12 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-6517b-Electr..> 29-Mar-2014 11:12 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Amplificateu..> 29-Mar-2014 11:11 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ir1150s_fr.p..> 29-Mar-2014 11:11 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-De-la-puissa..> 29-Mar-2014 11:10 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-BK2650A-BK26..> 29-Mar-2014 11:10 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Lubrifiant-a..> 26-Mar-2014 18:00 2.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Circuit-Note..> 26-Mar-2014 18:00 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Circuit-Note..> 26-Mar-2014 18:00 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Current-Tran..> 26-Mar-2014 17:59 2.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Current-Tran..> 26-Mar-2014 17:59 2.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Current-Tran..> 26-Mar-2014 17:58 2.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Current-Tran..> 26-Mar-2014 17:58 2.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Supercapacit..> 26-Mar-2014 17:57 2.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-GALVA-MAT-Re..> 26-Mar-2014 17:57 2.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-GALVA-A-FROI..> 26-Mar-2014 17:56 2.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-1907-2006-PD..> 26-Mar-2014 17:56 2.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ARALDITE-CW-..> 26-Mar-2014 17:56 2.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-06-6544-8-PD..> 26-Mar-2014 17:56 2.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Miniature-Ci..> 26-Mar-2014 17:55 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ARADUR-HY-13..> 26-Mar-2014 17:55 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LOCTITE-3463..> 25-Mar-2014 08:19 3.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LCW-CQ7P.CC-..> 25-Mar-2014 08:19 3.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ATtiny20-PDF..> 25-Mar-2014 08:19 3.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-3M-VolitionT..> 25-Mar-2014 08:18 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-EMC1182-PDF.htm 25-Mar-2014 08:17 3.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MC3510-PDF.htm 25-Mar-2014 08:17 3.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Directive-re..> 25-Mar-2014 08:16 3.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Loctite3455-..> 25-Mar-2014 08:16 3.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LOCTITE-542-..> 25-Mar-2014 08:15 3.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-5910-PDF.htm 25-Mar-2014 08:15 3.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-china_rohs_o..> 21-Mar-2014 10:04 3.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Cles-electro..> 21-Mar-2014 08:13 3.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ARALDITE-201..> 21-Mar-2014 08:12 3.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Premier-Farn..> 21-Mar-2014 08:11 3.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-celpac-SUL84..> 21-Mar-2014 08:11 3.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-S-TRI-SWT860..> 21-Mar-2014 08:11 3.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-3M-Polyimide..> 21-Mar-2014 08:09 3.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Strangkuhlko..> 21-Mar-2014 08:09 3.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Reglement-RE..> 21-Mar-2014 08:08 3.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-techfirst_se..> 21-Mar-2014 08:08 3.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Septembre-20..> 20-Mar-2014 17:46 3.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Telemetres-l..> 20-Mar-2014 17:46 3.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Multi-Functi..> 20-Mar-2014 17:38 3.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-testo-470-Fo..> 20-Mar-2014 17:38 3.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Novembre-201..> 20-Mar-2014 17:38 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-testo-205-20..> 20-Mar-2014 17:37 3.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Panasonic-Ra..> 20-Mar-2014 17:37 2.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Panasonic-Ne..> 20-Mar-2014 17:36 2.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Panasonic-EC..> 20-Mar-2014 17:36 2.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Panasonic-Id..> 20-Mar-2014 17:35 2.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-cree-Xlamp-X..> 20-Mar-2014 17:35 2.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-cree-Xlamp-X..> 20-Mar-2014 17:34 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ADSP-21362-A..> 20-Mar-2014 17:34 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-AD524-PDF.htm 20-Mar-2014 17:33 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MPXV7002-Rev..> 20-Mar-2014 17:33 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-cree-Xlamp-m..> 20-Mar-2014 17:32 2.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-cree-Xlamp-m..> 20-Mar-2014 17:32 2.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-50A-High-Pow..> 20-Mar-2014 17:31 2.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-cree-Xlamp-X..> 20-Mar-2014 17:31 2.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Series-2600B..> 20-Mar-2014 17:30 3.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ECO-Series-T..> 20-Mar-2014 08:14 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PDTA143X-ser..> 20-Mar-2014 08:12 2.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Panasonic-TS..> 20-Mar-2014 08:12 2.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Radial-Lead-..> 20-Mar-2014 08:12 2.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-GN-RELAYS-AG..> 20-Mar-2014 08:11 2.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Panasonic-Y3..> 20-Mar-2014 08:11 2.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Panasonic-EZ..> 20-Mar-2014 08:10 2.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ATMEL-8-bit-..> 19-Mar-2014 18:04 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-USB1T11A-PDF..> 19-Mar-2014 18:03 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-OSLON-SSL-Ce..> 19-Mar-2014 18:03 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Atmel-ATmega..> 19-Mar-2014 18:03 2.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PBSS5160T-60..> 19-Mar-2014 18:03 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MICROCHIP-PI..> 19-Mar-2014 18:02 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Ed.081002-DA..> 19-Mar-2014 18:02 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Instructions..> 19-Mar-2014 18:01 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Serie-PicoSc..> 19-Mar-2014 18:01 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-F42202-PDF.htm 19-Mar-2014 18:00 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-propose-plus..> 11-Mar-2014 08:19 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Haute-vitess..> 11-Mar-2014 08:17 2.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Controle-de-..> 11-Mar-2014 08:16 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-NXP-TEA1703T..> 11-Mar-2014 08:15 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-XPS-MC16-XPS..> 11-Mar-2014 08:15 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MC21605-PDF.htm 11-Mar-2014 08:14 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-WetTantalum-..> 11-Mar-2014 08:14 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ES2333-PDF.htm 11-Mar-2014 08:14 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-SB175-Connec..> 11-Mar-2014 08:14 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Cannon-ZD-PD..> 11-Mar-2014 08:13 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-YAGEO-DATA-S..> 11-Mar-2014 08:13 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ATMEL-8-bit-..> 11-Mar-2014 07:55 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-NXP-PCA9555 ..> 11-Mar-2014 07:54 2.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MICREL-KSZ88..> 11-Mar-2014 07:54 2.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Microship-PI..> 11-Mar-2014 07:53 2.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-EPCOS-Sample..> 11-Mar-2014 07:53 2.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-NXP-BT136-60..> 11-Mar-2014 07:52 2.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-NTE_SEMICOND..> 11-Mar-2014 07:52 2.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-L-efficacite..> 11-Mar-2014 07:52 2.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LUXEON-Guide..> 11-Mar-2014 07:52 2.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Realiser-un-..> 11-Mar-2014 07:51 2.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-SOT-23-Multi..> 11-Mar-2014 07:51 2.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ZigBee-ou-le..> 11-Mar-2014 07:50 2.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Les-derniers..> 11-Mar-2014 07:50 2.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Conception-d..> 11-Mar-2014 07:49 2.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Puissance-ut..> 11-Mar-2014 07:49 2.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MOLEX-43160-..> 10-Mar-2014 17:21 1.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MOLEX-87439-..> 10-Mar-2014 17:21 1.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MOLEX-43020-..> 10-Mar-2014 17:21 1.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-NXP-PBSS9110..> 10-Mar-2014 17:21 1.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TEKTRONIX-DP..> 10-Mar-2014 17:20 2.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-uC-OS-III-Br..> 10-Mar-2014 17:20 2.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-CIRRUS-LOGIC..> 10-Mar-2014 17:20 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-NXP-PSMN7R0-..> 10-Mar-2014 17:19 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MOLEX-39-00-..> 10-Mar-2014 17:19 1.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-manual-bus-p..> 10-Mar-2014 16:29 1.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Molex-Crimp-..> 10-Mar-2014 16:27 1.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-The-essentia..> 10-Mar-2014 16:27 1.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-OMRON-Master..> 10-Mar-2014 16:26 1.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Proskit-SS-3..> 10-Mar-2014 16:26 1.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-BYV79E-serie..> 10-Mar-2014 16:19 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-NXP-74VHC126..> 10-Mar-2014 16:17 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-NXP-PSMN1R7-..> 10-Mar-2014 16:17 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-FICHE-DE-DON..> 10-Mar-2014 16:17 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-HUNTSMAN-Adv..> 10-Mar-2014 16:17 1.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-NXP-PMBFJ620..> 10-Mar-2014 16:16 1.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Pico-Spox-Wi..> 10-Mar-2014 16:16 1.7M

2-electrode arrester

Series/Type: EF800X

Ordering code: B88069X2641xxxx a)

Version/Date: Issue 03 / 2008-01-18

Version: 6

Content of header bars 1 and 2 of data sheet will be automatically entered in headers and footers! Please fill in the

table and then change the color to "white" (or invisible). This ensures that the table disappears for the customer

PDF. To update the data sheet, click on the symbol "Preview" and then "Close". Please do not alter the header or

footer when copying the content.

Identification/Classification 1:

(header 1 + top left header bar)

Surge arrester

Identification/Classification 2:

(header 2 + bottom left header bar)

2-electrode arrester

Ordering code:

(top right header bar)

B88069X2641xxxx a)

Series/Type:

(top right header bar)

EF800X

Preliminary data (optional):

(if necessary)

Department: KB AB E / KB AB PM

Date: Issue 03 / 2008-01-18

© EPCOS AG 2008. Reproduction, publication and dissemination of this document, enclosures hereto and the information

contained therein without EPCOS' prior express consent is prohibited. Surge arrester B88069X2641xxxx a)

2-electrode arrester EF800X

KB AB E / KB AB PM Issue 03 / 2008-01-18

Please read Cautions and warnings and Page 2 of 4

Important notes at the end of this document.

Features Applications

Standard size

High follow current capability

Very fast response time

Stable performance over life

Very low capacitance

High insulation resistance

RoHS-compatible

Application with high follow current

Power supply

Electrical specifications

DC spark-over voltage 1) 2) 680 ... 1000 V

Impulse spark-over voltage

at 100 V/µs - for 99 % of measured values

- typical values of distribution

at 1 kV/µs - for 99 % of measured values

- typical values of distribution

< 1200

< 1000

< 1300

< 1100

V

V

V

V

Service life

10 operations 50 Hz, 1 s 5 A

1 operation 50 Hz, 0.18 s (9 cycles) 65 A

10 operations 8/20 µs 5 kA

1 operation 8/20 µs 10 kA

Max. follow current during one voltage half cycle at 50 Hz 200 A

Insulation resistance at 100 Vdc > 10 GΩ

Capacitance at 1 MHz < 1.5 pF

Arc voltage at 1 A

Glow to arc transition current

Glow voltage

~ 22

< 0.5

~ 140

V

A

V

Weight ~ 1.5 g

Operation and storage temperature -40 ... +90 °C

Climatic category (IEC 60068-1) 40/ 90/ 21

Marking, red positive EF 800 YY O

EF - Series

800 - Nominal voltage

YY - Year of production

O - Non radioactive

a) xxxx = S102 (100 pcs on 5 stripes)

= T502 (500 pcs on tape and reel)

1) At delivery AQL 0.65 level II, DIN ISO 2859

2) In ionized mode

Terms in accordance with ITU-T Rec. K.12 and DIN 57845/VDE0845 Surge arrester B88069X2641xxxx a)

2-electrode arrester EF800X

KB AB E / KB AB PM Issue 03 / 2008-01-18

Please read Cautions and warnings and Page 3 of 4

Important notes at the end of this document.

Dimensional drawing

Cautions and warnings

Surge arrester must be selected so that the maximum expected follow current can be quenched.

The follow current must be limited so that the arrester can be properly extinguished when the

surge has decayed. The arrester might otherwise heat up and ignite adjacent components.

Surge arresters must not be operated directly in power supply networks.

Surge arresters may become hot in case of longer periods of current stress (danger of burning).

Surge arresters may be used only within their specified values. In case of overload, the head

contacts may fail or the component may be destroyed.

Damaged surge arresters must not be re-used.

Not to scale

Dimensions in mm

Non controlled document Important notes

Page 4 of 4

The following applies to all products named in this publication:

1. Some parts of this publication contain statements about the suitability of our products for

certain areas of application. These statements are based on our knowledge of typical

requirements that are often placed on our products in the areas of application concerned. We

nevertheless expressly point out that such statements cannot be regarded as binding

statements about the suitability of our products for a particular customer application. As a

rule, EPCOS is either unfamiliar with individual customer applications or less familiar with them

than the customers themselves. For these reasons, it is always ultimately incumbent on the

customer to check and decide whether an EPCOS product with the properties described in the

product specification is suitable for use in a particular customer application.

2. We also point out that in individual cases, a malfunction of passive electronic components

or failure before the end of their usual service life cannot be completely ruled out in the

current state of the art, even if they are operated as specified. In customer applications

requiring a very high level of operational safety and especially in customer applications in which

the malfunction or failure of a passive electronic component could endanger human life or health

(e.g. in accident prevention or life-saving systems), it must therefore be ensured by means of

suitable design of the customer application or other action taken by the customer (e.g. installation

of protective circuitry or redundancy) that no injury or damage is sustained by third parties in the

event of malfunction or failure of a passive electronic component.

3. The warnings, cautions and product-specific notes must be observed.

4. In order to satisfy certain technical requirements, some of the products described in this

publication may contain substances subject to restrictions in certain jurisdictions (e.g.

because they are classed as hazardous). Useful information on this will be found in our Material

Data Sheets on the Internet (www.epcos.com/material). Should you have any more detailed

questions, please contact our sales offices.

5. We constantly strive to improve our products. Consequently, the products described in this

publication may change from time to time. The same is true of the corresponding product

specifications. Please check therefore to what extent product descriptions and specifications

contained in this publication are still applicable before or when you place an order.

We also reserve the right to discontinue production and delivery of products. Consequently,

we cannot guarantee that all products named in this publication will always be available.