Consent Manager Tag v2.0 (for TCF 2.0) -->

Farnell PDF

ACC Silicones LTD AS1803 - Farnell - Farnell - Farnell Element 14

ACC Silicones LTD AS1803 - Farnell - Farnell - Farnell Element 14

ACC Silicones LTD AS1803 - Farnell - Farnell - Farnell Element 14

- Revenir à l'accueil

Farnell Element 14 :

See the trailer for the next exciting episode of The Ben Heck show. Check back on Friday to be among the first to see the exclusive full show on element…

Connect your Raspberry Pi to a breadboard, download some code and create a push-button audio play project.

Puce électronique / Microchip :

Sans fil - Wireless :

Texas instrument :

Ordinateurs :

Logiciels :

Tutoriels :

Autres documentations :

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-0430300011-D..> 14-Jun-2014 18:13 2.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-06-6544-8-PD..> 26-Mar-2014 17:56 2.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-3M-Polyimide..> 21-Mar-2014 08:09 3.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-3M-VolitionT..> 25-Mar-2014 08:18 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-10BQ060-PDF.htm 14-Jun-2014 09:50 2.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-10TPB47M-End..> 14-Jun-2014 18:16 3.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-12mm-Size-In..> 14-Jun-2014 09:50 2.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-24AA024-24LC..> 23-Jun-2014 10:26 3.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-50A-High-Pow..> 20-Mar-2014 17:31 2.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-1907-2006-PD..> 26-Mar-2014 17:56 2.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-5910-PDF.htm 25-Mar-2014 08:15 3.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-6517b-Electr..> 29-Mar-2014 11:12 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-A-True-Syste..> 29-Mar-2014 11:13 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-AD524-PDF.htm 20-Mar-2014 17:33 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ADL6507-PDF.htm 14-Jun-2014 18:19 3.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ADSP-21362-A..> 20-Mar-2014 17:34 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ALF1225-12-V..> 01-Apr-2014 07:40 3.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ALF2412-24-V..> 01-Apr-2014 07:39 3.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-AN10361-Phil..> 23-Jun-2014 10:29 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ARADUR-HY-13..> 26-Mar-2014 17:55 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ARALDITE-201..> 21-Mar-2014 08:12 3.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ARALDITE-CW-..> 26-Mar-2014 17:56 2.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ATMEL-8-bit-..> 19-Mar-2014 18:04 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ATMEL-8-bit-..> 11-Mar-2014 07:55 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ATmega640-VA..> 14-Jun-2014 09:49 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ATtiny20-PDF..> 25-Mar-2014 08:19 3.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ATtiny26-L-A..> 13-Jun-2014 18:40 1.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Alimentation..> 14-Jun-2014 18:24 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Alimentation..> 01-Apr-2014 07:42 3.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Amplificateu..> 29-Mar-2014 11:11 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-An-Improved-..> 14-Jun-2014 09:49 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Atmel-ATmega..> 19-Mar-2014 18:03 2.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Avvertenze-e..> 14-Jun-2014 18:20 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-BC846DS-NXP-..> 13-Jun-2014 18:42 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-BC847DS-NXP-..> 23-Jun-2014 10:24 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-BF545A-BF545..> 23-Jun-2014 10:28 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-BK2650A-BK26..> 29-Mar-2014 11:10 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-BT151-650R-N..> 13-Jun-2014 18:40 1.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-BTA204-800C-..> 13-Jun-2014 18:42 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-BUJD203AX-NX..> 13-Jun-2014 18:41 1.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-BYV29F-600-N..> 13-Jun-2014 18:42 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-BYV79E-serie..> 10-Mar-2014 16:19 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-BZX384-serie..> 23-Jun-2014 10:29 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Battery-GBA-..> 14-Jun-2014 18:13 2.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-C.A-6150-C.A..> 14-Jun-2014 18:24 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-C.A 8332B-C...> 01-Apr-2014 07:40 3.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-CC2560-Bluet..> 29-Mar-2014 11:14 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-CD4536B-Type..> 14-Jun-2014 18:13 2.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-CIRRUS-LOGIC..> 10-Mar-2014 17:20 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-CS5532-34-BS..> 01-Apr-2014 07:39 3.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Cannon-ZD-PD..> 11-Mar-2014 08:13 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Ceramic-tran..> 14-Jun-2014 18:19 3.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Circuit-Note..> 26-Mar-2014 18:00 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Circuit-Note..> 26-Mar-2014 18:00 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Cles-electro..> 21-Mar-2014 08:13 3.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Conception-d..> 11-Mar-2014 07:49 2.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Connectors-N..> 14-Jun-2014 18:12 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Construction..> 14-Jun-2014 18:25 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Controle-de-..> 11-Mar-2014 08:16 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Cordless-dri..> 14-Jun-2014 18:13 2.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Current-Tran..> 26-Mar-2014 17:58 2.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Current-Tran..> 26-Mar-2014 17:58 2.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Current-Tran..> 26-Mar-2014 17:59 2.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Current-Tran..> 26-Mar-2014 17:59 2.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-DC-Fan-type-..> 14-Jun-2014 09:48 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-DC-Fan-type-..> 14-Jun-2014 09:51 1.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Davum-TMC-PD..> 14-Jun-2014 18:27 2.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-De-la-puissa..> 29-Mar-2014 11:10 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Directive-re..> 25-Mar-2014 08:16 3.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Documentatio..> 14-Jun-2014 18:26 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Download-dat..> 13-Jun-2014 18:40 1.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ECO-Series-T..> 20-Mar-2014 08:14 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ELMA-PDF.htm 29-Mar-2014 11:13 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-EMC1182-PDF.htm 25-Mar-2014 08:17 3.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-EPCOS-173438..> 23-Jun-2014 10:24 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-EPCOS-Sample..> 11-Mar-2014 07:53 2.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ES2333-PDF.htm 11-Mar-2014 08:14 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Ed.081002-DA..> 19-Mar-2014 18:02 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-F28069-Picco..> 14-Jun-2014 18:14 2.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-F42202-PDF.htm 19-Mar-2014 18:00 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-FDS-ITW-Spra..> 14-Jun-2014 18:22 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-FICHE-DE-DON..> 10-Mar-2014 16:17 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Fastrack-Sup..> 23-Jun-2014 10:25 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Ferric-Chlor..> 29-Mar-2014 11:14 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Fiche-de-don..> 14-Jun-2014 09:47 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Fiche-de-don..> 14-Jun-2014 18:26 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Fluke-1730-E..> 14-Jun-2014 18:23 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-GALVA-A-FROI..> 26-Mar-2014 17:56 2.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-GALVA-MAT-Re..> 26-Mar-2014 17:57 2.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-GN-RELAYS-AG..> 20-Mar-2014 08:11 2.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-HC49-4H-Crys..> 14-Jun-2014 18:20 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-HFE1600-Data..> 14-Jun-2014 18:22 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-HI-70300-Sol..> 14-Jun-2014 18:27 2.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-HUNTSMAN-Adv..> 10-Mar-2014 16:17 1.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Haute-vitess..> 11-Mar-2014 08:17 2.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-IP4252CZ16-8..> 13-Jun-2014 18:41 1.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Instructions..> 19-Mar-2014 18:01 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-KSZ8851SNL-S..> 23-Jun-2014 10:28 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-L-efficacite..> 11-Mar-2014 07:52 2.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LCW-CQ7P.CC-..> 25-Mar-2014 08:19 3.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LME49725-Pow..> 14-Jun-2014 09:49 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LOCTITE-542-..> 25-Mar-2014 08:15 3.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LOCTITE-3463..> 25-Mar-2014 08:19 3.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-LUXEON-Guide..> 11-Mar-2014 07:52 2.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Leaded-Trans..> 23-Jun-2014 10:26 3.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Les-derniers..> 11-Mar-2014 07:50 2.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Loctite3455-..> 25-Mar-2014 08:16 3.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Low-cost-Enc..> 13-Jun-2014 18:42 1.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Lubrifiant-a..> 26-Mar-2014 18:00 2.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MC3510-PDF.htm 25-Mar-2014 08:17 3.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MC21605-PDF.htm 11-Mar-2014 08:14 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MCF532x-7x-E..> 29-Mar-2014 11:14 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MICREL-KSZ88..> 11-Mar-2014 07:54 2.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MICROCHIP-PI..> 19-Mar-2014 18:02 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MOLEX-39-00-..> 10-Mar-2014 17:19 1.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MOLEX-43020-..> 10-Mar-2014 17:21 1.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MOLEX-43160-..> 10-Mar-2014 17:21 1.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MOLEX-87439-..> 10-Mar-2014 17:21 1.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MPXV7002-Rev..> 20-Mar-2014 17:33 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-MX670-MX675-..> 14-Jun-2014 09:46 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Microchip-MC..> 13-Jun-2014 18:27 1.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Microship-PI..> 11-Mar-2014 07:53 2.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Midas-Active..> 14-Jun-2014 18:17 3.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Midas-MCCOG4..> 14-Jun-2014 18:11 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Miniature-Ci..> 26-Mar-2014 17:55 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Mistral-PDF.htm 14-Jun-2014 18:12 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Molex-83421-..> 14-Jun-2014 18:17 3.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Molex-COMMER..> 14-Jun-2014 18:16 3.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Molex-Crimp-..> 10-Mar-2014 16:27 1.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Multi-Functi..> 20-Mar-2014 17:38 3.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-NTE_SEMICOND..> 11-Mar-2014 07:52 2.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-NXP-74VHC126..> 10-Mar-2014 16:17 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-NXP-BT136-60..> 11-Mar-2014 07:52 2.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-NXP-PBSS9110..> 10-Mar-2014 17:21 1.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-NXP-PCA9555 ..> 11-Mar-2014 07:54 2.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-NXP-PMBFJ620..> 10-Mar-2014 16:16 1.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-NXP-PSMN1R7-..> 10-Mar-2014 16:17 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-NXP-PSMN7R0-..> 10-Mar-2014 17:19 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-NXP-TEA1703T..> 11-Mar-2014 08:15 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Nilï¬-sk-E-..> 14-Jun-2014 09:47 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Novembre-201..> 20-Mar-2014 17:38 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-OMRON-Master..> 10-Mar-2014 16:26 1.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-OSLON-SSL-Ce..> 19-Mar-2014 18:03 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-OXPCIE958-FB..> 13-Jun-2014 18:40 1.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PBSS5160T-60..> 19-Mar-2014 18:03 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PDTA143X-ser..> 20-Mar-2014 08:12 2.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PDTB123TT-NX..> 13-Jun-2014 18:43 1.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PESD5V0F1BL-..> 13-Jun-2014 18:43 1.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PESD9X5.0L-P..> 13-Jun-2014 18:43 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PIC18F2455-2..> 23-Jun-2014 10:27 3.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PIC24FJ256GB..> 14-Jun-2014 09:51 2.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PMBT3906-PNP..> 13-Jun-2014 18:44 1.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PMBT4403-PNP..> 23-Jun-2014 10:27 3.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PMEG4002EL-N..> 14-Jun-2014 18:18 3.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-PMEG4010CEH-..> 13-Jun-2014 18:43 1.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Panasonic-15..> 23-Jun-2014 10:29 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Panasonic-EC..> 20-Mar-2014 17:36 2.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Panasonic-EZ..> 20-Mar-2014 08:10 2.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Panasonic-Id..> 20-Mar-2014 17:35 2.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Panasonic-Ne..> 20-Mar-2014 17:36 2.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Panasonic-Ra..> 20-Mar-2014 17:37 2.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Panasonic-TS..> 20-Mar-2014 08:12 2.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Panasonic-Y3..> 20-Mar-2014 08:11 2.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Pico-Spox-Wi..> 10-Mar-2014 16:16 1.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Pompes-Charg..> 24-Apr-2014 20:23 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Ponts-RLC-po..> 14-Jun-2014 18:23 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Portable-Ana..> 29-Mar-2014 11:16 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Premier-Farn..> 21-Mar-2014 08:11 3.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Produit-3430..> 14-Jun-2014 09:48 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Proskit-SS-3..> 10-Mar-2014 16:26 1.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Puissance-ut..> 11-Mar-2014 07:49 2.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Q48-PDF.htm 23-Jun-2014 10:29 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Radial-Lead-..> 20-Mar-2014 08:12 2.6M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Realiser-un-..> 11-Mar-2014 07:51 2.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Reglement-RE..> 21-Mar-2014 08:08 3.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Repartiteurs..> 14-Jun-2014 18:26 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-S-TRI-SWT860..> 21-Mar-2014 08:11 3.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-SB175-Connec..> 11-Mar-2014 08:14 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-SMBJ-Transil..> 29-Mar-2014 11:12 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-SOT-23-Multi..> 11-Mar-2014 07:51 2.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-SPLC780A1-16..> 14-Jun-2014 18:25 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-SSC7102-Micr..> 23-Jun-2014 10:25 3.2M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-SVPE-series-..> 14-Jun-2014 18:15 2.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Septembre-20..> 20-Mar-2014 17:46 3.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Serie-PicoSc..> 19-Mar-2014 18:01 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Serie-Standa..> 14-Jun-2014 18:23 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Series-2600B..> 20-Mar-2014 17:30 3.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Signal-PCB-R..> 14-Jun-2014 18:11 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Strangkuhlko..> 21-Mar-2014 08:09 3.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Supercapacit..> 26-Mar-2014 17:57 2.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TDK-Lambda-H..> 14-Jun-2014 18:21 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-TEKTRONIX-DP..> 10-Mar-2014 17:20 2.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Tektronix-AC..> 13-Jun-2014 18:44 1.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Telemetres-l..> 20-Mar-2014 17:46 3.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-Termometros-..> 14-Jun-2014 18:14 2.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-The-essentia..> 10-Mar-2014 16:27 1.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-U2270B-PDF.htm 14-Jun-2014 18:15 3.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-USB-Buccanee..> 14-Jun-2014 09:48 2.5M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-USB1T11A-PDF..> 19-Mar-2014 18:03 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-V4N-PDF.htm 14-Jun-2014 18:11 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-WetTantalum-..> 11-Mar-2014 08:14 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-XPS-AC-Octop..> 14-Jun-2014 18:11 2.1M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-XPS-MC16-XPS..> 11-Mar-2014 08:15 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-YAGEO-DATA-S..> 11-Mar-2014 08:13 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ZigBee-ou-le..> 11-Mar-2014 07:50 2.4M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-celpac-SUL84..> 21-Mar-2014 08:11 3.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-china_rohs_o..> 21-Mar-2014 10:04 3.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-cree-Xlamp-X..> 20-Mar-2014 17:34 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-cree-Xlamp-X..> 20-Mar-2014 17:35 2.7M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-cree-Xlamp-X..> 20-Mar-2014 17:31 2.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-cree-Xlamp-m..> 20-Mar-2014 17:32 2.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-cree-Xlamp-m..> 20-Mar-2014 17:32 2.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-ir1150s_fr.p..> 29-Mar-2014 11:11 3.3M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-manual-bus-p..> 10-Mar-2014 16:29 1.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-propose-plus..> 11-Mar-2014 08:19 2.8M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-techfirst_se..> 21-Mar-2014 08:08 3.9M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-testo-205-20..> 20-Mar-2014 17:37 3.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-testo-470-Fo..> 20-Mar-2014 17:38 3.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Farnell-uC-OS-III-Br..> 10-Mar-2014 17:20 2.0M

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Sefram-7866HD.pdf-PD..> 29-Mar-2014 11:46 472K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Sefram-CAT_ENREGISTR..> 29-Mar-2014 11:46 461K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Sefram-CAT_MESUREURS..> 29-Mar-2014 11:46 435K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Sefram-GUIDE_SIMPLIF..> 29-Mar-2014 11:46 481K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Sefram-GUIDE_SIMPLIF..> 29-Mar-2014 11:46 442K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif)

Sefram-GUIDE_SIMPLIF..> 29-Mar-2014 11:46 422K

![[TXT]](http://www.audentia-gestion.fr/icons/text.gif) Sefram-SP270.pdf-PDF..> 29-Mar-2014 11:46 464K

Sefram-SP270.pdf-PDF..> 29-Mar-2014 11:46 464K

http://www.farnell.com/datasheets/43798.pdf

http://www.farnell.com/datasheets/43798.pdf

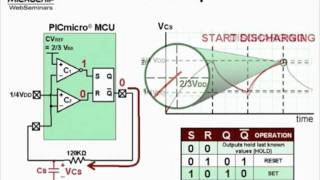

2010 Microchip Technology Inc. DS41302D

PIC12F609/615/617

PIC12HV609/615

Data Sheet

8-Pin, Flash-Based 8-Bit

CMOS Microcontrollers

*8-bit, 8-pin Devices Protected by Microchip’s Low Pin Count Patent: U.S. Patent No. 5,847,450. Additional U.S. and

foreign patents and applications may be issued or pending.

DS41302D-page 2 2010 Microchip Technology Inc.

Information contained in this publication regarding device

applications and the like is provided only for your convenience

and may be superseded by updates. It is your responsibility to

ensure that your application meets with your specifications.

MICROCHIP MAKES NO REPRESENTATIONS OR

WARRANTIES OF ANY KIND WHETHER EXPRESS OR

IMPLIED, WRITTEN OR ORAL, STATUTORY OR

OTHERWISE, RELATED TO THE INFORMATION,

INCLUDING BUT NOT LIMITED TO ITS CONDITION,

QUALITY, PERFORMANCE, MERCHANTABILITY OR

FITNESS FOR PURPOSE. Microchip disclaims all liability

arising from this information and its use. Use of Microchip

devices in life support and/or safety applications is entirely at

the buyer’s risk, and the buyer agrees to defend, indemnify and

hold harmless Microchip from any and all damages, claims,

suits, or expenses resulting from such use. No licenses are

conveyed, implicitly or otherwise, under any Microchip

intellectual property rights.

Trademarks

The Microchip name and logo, the Microchip logo, dsPIC,

KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART,

rfPIC and UNI/O are registered trademarks of Microchip

Technology Incorporated in the U.S.A. and other countries.

FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor,

MXDEV, MXLAB, SEEVAL and The Embedded Control

Solutions Company are registered trademarks of Microchip

Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, CodeGuard,

dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN,

ECONOMONITOR, FanSense, HI-TIDE, In-Circuit Serial

Programming, ICSP, Mindi, MiWi, MPASM, MPLAB Certified

logo, MPLIB, MPLINK, mTouch, Octopus, Omniscient Code

Generation, PICC, PICC-18, PICDEM, PICDEM.net, PICkit,

PICtail, PIC32 logo, REAL ICE, rfLAB, Select Mode, Total

Endurance, TSHARC, UniWinDriver, WiperLock and ZENA

are trademarks of Microchip Technology Incorporated in the

U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated

in the U.S.A.

All other trademarks mentioned herein are property of their

respective companies.

© 2010, Microchip Technology Incorporated, Printed in the

U.S.A., All Rights Reserved.

Printed on recycled paper.

Note the following details of the code protection feature on Microchip devices:

• Microchip products meet the specification contained in their particular Microchip Data Sheet.

• Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the

intended manner and under normal conditions.

• There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our

knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip’s Data

Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

• Microchip is willing to work with the customer who is concerned about the integrity of their code.

• Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not

mean that we are guaranteeing the product as “unbreakable.”

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our

products. Attempts to break Microchip’s code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts

allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Microchip received ISO/TS-16949:2002 certification for its worldwide

headquarters, design and wafer fabrication facilities in Chandler and

Tempe, Arizona; Gresham, Oregon and design centers in California

and India. The Company’s quality system processes and procedures

are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping

devices, Serial EEPROMs, microperipherals, nonvolatile memory and

analog products. In addition, Microchip’s quality system for the design

and manufacture of development systems is ISO 9001:2000 certified.

2010 Microchip Technology Inc. DS41302D-page 3

PIC12F609/615/617/12HV609/615

High-Performance RISC CPU:

• Only 35 Instructions to Learn:

- All single-cycle instructions except branches

• Operating Speed:

- DC – 20 MHz oscillator/clock input

- DC – 200 ns instruction cycle

• Interrupt Capability

• 8-Level Deep Hardware Stack

• Direct, Indirect and Relative Addressing modes

Special Microcontroller Features:

• Precision Internal Oscillator:

- Factory calibrated to ±1%, typical

- Software selectable frequency: 4 MHz or

8 MHz

• Power-Saving Sleep mode

• Voltage Range:

- PIC12F609/615/617: 2.0V to 5.5V

- PIC12HV609/615: 2.0V to user defined

maximum (see note)

• Industrial and Extended Temperature Range

• Power-on Reset (POR)

• Power-up Timer (PWRT) and Oscillator Start-up

Timer (OST)

• Brown-out Reset (BOR)

• Watchdog Timer (WDT) with independent

Oscillator for Reliable Operation

• Multiplexed Master Clear with Pull-up/Input Pin

• Programmable Code Protection

• High Endurance Flash:

- 100,000 write Flash endurance

- Flash retention: > 40 years

• Self Read/ Write Program Memory (PIC12F617

only)

Low-Power Features:

• Standby Current:

- 50 nA @ 2.0V, typical

• Operating Current:

- 11A @ 32 kHz, 2.0V, typical

- 260A @ 4 MHz, 2.0V, typical

• Watchdog Timer Current:

- 1A @ 2.0V, typical

Note: Voltage across the shunt regulator should

not exceed 5V.

Peripheral Features:

• Shunt Voltage Regulator (PIC12HV609/615 only):

- 5 volt regulation

- 4 mA to 50 mA shunt range

• 5 I/O Pins and 1 Input Only

• High Current Source/Sink for Direct LED Drive

- Interrupt-on-pin change or pins

- Individually programmable weak pull-ups

• Analog Comparator module with:

- One analog comparator

- Programmable on-chip voltage reference

(CVREF) module (% of VDD)

- Comparator inputs and output externally

accessible

- Built-In Hysteresis (software selectable)

• Timer0: 8-Bit Timer/Counter with 8-Bit

Programmable Prescaler

• Enhanced Timer1:

- 16-bit timer/counter with prescaler

- External Timer1 Gate (count enable)

- Option to use OSC1 and OSC2 in LP mode

as Timer1 oscillator if INTOSC mode

selected

- Option to use system clock as Timer1

• In-Circuit Serial ProgrammingTM (ICSPTM) via Two

Pins

PIC12F615/617/HV615 ONLY:

• Enhanced Capture, Compare, PWM module:

- 16-bit Capture, max. resolution 12.5 ns

- Compare, max. resolution 200 ns

- 10-bit PWM with 1 or 2 output channels, 1

output channel programmable “dead time,”

max. frequency 20 kHz, auto-shutdown

• A/D Converter:

- 10-bit resolution and 4 channels, samples

internal voltage references

• Timer2: 8-Bit Timer/Counter with 8-Bit Period

Register, Prescaler and Postscaler

8-Pin Flash-Based, 8-Bit CMOS Microcontrollers

PIC12F609/615/617/12HV609/615

DS41302D-page 4 2010 Microchip Technology Inc.

8-Pin Diagram, PIC12F609/HV609 (PDIP, SOIC, MSOP, DFN)

TABLE 1: PIC12F609/HV609 PIN SUMMARY (PDIP, SOIC, MSOP, DFN)

Device

Program

Memory Data Memory

Self Read/

Self Write I/O 10-bit A/D

(ch) Comparators ECCP Timers

8/16-bit Voltage Range

Flash

(words) SRAM (bytes)

PIC12F609 1024 64 — 5 0 1 — 1/1 2.0V-5.5V

PIC12HV609 1024 64 — 5 0 1 — 1/1 2.0V-user defined

PIC12F615 1024 64 — 5 4 1 YES 2/1 2.0V-5.5V

PIC12HV615 1024 64 — 5 4 1 YES 2/1 2.0V-user defined

PIC12F617 2048 128 YES 5 4 1 YES 2/1 2.0V-5.5V

I/O Pin Comparators Timer Interrupts Pull-ups Basic

GP0 7 CIN+ — IOC Y ICSPDAT

GP1 6 CIN0- — IOC Y ICSPCLK

GP2 5 COUT T0CKI INT/IOC Y —

GP3(1) 4 — — IOC Y(2) MCLR/VPP

GP4 3 CIN1- T1G IOC Y OSC2/CLKOUT

GP5 2 — T1CKI IOC Y OSC1/CLKIN

— 1 — — — — VDD

— 8 — — — — VSS

Note 1: Input only.

2: Only when pin is configured for external MCLR.

1

2

3

4 5

6

7

8

PIC12F609/

HV609

VSS

GP0/CIN+/ICSPDAT

GP1/CIN0-/ICSPCLK

GP2/T0CKI/INT/COUT

VDD

GP5/T1CKI/OSC1/CLKIN

GP4/CIN1-/T1G/OSC2/CLKOUT

GP3/MCLR/VPP

2010 Microchip Technology Inc. DS41302D-page 5

PIC12F609/615/617/12HV609/615

8-Pin Diagram, PIC12F615/617/HV615 (PDIP, SOIC, MSOP, DFN)

TABLE 2: PIC12F615/617/HV615 PIN SUMMARY (PDIP, SOIC, MSOP, DFN)

I/O Pin Analog Comparator

s Timer CCP Interrupts Pull-ups Basic

GP0 7 AN0 CIN+ — P1B IOC Y ICSPDAT

GP1 6 AN1 CIN0- — — IOC Y ICSPCLK/VREF

GP2 5 AN2 COUT T0CKI CCP1/P1A INT/IOC Y —

GP3(1) 4 — — T1G* — IOC Y(2) MCLR/VPP

GP4 3 AN3 CIN1- T1G P1B* IOC Y OSC2/CLKOUT

GP5 2 — — T1CKI P1A* IOC Y OSC1/CLKIN

— 1 — — — — — — VDD

— 8 — — — — — — VSS

* Alternate pin function.

Note 1: Input only.

2: Only when pin is configured for external MCLR.

1

2

3

4 5

6

7

8

PIC12F615/

617/HV615

VSS

GP0/AN0/CIN+/P1B/ICSPDAT

GP1/AN1/CIN0-/VREF/ICSPCLK

GP2/AN2/T0CKI/INT/COUT/CCP1/P1A

VDD

GP5/T1CKI/P1A*/OSC1/CLKIN

GP4/AN3/CIN1-/T1G/P1B*/OSC2/CLKOUT

GP3/T1G*/MCLR/VPP

* Alternate pin function.

PIC12F609/615/617/12HV609/615

DS41302D-page 6 2010 Microchip Technology Inc.

Table of Contents

1.0 Device Overview ......................................................................................................................................................................... 7

2.0 Memory Organization ................................................................................................................................................................ 11

3.0 Flash Program Memory Self Read/Self Write Control (PIC12F617 only).................................................................................. 27

4.0 Oscillator Module ....................................................................................................................................................................... 37

5.0 I/O Port ...................................................................................................................................................................................... 43

6.0 Timer0 Module .......................................................................................................................................................................... 53

7.0 Timer1 Module with Gate Control .............................................................................................................................................. 57

8.0 Timer2 Module (PIC12F615/617/HV615 only) .......................................................................................................................... 65

9.0 Comparator Module ................................................................................................................................................................... 67

10.0 Analog-to-Digital Converter (ADC) Module (PIC12F615/617/HV615 only) ............................................................................... 79

11.0 Enhanced Capture/Compare/PWM (With Auto-Shutdown and Dead Band) Module (PIC12F615/617/HV615 only) ............... 89

12.0 Special Features of the CPU ................................................................................................................................................... 107

13.0 Voltage Regulator .................................................................................................................................................................... 127

14.0 Instruction Set Summary ........................................................................................................................................................ 129

15.0 Development Support ............................................................................................................................................................. 139

16.0 Electrical Specifications ........................................................................................................................................................... 143

17.0 DC and AC Characteristics Graphs and Tables ...................................................................................................................... 171

18.0 Packaging Information ............................................................................................................................................................ 195

Appendix A: Data Sheet Revision History ......................................................................................................................................... 203

Appendix B: Migrating from other PIC® Devices ............................................................................................................................... 203

Index ................................................................................................................................................................................................. 205

The Microchip Web Site .................................................................................................................................................................... 209

Customer Change Notification Service ............................................................................................................................................. 209

Customer Support ............................................................................................................................................................................. 209

Reader Response ............................................................................................................................................................................. 210

Product Identification System ............................................................................................................................................................ 211

Worldwide Sales and Service ........................................................................................................................................................... 212

TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip

products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and

enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via

E-mail at docerrors@microchip.com or fax the Reader Response Form in the back of this data sheet to (480) 792-4150. We

welcome your feedback.

Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page.

The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current

devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of

silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

• Microchip’s Worldwide Web site; http://www.microchip.com

• Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are

using.

Customer Notification System

Register on our web site at www.microchip.com to receive the most current information on all of our products.

2010 Microchip Technology Inc. DS41302D-page 7

PIC12F609/615/617/12HV609/615

1.0 DEVICE OVERVIEW

The PIC12F609/615/617/12HV609/615 devices are

covered by this data sheet. They are available in 8-pin

PDIP, SOIC, MSOP and DFN packages.

Block Diagrams and pinout descriptions of the devices

are as follows:

• PIC12F609/HV609 (Figure 1-1, Table 1-1)

• PIC12F615/617/HV615 (Figure 1-2, Table 1-2)

FIGURE 1-1: PIC12F609/HV609 BLOCK DIAGRAM

Flash

Program

Memory

13

Data Bus

8

Program 14

Bus

Instruction Reg

Program Counter

RAM

File

Registers

Direct Addr 7

RAM Addr 9

Addr MUX

Indirect

Addr

FSR Reg

STATUS Reg

MUX

ALU

W Reg

Instruction

Decode &

Control

Timing

Generation

OSC1/CLKIN

OSC2/CLKOUT

GPIO

8

8

8

3

8-Level Stack 64 Bytes

1K X 14

(13-Bit)

Power-up

Timer

Oscillator

Start-up Timer

Power-on

Reset

Watchdog

Timer

MCLR VSS

Brown-out

Reset

Timer0 Timer1

GP0

GP1

GP2

GP3

GP4

GP5

Analog Comparator

T0CKI

INT

T1CKI

Configuration

Internal

Oscillator

and Reference

T1G

VDD

Block

CIN+

CIN0-

CIN1-

COUT

Comparator Voltage Reference

Absolute Voltage Reference

Shunt Regulator

(PIC12HV609 only)

PIC12F609/615/617/12HV609/615

DS41302D-page 8 2010 Microchip Technology Inc.

FIGURE 1-2: PIC12F615/617/HV615 BLOCK DIAGRAM

Flash

Program

Memory

13

Data Bus

8

Program 14

Bus

Instruction Reg

Program Counter

RAM

File

Registers

Direct Addr 7

RAM Addr 9

Addr MUX

Indirect

Addr

FSR Reg

STATUS Reg

MUX

ALU

W Reg

Instruction

Decode &

Control

Timing

Generation

OSC1/CLKIN

OSC2/CLKOUT

GPIO

8

8

8

3

8-Level Stack 64 Bytes and

1K X 14

(13-Bit)

Power-up

Timer

Oscillator

Start-up Timer

Power-on

Reset

Watchdog

Timer

MCLR VSS

Brown-out

Reset

Timer0 Timer1

GP0

GP1

GP2

GP3

GP4

GP5

Analog Comparator

T0CKI

INT

T1CKI

Configuration

Internal

Oscillator

VREF

and Reference

T1G

VDD

Timer2

Block

Shunt Regulator

(PIC12HV615 only)

Analog-To-Digital Converter

AN0

AN1

AN2

AN3

CIN+

CIN0-

CIN1-

COUT

ECCP

CCP1/P1A

P1B

P1A*

P1B*

Comparator Voltage Reference

Absolute Voltage Reference

* Alternate pin function.

** For the PIC12F617 only.

T1G*

2K X 14**

and

128 Bytes**

2010 Microchip Technology Inc. DS41302D-page 9

PIC12F609/615/617/12HV609/615

TABLE 1-1: PIC12F609/HV609 PINOUT DESCRIPTION

Name Function Input

Type

Output

Type Description

GP0/CIN+/ICSPDAT GP0 TTL CMOS General purpose I/O with prog. pull-up and interrupt-on-change

CIN+ AN — Comparator non-inverting input

ICSPDAT ST CMOS Serial Programming Data I/O

GP1/CIN0-/ICSPCLK GP1 TTL CMOS General purpose I/O with prog. pull-up and interrupt-on-change

CIN0- AN — Comparator inverting input

ICSPCLK ST — Serial Programming Clock

GP2/T0CKI/INT/COUT GP2 ST CMOS General purpose I/O with prog. pull-up and interrupt-on-change

T0CKI ST — Timer0 clock input

INT ST — External Interrupt

COUT — CMOS Comparator output

GP3/MCLR/VPP GP3 TTL — General purpose input with interrupt-on-change

MCLR ST — Master Clear w/internal pull-up

VPP HV — Programming voltage

GP4/CIN1-/T1G/OSC2/

CLKOUT

GP4 TTL CMOS General purpose I/O with prog. pull-up and interrupt-on-change

CIN1- AN — Comparator inverting input

T1G ST — Timer1 gate (count enable)

OSC2 — XTAL Crystal/Resonator

CLKOUT — CMOS FOSC/4 output

GP5/T1CKI/OSC1/CLKIN GP5 TTL CMOS General purpose I/O with prog. pull-up and interrupt-on-change

T1CKI ST — Timer1 clock input

OSC1 XTAL — Crystal/Resonator

CLKIN ST — External clock input/RC oscillator connection

VDD VDD Power — Positive supply

VSS VSS Power — Ground reference

Legend: AN=Analog input or output CMOS= CMOS compatible input or output HV= High Voltage

ST=Schmitt Trigger input with CMOS levels TTL = TTL compatible input XTAL=Crystal

PIC12F609/615/617/12HV609/615

DS41302D-page 10 2010 Microchip Technology Inc.

TABLE 1-2: PIC12F615/617/HV615 PINOUT DESCRIPTION

Name Function Input

Type

Output

Type Description

GP0/AN0/CIN+/P1B/ICSPDAT GP0 TTL CMOS General purpose I/O with prog. pull-up and interrupt-onchange

AN0 AN — A/D Channel 0 input

CIN+ AN — Comparator non-inverting input

P1B — CMOS PWM output

ICSPDAT ST CMOS Serial Programming Data I/O

GP1/AN1/CIN0-/VREF/ICSPCLK GP1 TTL CMOS General purpose I/O with prog. pull-up and interrupt-onchange

AN1 AN — A/D Channel 1 input

CIN0- AN — Comparator inverting input

VREF AN — External Voltage Reference for A/D

ICSPCLK ST — Serial Programming Clock

GP2/AN2/T0CKI/INT/COUT/CCP1/

P1A

GP2 ST CMOS General purpose I/O with prog. pull-up and interrupt-onchange

AN2 AN — A/D Channel 2 input

T0CKI ST — Timer0 clock input

INT ST — External Interrupt

COUT — CMOS Comparator output

CCP1 ST CMOS Capture input/Compare input/PWM output

P1A — CMOS PWM output

GP3/T1G*/MCLR/VPP GP3 TTL — General purpose input with interrupt-on-change

T1G* ST — Timer1 gate (count enable), alternate pin

MCLR ST — Master Clear w/internal pull-up

VPP HV — Programming voltage

GP4/AN3/CIN1-/T1G/P1B*/OSC2/

CLKOUT

GP4 TTL CMOS General purpose I/O with prog. pull-up and interrupt-onchange

AN3 AN — A/D Channel 3 input

CIN1- AN — Comparator inverting input

T1G ST — Timer1 gate (count enable)

P1B* — CMOS PWM output, alternate pin

OSC2 — XTAL Crystal/Resonator

CLKOUT — CMOS FOSC/4 output

GP5/T1CKI/P1A*/OSC1/CLKIN GP5 TTL CMOS General purpose I/O with prog. pull-up and interrupt-onchange

T1CKI ST — Timer1 clock input

P1A* — CMOS PWM output, alternate pin

OSC1 XTAL — Crystal/Resonator

CLKIN ST — External clock input/RC oscillator connection

VDD VDD Power — Positive supply

VSS VSS Power — Ground reference

* Alternate pin function.

Legend: AN=Analog input or output CMOS=CMOS compatible input or output HV= High Voltage

ST=Schmitt Trigger input with CMOS levels TTL = TTL compatible input XTAL=Crystal

2010 Microchip Technology Inc. DS41302D-page 11

PIC12F609/615/617/12HV609/615

2.0 MEMORY ORGANIZATION

2.1 Program Memory Organization

The PIC12F609/615/617/12HV609/615 has a 13-bit

program counter capable of addressing an 8K x 14

program memory space. Only the first 1K x 14 (0000h-

03FFh) for the PIC12F609/615/12HV609/615 is

physically implemented. For the PIC12F617, the first

2K x 14 (0000h-07FFh) is physically implemented.

Accessing a location above these boundaries will

cause a wrap-around within the first 1K x 14 space for

PIC12F609/615/12HV609/615 devices, and within the

first 2K x 14 space for the PIC12F617 device. The

Reset vector is at 0000h and the interrupt vector is at

0004h (see Figure 2-1).

FIGURE 2-1: PROGRAM MEMORY MAP

AND STACK FOR THE

PIC12F609/615/12HV609/615

FIGURE 2-2: PROGRAM MEMORY MAP

AND STACK FOR THE

PIC12F617

2.2 Data Memory Organization

The data memory (see Figure 2-3) is partitioned into two

banks, which contain the General Purpose Registers

(GPR) and the Special Function Registers (SFR). The

Special Function Registers are located in the first 32

locations of each bank. Register locations 40h-7Fh in

Bank 0 are General Purpose Registers, implemented as

static RAM. For the PIC12F617, the register locations

20h-7Fh in Bank 0 and A0h-EFh in Bank 1 are general

purpose registers implemented as Static RAM. Register

locations F0h-FFh in Bank 1 point to addresses 70h-7Fh

in Bank 0. All other RAM is unimplemented and returns

‘0’ when read. The RP0 bit of the STATUS register is the

bank select bit.

RP0

0 Bank 0 is selected

1 Bank 1 is selected

PC<12:0>

13

0000h

0004h

0005h

03FFh

0400h

1FFFh

Stack Level 1

Stack Level 8

Reset Vector

Interrupt Vector

On-chip Program

Memory

CALL, RETURN

RETFIE, RETLW

Stack Level 2

Wraps to 0000h-03FFh

Note: The IRP and RP1 bits of the STATUS

register are reserved and should always be

maintained as ‘0’s.

PC<12:0>

13

0000h

0004h

0005h

07FFh

Stack Level 1

Stack Level 8

Reset Vector

Interrupt Vector

CALL, RETURN

RETFIE, RETLW

Stack Level 2

Page 0

On-Chip

Program

Memory

Wraps to 0000h-07FFh

0800h

1FFFh

PIC12F609/615/617/12HV609/615

DS41302D-page 12 2010 Microchip Technology Inc.

2.2.1 GENERAL PURPOSE REGISTER

FILE

The register file is organized as 64 x 8 in the

PIC12F609/615/12HV609/615, and as 128 x 8 in the

PIC12F617. Each register is accessed, either directly

or indirectly, through the File Select Register (FSR)

(see Section 2.4 “Indirect Addressing, INDF and

FSR Registers”).

2.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers are registers used by

the CPU and peripheral functions for controlling the

desired operation of the device (see Table 2-1). These

registers are static RAM.

The special registers can be classified into two sets:

core and peripheral. The Special Function Registers

associated with the “core” are described in this section.

Those related to the operation of the peripheral features

are described in the section of that peripheral feature.

FIGURE 2-3: DATA MEMORY MAP OF

THE PIC12F609/HV609

Indirect Addr.(1)

TMR0

PCL

STATUS

FSR

GPIO

PCLATH

INTCON

PIR1

TMR1L

TMR1H

00h

01h

02h

03h

04h

05h

06h

07h

08h

09h

0Ah

0Bh

0Ch

0Dh

0Eh

0Fh

10h

11h

12h

13h

14h

15h

16h

17h

18h

19h

1Ah

1Bh

1Ch

1Dh

1Eh

1Fh

20h

7Fh

Bank 0

Unimplemented data memory locations, read as ‘0’.

Note 1: Not a physical register.

General

File

Address

File

Address

WPU

IOC

Indirect Addr.(1)

OPTION_REG

PCL

STATUS

FSR

TRISIO

PCLATH

INTCON

PIE1

PCON

80h

81h

82h

83h

84h

85h

86h

87h

88h

89h

8Ah

8Bh

8Ch

8Dh

8Eh

8Fh

90h

91h

92h

93h

94h

95h

96h

97h

98h

99h

9Ah

9Bh

9Ch

9Dh

9Eh

9Fh

A0h

FFh

Bank 1

ANSEL

Accesses 70h-7Fh F0h

VRCON

CMCON0

OSCTUNE

40h

3Fh

CMCON1

EFh

T1CON

Purpose

Registers

64 Bytes

Accesses 70h-7Fh

6Fh

70h

2010 Microchip Technology Inc. DS41302D-page 13

PIC12F609/615/617/12HV609/615

FIGURE 2-4: DATA MEMORY MAP OF

THE PIC12F615/617/HV615

Indirect Addr.(1)

TMR0

PCL

STATUS

FSR

GPIO

PCLATH

INTCON

PIR1

TMR1L

TMR1H

T1CON

00h

01h

02h

03h

04h

05h

06h

07h

08h

09h

0Ah

0Bh

0Ch

0Dh

0Eh

0Fh

10h

11h

12h

13h

14h

15h

16h

17h

18h

19h

1Ah

1Bh

1Ch

1Dh

1Eh

1Fh

20h

7Fh

Bank 0

Unimplemented data memory locations, read as ‘0’.

Note 1: Not a physical register.

2: Used for the PIC12F617 only.

File

Address

File

Address

WPU

IOC

Indirect Addr.(1)

OPTION_REG

PCL

STATUS

FSR

TRISIO

PCLATH

INTCON

PIE1

PCON

80h

81h

82h

83h

84h

85h

86h

87h

88h

89h

8Ah

8Bh

8Ch

8Dh

8Eh

8Fh

90h

91h

92h

93h

94h

95h

96h

97h

98h

99h

9Ah

9Bh

9Ch

9Dh

9Eh

9Fh

A0h

FFh

Bank 1

ADRESH

ADCON0

ADRESL

ANSEL

Accesses 70h-7Fh F0h

TMR2

T2CON

CCPR1L

CCPR1H

CCP1CON

PWM1CON

ECCPAS

VRCON

CMCON0

OSCTUNE

PR2

40h

3Fh

CMCON1

EFh

APFCON

General

Purpose

Registers

64 Bytes

Accesses 70h-7Fh

6Fh

70h

PMCON1 (2)

PMCON2 (2)

PMADRL (2)

PMADRH (2)

PMDATL (2)

PMDATH (2)

General

Purpose

Registers

96 Bytes from

20h-7Fh(2) Unimplemented for

PIC12F615/HV615

General

Purpose

Registers

32 Bytes(2)

Unimplemented for

PIC12F615/HV615

BFh

C0h

PIC12F609/615/617/12HV609/615

DS41302D-page 14 2010 Microchip Technology Inc.

TABLE 2-1: PIC12F609/HV609 SPECIAL FUNCTION REGISTERS SUMMARY BANK 0

Addr Name Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 Value on

POR, BOR Page

Bank 0

00h INDF Addressing this location uses contents of FSR to address data memory (not a physical register) xxxx xxxx 25, 115

01h TMR0 Timer0 Module’s Register xxxx xxxx 53, 115

02h PCL Program Counter’s (PC) Least Significant Byte 0000 0000 25, 115

03h STATUS IRP(1) RP1(1) RP0 TO PD Z DC C 0001 1xxx 18, 115

04h FSR Indirect Data Memory Address Pointer xxxx xxxx 25, 115

05h GPIO — — GP5 GP4 GP3 GP2 GP1 GP0 --x0 x000 43, 115

06h — Unimplemented — —

07h — Unimplemented — —

08h — Unimplemented — —

09h — Unimplemented — —

0Ah PCLATH — — — Write Buffer for upper 5 bits of Program Counter ---0 0000 25, 115

0Bh INTCON GIE PEIE T0IE INTE GPIE T0IF INTF GPIF 0000 0000 20, 115

0Ch PIR1 — — — — CMIF — — TMR1IF ---- 0--0 22, 115

0Dh — Unimplemented — —

0Eh TMR1L Holding Register for the Least Significant Byte of the 16-bit TMR1 Register xxxx xxxx 57, 115

0Fh TMR1H Holding Register for the Most Significant Byte of the 16-bit TMR1 Register xxxx xxxx 57, 115

10h T1CON T1GINV TMR1GE T1CKPS1 T1CKPS0 T1OSCEN T1SYNC TMR1CS TMR1ON 0000 0000 62, 115

11h — Unimplemented — —

12h — Unimplemented — —

13h — Unimplemented — —

14h — Unimplemented — —

15h — Unimplemented — —

16h — Unimplemented — —

17h — Unimplemented — —

18h — Unimplemented — —

19h VRCON CMVREN — VRR FVREN VR3 VR2 VR1 VR0 0-00 0000 76, 116

1Ah CMCON0 CMON COUT CMOE CMPOL — CMR — CMCH 0000 -0-0 72, 116

1Bh — — — — —

1Ch CMCON1 — — — T1ACS CMHYS — T1GSS CMSYNC ---0 0-10 73, 116

1Dh — Unimplemented — —

1Eh — Unimplemented — —

1Fh — Unimplemented — —

Legend: – = Unimplemented locations read as ‘0’, u = unchanged, x = unknown, q = value depends on condition, shaded = unimplemented

1: IRP and RP1 bits are reserved, always maintain these bits clear.

2: Read only register.

2010 Microchip Technology Inc. DS41302D-page 15

PIC12F609/615/617/12HV609/615

TABLE 2-2: PIC12F615/617/HV615 SPECIAL FUNCTION REGISTERS SUMMARY BANK 0

Addr Name Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 Value on

POR, BOR Page

Bank 0

00h INDF Addressing this location uses contents of FSR to address data memory (not a physical register) xxxx xxxx 25, 116

01h TMR0 Timer0 Module’s Register xxxx xxxx 53, 116

02h PCL Program Counter’s (PC) Least Significant Byte 0000 0000 25, 116

03h STATUS IRP(1) RP1(1) RP0 TO PD Z DC C 0001 1xxx 18, 116

04h FSR Indirect Data Memory Address Pointer xxxx xxxx 25, 116

05h GPIO — — GP5 GP4 GP3 GP2 GP1 GP0 --x0 x000 43, 116

06h — Unimplemented — —

07h — Unimplemented — —

08h — Unimplemented — —

09h — Unimplemented — —

0Ah PCLATH — — — Write Buffer for upper 5 bits of Program Counter ---0 0000 25, 116

0Bh INTCON GIE PEIE T0IE INTE GPIE T0IF INTF GPIF 0000 0000 20, 116

0Ch PIR1 — ADIF CCP1IF — CMIF — TMR2IF TMR1IF -00- 0-00 22, 116

0Dh — Unimplemented — —

0Eh TMR1L Holding Register for the Least Significant Byte of the 16-bit TMR1 Register xxxx xxxx 57, 116

0Fh TMR1H Holding Register for the Most Significant Byte of the 16-bit TMR1 Register xxxx xxxx 57, 116

10h T1CON T1GINV TMR1GE T1CKPS1 T1CKPS0 T1OSCEN T1SYNC TMR1CS TMR1ON 0000 0000 62, 116

11h TMR2(3) Timer2 Module Register 0000 0000 65, 116

12h T2CON(3) — TOUTPS3 TOUTPS2 TOUTPS1 TOUTPS0 TMR2ON T2CKPS1 T2CKPS0 -000 0000 66, 116

13h CCPR1L(3) Capture/Compare/PWM Register 1 Low Byte XXXX XXXX 90, 116

14h CCPR1H(3) Capture/Compare/PWM Register 1 High Byte XXXX XXXX 90, 116

15h CCP1CON(3) P1M — DC1B1 DC1B0 CCP1M3 CCP1M2 CCP1M1 CCP1M0 0-00 0000 89, 116

16h PWM1CON(3) PRSEN PDC6 PDC5 PDC4 PDC3 PDC2 PDC1 PDC0 0000 0000 105,

116

17h ECCPAS(3) ECCPASE ECCPAS2 ECCPAS1 ECCPAS0 PSSAC1 PSSAC0 PSSBD1 PSSBD0 0000 0000 102,

116

18h — Unimplemented — —

19h VRCON CMVREN — VRR FVREN VR3 VR2 VR1 VR0 0-00 0000 76, 116

1Ah CMCON0 CMON COUT CMOE CMPOL — CMR — CMCH 0000 -0-0 72, 116

1Bh — — — — —

1Ch CMCON1 — — — T1ACS CMHYS — T1GSS CMSYNC ---0 0-10 73, 116

1Dh — Unimplemented — —

1Eh ADRESH(2, 3) Most Significant 8 bits of the left shifted A/D result or 2 bits of right shifted result xxxx xxxx 85, 116

1Fh ADCON0(3) ADFM VCFG — CHS2 CHS1 CHS0 GO/DONE ADON 00-0 0000 84, 116

Legend: – = Unimplemented locations read as ‘0’, u = unchanged, x = unknown, q = value depends on condition, shaded = unimplemented

Note 1: IRP and RP1 bits are reserved, always maintain these bits clear.

2: Read only register.

3: PIC12F615/617/HV615 only.

PIC12F609/615/617/12HV609/615

DS41302D-page 16 2010 Microchip Technology Inc.

TABLE 2-3: PIC12F609/HV609 SPECIAL FUNCTION REGISTERS SUMMARY BANK 1

Addr Name Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 Value on

POR, BOR Page

Bank 1

80h INDF Addressing this location uses contents of FSR to address data memory (not a physical register) xxxx xxxx 25, 116

81h OPTION_RE

G GPPU INTEDG T0CS T0SE PSA PS2 PS1 PS0 1111 1111 19, 116

82h PCL Program Counter’s (PC) Least Significant Byte 0000 0000 25, 116

83h STATUS IRP(1) RP1(1) RP0 TO PD Z DC C 0001 1xxx 18, 116

84h FSR Indirect Data Memory Address Pointer xxxx xxxx 25, 116

85h TRISIO — — TRISIO5 TRISIO4 TRISIO3(4) TRISIO2 TRISIO1 TRISIO0 --11 1111 44, 116

86h — Unimplemented — —

87h — Unimplemented — —

88h — Unimplemented — —

89h — Unimplemented — —

8Ah PCLATH — — — Write Buffer for upper 5 bits of Program Counter ---0 0000 25, 116

8Bh INTCON GIE PEIE T0IE INTE GPIE T0IF INTF GPIF(3) 0000 0000 20, 116

8Ch PIE1 — — — — CMIE — — TMR1IE ---- 0--0 21, 116

8Dh — Unimplemented — —

8Eh PCON — — — — — — POR BOR ---- --qq 23, 116

8Fh — Unimplemented — —

90h OSCTUNE — — — TUN4 TUN3 TUN2 TUN1 TUN0 ---0 0000 41, 116

91h — Unimplemented — —

92h — Unimplemented — —

93h — Unimplemented — —

94h — Unimplemented — —

95h WPU(2) — — WPU5 WPU4 — WPU2 WPU1 WPU0 --11 -111 46, 116

96h IOC — — IOC5 IOC4 IOC3 IOC2 IOC1 IOC0 --00 0000 46, 116

97h — Unimplemented — —

98h — Unimplemented — —

99h — Unimplemented — —

9Ah — Unimplemented — —

9Bh — Unimplemented — —

9Ch — Unimplemented — —

9Dh — Unimplemented — —

9Eh — Unimplemented — —

9Fh ANSEL — — — — ANS3 — ANS1 ANS0 ---- 1-11 45, 117

Legend: – = Unimplemented locations read as ‘0’, u = unchanged, x = unknown, q = value depends on condition, shaded = unimplemented

Note 1: IRP and RP1 bits are reserved, always maintain these bits clear.

2: GP3 pull-up is enabled when MCLRE is ‘1’ in the Configuration Word register.

3: MCLR and WDT Reset does not affect the previous value data latch. The GPIF bit will clear upon Reset but will set again if the mismatch

exists.

4: TRISIO3 always reads as ‘1’ since it is an input only pin.

2010 Microchip Technology Inc. DS41302D-page 17

PIC12F609/615/617/12HV609/615

TABLE 2-4: PIC12F615/617/HV615 SPECIAL FUNCTION REGISTERS SUMMARY BANK 1

Addr Name Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 Value on

POR, BOR Page

Bank 1

80h INDF Addressing this location uses contents of FSR to address data memory (not a physical register) xxxx xxxx 25, 116

81h OPTION_REG GPPU INTEDG T0CS T0SE PSA PS2 PS1 PS0 1111 1111 19, 116

82h PCL Program Counter’s (PC) Least Significant Byte 0000 0000 25, 116

83h STATUS IRP(1) RP1(1) RP0 TO PD Z DC C 0001 1xxx 18, 116

84h FSR Indirect Data Memory Address Pointer xxxx xxxx 25, 116

85h TRISIO — — TRISIO5 TRISIO4 TRISIO3(4) TRISIO2 TRISIO1 TRISIO0 --11 1111 44, 116

86h — Unimplemented — —

87h — Unimplemented — —

88h — Unimplemented — —

89h — Unimplemented — —

8Ah PCLATH — — — Write Buffer for upper 5 bits of Program Counter ---0 0000 25, 116

8Bh INTCON GIE PEIE T0IE INTE GPIE T0IF INTF GPIF(3) 0000 0000 20, 116

8Ch PIE1 — ADIE CCP1IE — CMIE — TMR2IE TMR1IE -00- 0-00 21, 116

8Dh — Unimplemented — —

8Eh PCON — — — — — — POR BOR ---- --qq 23, 116

8Fh — Unimplemented — —

90h OSCTUNE — — — TUN4 TUN3 TUN2 TUN1 TUN0 ---0 0000 41, 116

91h — Unimplemented — —

92h PR2 Timer2 Module Period Register 1111 1111 65, 116

93h APFCON — — — T1GSEL — — P1BSEL P1ASEL ---0 --00 21, 116

94h — Unimplemented — —

95h WPU(2) — — WPU5 WPU4 — WPU2 WPU1 WPU0 --11 -111 46, 116

96h IOC — — IOC5 IOC4 IOC3 IOC2 IOC1 IOC0 --00 0000 46, 116

97h — Unimplemented — —

98h PMCON1(7) — — — — — WREN WR RD ---- -000 29

99h PMCON2(7) Program Memory Control Register 2 (not a physical register). ---- ---- —

9Ah PMADRL(7) PMADRL7 PMADRL6 PMADRL5 PMADRL4 PMADRL3 PMADRL2 PMADRL1 PMADRL0 0000 0000 28

9Bh PMADRH(7) — — — — — PMADRH2 PMADRH1 PMADRH0 ---- -000 28

9Ch PMDATL(7) PMDATL7 PMDATL6 PMDATL5 PMDATL4 PMDATL3 PMDATL2 PMDATL1 PMDATL0 0000 0000 28

9Dh PMDATH(7) — — Program Memory Data Register High Byte. --00 0000 28

9Eh ADRESL(5, 6) Least Significant 2 bits of the left shifted result or 8 bits of the right shifted result xxxx xxxx 85, 117

9Fh ANSEL — ADCS2 ADCS1 ADCS0 ANS3 ANS2 ANS1 ANS0 -000 1111 45, 117

Legend: – = Unimplemented locations read as ‘0’, u = unchanged, x = unknown, q = value depends on condition, shaded = unimplemented

Note 1: IRP and RP1 bits are reserved, always maintain these bits clear.

2: GP3 pull-up is enabled when MCLRE is ‘1’ in the Configuration Word register.

3: MCLR and WDT Reset does not affect the previous value data latch. The GPIF bit will clear upon Reset but will set again if the mismatch

exists.

4: TRISIO3 always reads as ‘1’ since it is an input only pin.

5: Read only register.

6: PIC12F615/617/HV615 only.

7: PIC12F617 only.

PIC12F609/615/617/12HV609/615

DS41302D-page 18 2010 Microchip Technology Inc.

2.2.2.1 STATUS Register

The STATUS register, shown in Register 2-1, contains:

• the arithmetic status of the ALU

• the Reset status

• the bank select bits for data memory (RAM)

The STATUS register can be the destination for any

instruction, like any other register. If the STATUS

register is the destination for an instruction that affects

the Z, DC or C bits, then the write to these three bits is

disabled. These bits are set or cleared according to the

device logic. Furthermore, the TO and PD bits are not

writable. Therefore, the result of an instruction with the

STATUS register as destination may be different than

intended.

For example, CLRF STATUS, will clear the upper three

bits and set the Z bit. This leaves the STATUS register

as ‘000u u1uu’ (where u = unchanged).

It is recommended, therefore, that only BCF, BSF,

SWAPF and MOVWF instructions are used to alter the

STATUS register, because these instructions do not

affect any Status bits. For other instructions not

affecting any Status bits, see the Section 14.0

“Instruction Set Summary”.

Note 1: Bits IRP and RP1 of the STATUS register

are not used by the PIC12F609/615/617/

12HV609/615 and should be maintained

as clear. Use of these bits is not recommended,

since this may affect upward

compatibility with future products.

2: The C and DC bits operate as a Borrow

and Digit Borrow out bit, respectively, in

subtraction. See the SUBLW and SUBWF

instructions for examples.

REGISTER 2-1: STATUS: STATUS REGISTER

Reserved Reserved R/W-0 R-1 R-1 R/W-x R/W-x R/W-x

IRP RP1 RP0 TO PD Z DC C

bit 7 bit 0

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as ‘0’

-n = Value at POR ‘1’ = Bit is set ‘0’ = Bit is cleared x = Bit is unknown

bit 7 IRP: This bit is reserved and should be maintained as ‘0’

bit 6 RP1: This bit is reserved and should be maintained as ‘0’

bit 5 RP0: Register Bank Select bit (used for direct addressing)

1 = Bank 1 (80h – FFh)

0 = Bank 0 (00h – 7Fh)

bit 4 TO: Time-out bit

1 = After power-up, CLRWDT instruction or SLEEP instruction

0 = A WDT time-out occurred

bit 3 PD: Power-down bit

1 = After power-up or by the CLRWDT instruction

0 = By execution of the SLEEP instruction

bit 2 Z: Zero bit

1 = The result of an arithmetic or logic operation is zero

0 = The result of an arithmetic or logic operation is not zero

bit 1 DC: Digit Carry/Borrow bit (ADDWF, ADDLW,SUBLW,SUBWF instructions), For Borrow, the polarity is

reversed.

1 = A carry-out from the 4th low-order bit of the result occurred

0 = No carry-out from the 4th low-order bit of the result

bit 0 C: Carry/Borrow bit(1) (ADDWF, ADDLW, SUBLW, SUBWF instructions)

1 = A carry-out from the Most Significant bit of the result occurred

0 = No carry-out from the Most Significant bit of the result occurred

Note 1: For Borrow, the polarity is reversed. A subtraction is executed by adding the two’s complement of the

second operand. For rotate (RRF, RLF) instructions, this bit is loaded with either the high-order or low-order

bit of the source register.

2010 Microchip Technology Inc. DS41302D-page 19

PIC12F609/615/617/12HV609/615

2.2.2.2 OPTION Register

The OPTION register is a readable and writable

register, which contains various control bits to

configure:

• Timer0/WDT prescaler

• External GP2/INT interrupt

• Timer0

• Weak pull-ups on GPIO

Note: To achieve a 1:1 prescaler assignment for

Timer0, assign the prescaler to the WDT

by setting PSA bit to ‘1’ of the OPTION

register. See Section 6.1.3 “Software

Programmable Prescaler”.

REGISTER 2-2: OPTION_REG: OPTION REGISTER

R/W-1 R/W-1 R/W-1 R/W-1 R/W-1 R/W-1 R/W-1 R/W-1

GPPU INTEDG T0CS T0SE PSA PS2 PS1 PS0

bit 7 bit 0

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as ‘0’

-n = Value at POR ‘1’ = Bit is set ‘0’ = Bit is cleared x = Bit is unknown

bit 7 GPPU: GPIO Pull-up Enable bit

1 = GPIO pull-ups are disabled

0 = GPIO pull-ups are enabled by individual PORT latch values

bit 6 INTEDG: Interrupt Edge Select bit

1 = Interrupt on rising edge of GP2/INT pin

0 = Interrupt on falling edge of GP2/INT pin

bit 5 T0CS: Timer0 Clock Source Select bit

1 = Transition on GP2/T0CKI pin

0 = Internal instruction cycle clock (FOSC/4)

bit 4 T0SE: Timer0 Source Edge Select bit

1 = Increment on high-to-low transition on GP2/T0CKI pin

0 = Increment on low-to-high transition on GP2/T0CKI pin

bit 3 PSA: Prescaler Assignment bit

1 = Prescaler is assigned to the WDT

0 = Prescaler is assigned to the Timer0 module

bit 2-0 PS<2:0>: Prescaler Rate Select bits

000

001

010

011

100

101

110

111

1 : 2

1 : 4

1 : 8

1 : 16

1 : 32

1 : 64

1 : 128

1 : 256

1 : 1

1 : 2

1 : 4

1 : 8

1 : 16

1 : 32

1 : 64

1 : 128

BIT VALUE TIMER0 RATE WDT RATE

PIC12F609/615/617/12HV609/615

DS41302D-page 20 2010 Microchip Technology Inc.

2.2.2.3 INTCON Register

The INTCON register is a readable and writable

register, which contains the various enable and flag bits

for TMR0 register overflow, GPIO change and external

GP2/INT pin interrupts.

Note: Interrupt flag bits are set when an interrupt

condition occurs, regardless of the state of

its corresponding enable bit or the Global

Enable bit, GIE of the INTCON register.

User software should ensure the

appropriate interrupt flag bits are clear

prior to enabling an interrupt.

REGISTER 2-3: INTCON: INTERRUPT CONTROL REGISTER

R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

GIE PEIE T0IE INTE GPIE T0IF INTF GPIF

bit 7 bit 0

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as ‘0’

-n = Value at POR ‘1’ = Bit is set ‘0’ = Bit is cleared x = Bit is unknown

bit 7 GIE: Global Interrupt Enable bit

1 = Enables all unmasked interrupts

0 = Disables all interrupts

bit 6 PEIE: Peripheral Interrupt Enable bit

1 = Enables all unmasked peripheral interrupts

0 = Disables all peripheral interrupts

bit 5 T0IE: Timer0 Overflow Interrupt Enable bit

1 = Enables the Timer0 interrupt

0 = Disables the Timer0 interrupt

bit 4 INTE: GP2/INT External Interrupt Enable bit

1 = Enables the GP2/INT external interrupt

0 = Disables the GP2/INT external interrupt

bit 3 GPIE: GPIO Change Interrupt Enable bit(1)

1 = Enables the GPIO change interrupt

0 = Disables the GPIO change interrupt

bit 2 T0IF: Timer0 Overflow Interrupt Flag bit(2)

1 = Timer0 register has overflowed (must be cleared in software)

0 = Timer0 register did not overflow

bit 1 INTF: GP2/INT External Interrupt Flag bit

1 = The GP2/INT external interrupt occurred (must be cleared in software)

0 = The GP2/INT external interrupt did not occur

bit 0 GPIF: GPIO Change Interrupt Flag bit

1 = When at least one of the GPIO <5:0> pins changed state (must be cleared in software)

0 = None of the GPIO <5:0> pins have changed state

Note 1: IOC register must also be enabled.

2: T0IF bit is set when TMR0 rolls over. TMR0 is unchanged on Reset and should be initialized before

clearing T0IF bit.

2010 Microchip Technology Inc. DS41302D-page 21

PIC12F609/615/617/12HV609/615

2.2.2.4 PIE1 Register

The PIE1 register contains the Peripheral Interrupt

Enable bits, as shown in Register 2-4.

Note: Bit PEIE of the INTCON register must be

set to enable any peripheral interrupt.

REGISTER 2-4: PIE1: PERIPHERAL INTERRUPT ENABLE REGISTER 1

U-0 R/W-0 R/W-0 U-0 R/W-0 U-0 R/W-0 R/W-0

— ADIE(1) CCP1IE(1) — CMIE — TMR2IE(1) TMR1IE

bit 7 bit 0

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as ‘0’

-n = Value at POR ‘1’ = Bit is set ‘0’ = Bit is cleared x = Bit is unknown

bit 7 Unimplemented: Read as ‘0’

bit 6 ADIE: A/D Converter (ADC) Interrupt Enable bit(1)

1 = Enables the ADC interrupt

0 = Disables the ADC interrupt

bit 5 CCP1IE: CCP1 Interrupt Enable bit(1)

1 = Enables the CCP1 interrupt

0 = Disables the CCP1 interrupt

bit 4 Unimplemented: Read as ‘0’

bit 3 CMIE: Comparator Interrupt Enable bit

1 = Enables the Comparator interrupt

0 = Disables the Comparator interrupt

bit 2 Unimplemented: Read as ‘0’

bit 1 TMR2IE: Timer2 to PR2 Match Interrupt Enable bit(1)

1 = Enables the Timer2 to PR2 match interrupt

0 = Disables the Timer2 to PR2 match interrupt

bit 0 TMR1IE: Timer1 Overflow Interrupt Enable bit

1 = Enables the Timer1 overflow interrupt

0 = Disables the Timer1 overflow interrupt

Note 1: PIC12F615/617/HV615 only. PIC12F609/HV609 unimplemented, read as ‘0’.

PIC12F609/615/617/12HV609/615

DS41302D-page 22 2010 Microchip Technology Inc.

2.2.2.5 PIR1 Register

The PIR1 register contains the Peripheral Interrupt flag

bits, as shown in Register 2-5.

Note: Interrupt flag bits are set when an interrupt

condition occurs, regardless of the state of

its corresponding enable bit or the Global

Enable bit, GIE of the INTCON register.

User software should ensure the

appropriate interrupt flag bits are clear prior

to enabling an interrupt.